技术特征:

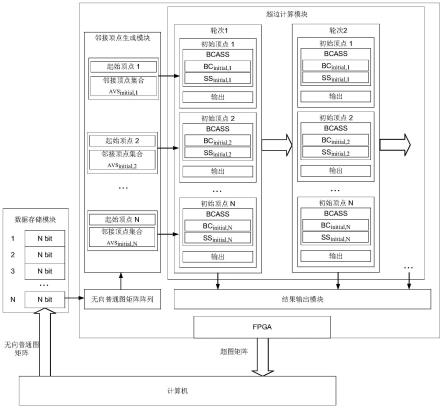

1.一种基于fpga的并行超图构建装置,其特征在于,包括通信连接的计算机系统和fpga;所述计算机系统被配置成用于向fpga发送表示普通图的无向邻接矩阵,接收fpga发送的所有超边,并依据所有超边构建超图;所述fpga被配置成用于接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,依据邻接顶点集合并行构建每个目标顶点对应的超边,并将所有超边传输至计算机系统。2.根据权利要求1所述的基于fpga的并行超图构建装置,其特征在于,所述无向邻接矩阵为n*n大小的二维矩阵,二维矩阵中元素值代表顶点和顶点之间的关联信息,若第i个顶点与第j个顶点关联,则二维矩阵中第i行、第j列的值为1,反之则为0。3.根据权利要求1所述的基于fpga的并行超图构建装置,其特征在于,所述fpga包括数据存储模块、邻接顶点生成模块、超边计算模块、结果输出模块;所述数据存储模块用于对接收的无向邻接矩阵进行存储,包括:为n*n大小的无向邻接矩阵构建一个深度为n、位宽为n的存储空间,将无向邻接矩阵的每一行作为一个二进制数据进行存储,即将每个顶点对应的那一行的二进制数据存储在一个地址空间,并标记该地址空间的地址为对应顶点;所述邻接顶点生成模块用于从数据存储模块中提取存储收据,将每个顶点作为单个目标顶点,并构建每个目标顶点的邻接顶点集合;所述超边计算模块用于根据n个邻接顶点集合并行构建超边;所述结果输出模块用于将构建的所有超边按顺序传输至计算机系统。4.根据权利要求2所述的基于fpga的并行超图构建装置,其特征在于,所述邻接顶点生成模块中,从数据存储模块中提取每个地址空间的地址以及二进制数据,其中,地址存储的顶点作为单个目标顶点,将二进制数据中目标顶点位置的数据值置0后的数据作为目标顶点的邻接顶点集合,邻接顶点集合中值为1对应的顶点为邻接顶点。5.根据权利要求2所述的基于fpga的并行超图构建装置,其特征在于,所述超边计算模块中,根据n个邻接顶点集合进行首轮的并行超边构建,包括:以每个目标顶点为起始顶点,执行以下超边构建步骤:首先,将起始顶点的邻接顶点集合记为avs

initial,j

,并为目标顶点初始化超边集合bc

initial,j

和备选集合ss

initial,j

,其中,bc

initial,j

和ss

initial,j

的位宽与avs

initial,j

相等,且所有数值为0;然后,遍历avs

initial,j

中每个邻接顶点p

i

,并执行:获取邻接顶点p

i

的邻接顶点集合avs

adjoin,i

,将avs

adjoin,i

与当前bc

initialt,j

进行与运算,当与运算结果与bc

initial,j

相等,则将bc

initial,j

中邻接顶点p

i

的对应位置赋值为1,以更新bc

initial,j

,否则将ss

initial,j

中邻接顶点p

i

的对应位置赋值为1,以更新ss

initial,j

;在遍历完avs

initial,j

中所有邻接顶点,将最后更新的bc

initial,j

作为目标顶点的超边。6.根据权利要求5所述的基于fpga的并行超图构建装置,其特征在于,所述超边计算模块中,在第k轮并行超边构建结束后,当ss

initial,j

中存在数值1时,进行第k 1轮的并行超边构建,包括:针对每个第k轮的avs

initial,j

,将第k轮的avs

initial,j

对应的初始顶点从无向邻接矩阵中去除,同时更新初始顶点对应的邻接顶点p

i

的邻接顶点集合avs

adjoin,i

,以更新后邻

接顶点集合avs

adjoin,i

中每个邻接顶点p

i

作为第k 1轮的初始顶点,执行第k 1轮的超边构建步骤。7.根据权利要求3所述的基于fpga的并行超图构建装置,其特征在于,所述结果输出模块中,将并行计算的所有超边按照轮次顺序将每轮次构建的超边进行输出,在每个轮次内,按照初始顶点的序号顺序输出。8.一种基于fpga的并行超图构建方法,其特征在于,所述并行超图构建方法采用权利要求1-7任一项所述的并行超图构建装置,包括以下步骤:所述计算机系统向fpga发送表示普通图的无向邻接矩阵;所述fpga接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,并行依据邻接顶点集合构建每个目标顶点对应的超边,并将所有超边传输至计算机系统;所述计算机系统接收fpga发送的所有超边,并依据所有超边构建超图。

技术总结

本发明公开了一种基于FPGA的并行超图构建方法和装置,装置包括通信连接的计算机系统和FPGA;计算机系统被配置成用于向FPGA发送表示普通图的无向邻接矩阵,接收FPGA发送的所有超边并依据所有超边构建超图;FPGA被配置成用于接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,并行依据邻接顶点集合构建每个目标顶点对应的超边,并将所有超边传输至计算机系统。该装置和方法通过FPGA超边的并行计算,将超边构建的时间复杂度转化到空间复杂度来降低运算时间开销,进而实现精确超图的快速构建。进而实现精确超图的快速构建。进而实现精确超图的快速构建。

技术研发人员:周凡 高翔 刘雪松 田翔

受保护的技术使用者:浙江大学滨江研究院

技术研发日:2022.07.19

技术公布日:2022/11/22

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。