1.本发明属于数据存储技术领域,具体涉及一种线性采集存储网络综合设备及存储架构。

背景技术:

2.随着舰艇网络一体化发展需求、各装备间的信息交换与信息共享需求越来越突出,其网络信息量也急剧增大,给10ge/40ge高速网络数据采集分析存储设备提出更高的带宽和分析能力要求;同时还面临很多种类型数据高低速混合实时存储,实现部分类型数据内容实时解析关联管理等应用场景,给高速网络数据采集分析存储设备带来更高难度挑战。

3.现有的高速网络数据采集分析存储技术架构为基于cpu采集存储架构。用户数据由前端采集模块采集后先传输至记录控制模块,再由记录控制模块传输至后端存储体阵列。然而在实际应用中该架构存在如下问题:

4.一、精度问题:该存储架构中数据包先被缓存在网卡,再聚合一定数据包通过dma方式把数据搬运cpu的ddr,数据包到达时间戳是在内核添加,其时间信息存在一定延迟;同时在cpu调度实时性问题,不能保证准确调度;即整体采集网络数据包时间戳精度不高。

5.二、性能问题:网络高速采集时,受限于网络协议栈实现,需要把数据从内核拷贝到应用;数据存储时,需要把数据从应用层拷贝到内核层,两次数据拷贝,特别是在高速采集存储时,cpu能力、ddr主存访问带宽均可能会成为整个数据路径上的性能瓶颈,会出现丢包情况。高速记录系统因功耗及应用环境特殊,多采用嵌入式工控cpu平台进行采集存储,其处理能力及内存访问带宽均相对有限,导致现有采集记录技术很难适应所有的高速数据记录场景。

6.三、扩展问题:设备扩展性差,当记录控制模块的cpu支撑不业务时,不能通过快速增加记录控制模块来解决。

技术实现要素:

7.本发明的目的之一在于提供一种线性采集存储网络综合设备,提供一种集高速采集存储、负载均衡、实时处理等于一体的网络综合产品。

8.为实现上述目的,本发明所采取的技术方案为:

9.一种线性采集存储网络综合设备,所述线性采集存储网络综合设备包括前端采集模块、记录控制模块和后端存储体阵列,其中:

10.所述前端采集模块,用于解析所采集的数据包,根据解析结果以及配置规则对数据包执行过滤操作、转发操作和/或存储操作,其中:

11.所述前端采集模块执行过滤操作时,执行如下步骤:基于由解析结果以及配置规则确定的过滤模式对数据包进行过滤,若当前数据包被过滤丢弃,则结束本次操作等待下一数据包的到来,若当前数据包未被过滤丢弃,则执行转发操作和/或存储操作;

12.所述前端采集模块执行转发操作时,执行如下步骤:将数据包中非高速数据以实时透传方式转发至所述记录控制模块,由记录控制模块传输至所述后端存储体阵列落盘存储;

13.所述前端采集模块执行存储操作时,执行如下步骤:将数据包中的高速数据进行缓存,在缓存的高速数据达到预设数据量时通知所述记录控制模块,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储。

14.以下还提供了若干可选方式,但并不作为对上述总体方案的额外限定,仅仅是进一步的增补或优选,在没有技术或逻辑矛盾的前提下,各可选方式可单独针对上述总体方案进行组合,还可以是多个可选方式之间进行组合。

15.作为优选,所述配置规则包括根据数据包的五元组信息预设的过滤模式,所述过滤模式包括非白即黑和非黑即白,所述五元组信息包括源ip、目标ip、源端口、目标端口和协议类型。

16.作为优选,所述前端采集模块包括fpga和ddr缓存单元,所述前端采集模块,在缓存的高速数据达到预设数据量时通知所述记录控制模块,执行如下操作:

17.向所述记录控制模块产生中断,并将高速数据在ddr缓存单元内首地址、数据有效长度和逻辑通道id发送至所述记录控制模块,所述数据包中的高速数据存储在ddr缓存单元内实现缓存。

18.作为优选,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储,执行如下操作:

19.所述后端存储体阵列接收记录控制模块发送的高速数据在ddr缓存单元内首地址、数据有效长度和管理逻辑地址,启动dma,根据高速数据在ddr缓存单元内首地址和数据有效长度,将ddr缓存单元中的高速数据搬移到后端存储体阵列中管理逻辑地址对应的块地址上,完成数据落盘,所述管理逻辑地址由记录控制模块根据逻辑通道id获得。

20.本发明提供的线性采集存储网络综合设备,新增一条网络路径,从前端采集模块到记录控制模块;在新硬件框架基础上,修改用户数据传输路径,数据从前端采集模块直接到后端存储体阵列,记录控制模块只负责调度和管理,规避性能瓶颈,从而达到高速记录的目的。通过新增网络路径,前端采集模块把非高速采集的数据和命令,实时透传转发给记录控制模块,由记录控制模块的操作系统来完成网络协议栈处理。

21.本发明的目的之二在于提供一种存储架构,具有灵活,流程效率高、可扩展性强等特点。

22.为实现上述目的,本发明所采取的技术方案为:

23.一种存储架构,所述存储架构包括多个处于集群工作模式的线性采集存储网络综合设备,所述线性采集存储网络综合设备包括前端采集模块、记录控制模块和后端存储体阵列,其中:

24.所述前端采集模块,用于解析所采集的数据包,根据解析结果以及配置规则对数据包执行过滤操作、转发操作和/或存储操作,其中:

25.所述前端采集模块执行过滤操作时,执行如下步骤:基于由解析结果以及配置规则确定的过滤模式对数据包进行过滤,若当前数据包被过滤丢弃,则结束本次操作等待下一数据包的到来,若当前数据包未被过滤丢弃,则执行转发操作和/或存储操作;

26.所述前端采集模块执行转发操作时,执行如下步骤:将数据包中非高速数据以实时透传方式转发至所述记录控制模块,由记录控制模块传输至所述后端存储体阵列落盘存储;同时基于由解析结果以及配置规则确定的转发模式将非高速数据和/或高速数据转发至并行布置的线性采集存储网络综合设备的前端采集模块用于存储;

27.所述前端采集模块执行存储操作时,执行如下步骤:将数据包中的高速数据进行缓存,在缓存的高速数据达到预设数据量时通知所述记录控制模块,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储。

28.作为优选,所述配置规则包括根据数据包的五元组信息预设的过滤模式,所述过滤模式包括非白即黑和非黑即白,所述五元组信息包括源ip、目标ip、源端口、目标端口和协议类型;

29.所述配置规则还包括根据数据包的五元组信息预设的转发模式,所述转发模式包括轮询和动态负载调整。

30.作为优选,所述前端采集模块包括fpga和ddr缓存单元,所述前端采集模块,在缓存的高速数据达到预设数据量时通知所述记录控制模块,执行如下操作:

31.向所述记录控制模块产生中断,并将高速数据在ddr缓存单元内首地址、数据有效长度和逻辑通道id发送至所述记录控制模块,所述数据包中的高速数据存储在ddr缓存单元内实现缓存。

32.作为优选,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储,执行如下操作:

33.所述后端存储体阵列接收记录控制模块发送的高速数据在ddr缓存单元内首地址、数据有效长度和管理逻辑地址,启动dma,根据高速数据在ddr缓存单元内首地址和数据有效长度,将ddr缓存单元中的高速数据搬移到后端存储体阵列中管理逻辑地址对应的块地址上,完成数据落盘,所述管理逻辑地址由记录控制模块根据逻辑通道id获得。

34.本发明提供的存储架构,通过重定向文件存取dma地址的方式,扩展了直接数据记录通道,以适应高速记录和高精度时间戳节拍控制应用场景;按照配置规则,前端采集模块实时转发实现了负载均衡能力,达到集群模式,可实现数据内容实时解析和处理,达到数据精细化管理;同时在最前端执行实时过滤,实现防火墙效果,保护设备安全。

附图说明

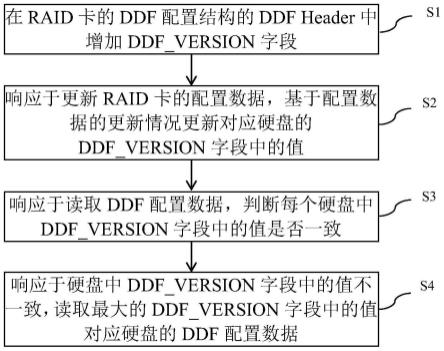

35.图1为本发明的线性采集存储网络综合设备的结构示意图;

36.图2为本发明的存储架构的结构示意图。

具体实施方式

37.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具

体的实施例的目的,不是在于限制本发明。

39.为了克服现有技术中高速网络数据采集分析存储技术架构存在的精度、性能、扩展方面的问题,在一个实施例中,提出一种线性采集存储网络综合设备。

40.如图1所示,本实施例的线性采集存储网络综合设备包括前端采集模块、记录控制模块和后端存储体阵列。其中前端采集装置可以是fpga及相应的内存ddr(称为ddr缓存单元)进行外部数据采集缓存,例如摄像头设备。读写控制装置通常为带网卡的中央处理器cpu及相应的主存ddr(称为系统ddr主存单元),例如一台计算机设备。后端存储体可以为nvme固态盘,进行读取数据并缓存,例如录像机设备。

41.本实施例中前端采集模块和后端存储体阵列之间、记录控制模块和后端存储体阵列之间均基于数据交换模块进行数据交互,前端采集模块和记录控制模块之间直接通过cpu的网卡进行交互。其中数据交换模块为pcie switch,提供高速数据通道。

42.本实施例中,所述前端采集模块,用于解析所采集的数据包,根据解析结果以及配置规则对数据包执行过滤操作、转发操作和/或存储操作。

43.本实施例中配置规则包括根据数据包的五元组信息预设的过滤模式,过滤模式包括非白即黑方式和非黑即白方式,五元组信息包括源ip、目标ip、源端口、目标端口和协议类型。本实施例事先在配置规则中根据五元组信息为每一路数据定制各自的过滤模式。

44.根据应用场景,设置以下两种工作模式:

45.1)非白即黑方式:只配置白名单,白名单中的数据包按照配置规则存储或转发,而没有配置名单,默认为丢弃;设备默认工作模式为非白即黑模式,在该工作模式下,fpga作为设备防火墙,起到隔离作用,保护设备安全。

46.2)非黑即白方式:只配置黑名单,即被过滤名单,黑名单中的数据包丢弃,其他数据包按照配置规则存储或转发;如果没有配置,默认实时透传方式转发。

47.本实施例中前端采集模块(具体可以是有fpga执行)执行数据过滤时,执行如下步骤:基于由解析结果以及配置规则确定的过滤模式对数据包进行过滤,若当前数据包被过滤丢弃,则结束本次操作等待下一数据包的到来,若当前数据包未被过滤丢弃,则执行转发操作和/或存储操作。

48.针对经过数据过滤保留的数据包,fpga针对其中的非高速数据和命令执行数据转发,针对高速数据执行数据存储。

49.本实施例的前端采集模块执行转发操作时,执行如下步骤:将数据包中非高速数据以实时透传方式转发至记录控制模块,由记录控制模块传输至后端存储体阵列落盘存储。容易理解的是,前端采集模块转发至记录控制模块的除了非高速数据之外,还可以包括各类命令。

50.本实施例的前端采集模块执行存储操作时,执行如下步骤:将数据包中的高速数据进行缓存,在缓存的高速数据达到预设数据量时通知所述记录控制模块,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储。

51.本实施例的线性采集存储网络综合设备相较于传统存储技术架构新增一条网络路径,从前端采集模块到记录控制模块,用于传输非高速数据;根据配置分配规则,前端采集模块可采集并直接存储数据到后端存储体阵列从而实现数据存储路径不经过记录控制

模块,通过修改数据传输路径,记录控制模块只负责调度和管理,规避性能瓶颈,从而达到高速记录的目的。

52.需要说明的是,本实施例中的过滤操作、转发操作和存储操作可以是全部执行,也可以是根据实际应用场景选择其中的部分操作执行,例如不执行转发操作,整个设备不对非高速数据进行处理等等。

53.为了便于描述,本实施例以前端采集模块包括fpga和ddr缓存单元为例进行说明。

54.本实施例中fpga执行数据存储时,将采集的高速数据存储在ddr缓存单元中,并在检测到高速数据的数据量达到可搬运数据量时,向录控制模块产生中断,并向记录控制模块发送高速数据在ddr缓存单元内首地址、数据有效长度和逻辑通道id。

55.记录控制模块响应于fpga产生的中断,接收高速数据在ddr缓存单元内首地址、数据有效长度和逻辑通道id,根据逻辑通道id得到管理逻辑地址,并向后端存储体阵列提交io命令,将高速数据在ddr缓存单元内首地址、数据有效长度和管理逻辑地址传输至后端存储体阵列。

56.后端存储体阵列接收到记录控制模块提交的io命令后,根据接收的管理逻辑地址转换得到对应的物理存储地址,并启动dma,根据高速数据在ddr缓存单元内首地址和数据有效长度,通过pcie switch总线寻址方式,将ddr缓存单元中的待存储数据搬移到后端存储体阵列对应的物理存储地址上,完成数据存储落盘。

57.在传统的技术方案中,前端采集装置采集的数据在缓存后,需要先被读取到记录控制模块的内存中,然后再被写入到后端存储体阵列。本技术技术方案将前端采集装置采集的数据,从前端采集装置的缓存中直接落盘到后端存储体阵列,降低读写控制装置中系统的性能和带宽负担。

58.在传统的技术方案中,后端存储体阵列通过启动dma从记录控制模块读取数据,其中dma描述包含三个要素:数据在系统内存中位置的总线地址,数据的长度,数据将要写入的存储体起始块编号。

59.现有架构中记录控制模块由安装在cpu中的软件程序实现的应用软件,以及由记录控制模块操作系统中的内核程序提供的文件系统和存储体驱动构成。通用文件系统数据标准落盘,dma描述符会指示文件数据在系统主存内,是由存储体的dma引擎从系统ddr主存单元搬取,而本技术将高速数据在ddr缓存单元内首地址初始化到dma描述符中,则存储体可以不经过记录控制模块,直接将前端采集模块中的高速数据写入到盘内。

60.本实施例实现上述功能时,在现有的文件系统和存储体驱动上进行扩展,保持原有的文件系统和存储体驱动所有特性不变,额外定义文件扩展专用接口供应用软件调用。具体扩展操作如下:

61.a、新增文件系统的专用接口:该专用接口用于应用软件调用以将高速数据在ddr缓存单元内首地址、数据有效长度传入文件系统。其中新增的专用接口可以使用ioctl系统调用实现,即新增自定义ioctl命令,将参数由应用层传递到操作系统内核中的文件系统层。

62.b、文件系统扩展功能:在文件系统新增文件ioctl命令响应函数实现,响应函数实现的具体内容包括:

63.接收到文件系统的专用接口提供的数据有效长度,按读写大小调用文件系统的常

规块分配函数分配逻辑块;结合高速数据在ddr缓存单元内首地址,创建一个特殊的bio(block input output,块读写);为特殊的bio打上一个自定义的标签,并按常规路径提交到块设备层。

64.c、存储体驱动扩展功能:接收到上层提供的bio,处理时新增标签判断逻辑,若为常规bio,则保留原有的处理方式,即进行虚拟地址转换成总线地址转换,若为带自定义标签的特殊bio,则跳过常规的地址转换步骤,直接将上层传递下来的高速数据在ddr缓存单元内首地址设置到dma描述符中。

65.即本实施例中应用软件调用文件系统的专用接口,将参数传递给文件系统,文件系统进行响应,创建特殊的块读写,并将特殊的块读写提交到存储体驱动,存储体驱动接收到特殊的块读写后,将参数中的高速数据在ddr缓存单元内首地址和数据有效长度设置到dma描述符中,封装为读写命令,提交给存储体。

66.容易理解的是,本实施例通过记录控制模块中的应用软件、文件系统和存储体驱动将fpga发送的高速数据在ddr缓存单元内首地址和数据有效长度直接传输至后端存储体阵列,由后端存储体阵列直接根据数据从fpga内获取数据落盘。关于记录控制模块根据逻辑通道获取管理逻辑地址,后端存储体阵列根据管理逻辑地址转换得到对应的物理存储地址等逻辑均为现有常规处理逻辑,本实施例中不进行赘述。

67.基于记录控制模块中的应用软件、文件系统和存储体驱动,线性采集存储网络综合设备对于高速数据进行存储的一个具体实例如下:

68.1)fpga实时计算数据量达到可搬运时,以中断方式通知应用软件,向应用软件传递参数包括:高速数据在ddr缓存单元内首地址、数据有效长度和和逻辑通道id;

69.2)应用软件先解析参数,再根据逻辑通道id找到通道对应文件,分配将要写入的存储体起始块编号,得到管理逻辑地址,最后调用文件系统的专用接口,向文件系统传递高速数据在ddr缓存单元内首地址和数据有效长度;

70.3)文件系统根据管理逻辑地址,形成一次写操作,由存储体驱动向存储体提交io命令,并传输参数包括高速数据在ddr缓存单元内首地址和管理逻辑地址;

71.4)存储体接收io命令,启动dma,通过pcie switch总线寻址方式将ddr缓存单元内数据搬移到对应的块地址上。

72.5)应用软件建立索引信息,并实时写入存储体,通过系统ddr主存单元到存储体的数据流向使得索引信息和数据保持相一致。

73.本实施例现有采集存储架构的数据传输路径,把原来从ddr缓存单元的网络数据先搬运到系统ddr主存单元,再从系统ddr主存单元搬运到存储体的数据流程,修改成从ddr缓存单元的网络数据直接搬运到存储体的数据流程,实现了数据的高速采集记录。

74.本实施例在传统的采集存储架构上,新增一条网络路径,fpga把非高速采集的数据和命令,实时透传转发给cpu,由cpu的操作系统来完成网络协议栈处理,应用软件只感知用户数据,不需要关注协议栈,降低软件复杂度;同时在硬件框架基础上,通过对文件系统、存储体驱动进行扩展,改变记录控制模块的数据传输路径,数据从fpga直接到存储体,cpu只负责调度和管理,规避性能瓶颈,从而达到高速记录的目的。

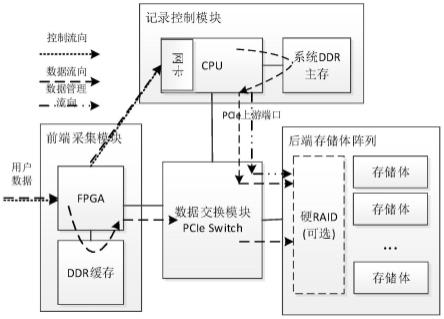

75.在另一个实施例中,如图2所示,还提供一种存储架构,该存储架构包括多个处于集群工作模式的线性采集存储网络综合设备,所述线性采集存储网络综合设备包括前端采

集模块、记录控制模块和后端存储体阵列,其中:

76.所述前端采集模块,用于解析所采集的数据包,根据解析结果以及配置规则对数据包执行过滤操作、转发操作和/或存储操作,其中:

77.所述前端采集模块执行过滤操作时,执行如下步骤:基于由解析结果以及配置规则确定的过滤模式对数据包进行过滤,若当前数据包被过滤丢弃,则结束本次操作等待下一数据包的到来,若当前数据包未被过滤丢弃,则执行转发操作和/或存储操作;

78.所述前端采集模块执行转发操作时,执行如下步骤:将数据包中非高速数据以实时透传方式转发至所述记录控制模块,由记录控制模块传输至所述后端存储体阵列落盘存储;同时基于由解析结果以及配置规则确定的转发模式将非高速数据和/或高速数据转发至并行布置的线性采集存储网络综合设备的前端采集模块;

79.所述前端采集模块执行存储操作时,执行如下步骤:将数据包中的高速数据进行缓存,在缓存的高速数据达到预设数据量时通知所述记录控制模块,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储。

80.在一个具体实施例中,所述配置规则包括根据数据包的五元组信息预设的过滤模式,所述过滤模式包括非白即黑和非黑即白,所述五元组信息包括源ip、目标ip、源端口、目标端口和协议类型;

81.所述配置规则还包括根据数据包的五元组信息预设的转发模式,所述转发模式包括轮询和动态负载调整。

82.在一个具体实施例中,所述前端采集模块包括fpga和ddr缓存单元,所述前端采集模块,在缓存的高速数据达到预设数据量时通知所述记录控制模块,执行如下操作:

83.向所述记录控制模块产生中断,并将高速数据在ddr缓存单元内首地址、数据有效长度和逻辑通道id发送至所述记录控制模块,所述数据包中的高速数据存储在ddr缓存单元内实现缓存。

84.在一个具体实施例中,所述后端存储体阵列在所述记录控制模块的控制下直接从所述前端采集模块读取缓存的高速数据落盘存储,执行如下操作:

85.所述后端存储体阵列接收记录控制模块发送的高速数据在ddr缓存单元内首地址、数据有效长度和管理逻辑地址,启动dma,根据高速数据在ddr缓存单元内首地址和数据有效长度,将ddr缓存单元中的高速数据搬移到后端存储体阵列中管理逻辑地址对应的块地址上,完成数据落盘,所述管理逻辑地址由记录控制模块根据逻辑通道id获得。

86.关于存储架构的具体限定可参见所述线性采集存储网络综合设备的限定,这里不进行赘述。

87.存储架构中根据配置规则,fpga把网络数据负载分担分发到其他设备,起到负载分担作用。按照目前fpga资源,可以做到2个网口进,根据流量配置分配规则分担到16个网口出去,从而实现了横向扩展。

88.由于本实施例存储架构中包括多个处于集群工作模式的线性采集存储网络综合设备,即本实施例存储架构实现集群工作模式,因此本实施例中位于存储架构中的线性采集存储网络综合设备的转发模式还包括向平行设置的线性采集存储网络综合设备进行数据转发,以实现负载均衡达到集群工作模式,类似于网络负载均衡器(f5)。

89.根据应用场景,设置以下两种工作模式:

90.1)轮询:根据设备源ip和端口,轮询到不同设备上,需保证同一业务在同一台设备处理。

91.2)动态负载:根据后端设备(fpga或cpu)实时负载情况,应用软件可动态修改fpga转发规则,实现动态负载均衡;同时根据设备工作状态,应用软件动态修改fpga转发规则,实现设备动态加入或离开,从而达到动态扩展,即集群工作模式。

92.当一台设备cpu无法实时处理高速数据采集、解析、存储整个工作流程时,可通过动态扩展设备来实现流量负载,达到多个设备并行处理,即集群模式,从而实现对数据内容帧级别管理,即数据管理精细化;根据数据特性分类处理,高速数据采用直接存储,中低速数据采用实时转发(透传)本设备cpu,实现中低速实数据内容级别管理存储。

93.本实施例的存储架构,以简单的方式实现高速存储,降低高速存储对高性能cpu依赖;同时保留文件系统的原有特性,高速存储形成的数据文件,可通过标准文件访问接口访问,便于存储管理。根据不同应用场景:高速数据内容级管理,根据配置转发规则,实现多台设备并行处理达到动态负载均衡的集群工作模式;高速数据只采集存储不做实时分析而做事后分析,中低速数据内容级数据存储管理通过实时转发按照配置规则;fpga在最前端实现实时过滤工作,达到设备防火墙效果,保证产品安全。上述三种优势可同时生效,得到具有灵活,流程效率高、可扩展性强等特点的存储架构。

94.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

95.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明的保护范围应以所附权利要求为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。