1.本发明涉及芯片仿真技术领域,具体而言,涉及一种转换二进制文件产生离散已加载仿真内存模型的方法,更具体地涉及一种转换摩托罗拉srec格式二进制文件产生离散已加载仿真内存模型的方法。

背景技术:

2.cpu芯片的系统程序需要提供从rom加载到ram的自加载流程,该加载过程在芯片仿真中可以通过分析可执行文件符号表直接加载到内存模型中来省略,来加速芯片仿真过程。

3.芯片的系统测试用例一般表现为二进制程序,按规范链接为.text/.rodata/.data/.bss段。其中,.text段放置代码,.rodata段放置只读数据,.data段放置已初始化数据,.bss段放置未初始化数据。由于芯片的系统程序中不包括之前执行的其他程序,因此需要提供自加载功能,将程序按照链接后的段空间加载到对应的cpu地址空间中。一般来说,执行系统程序需要只读的rom和可读写的ram。在非仿真的芯片真实运行环境中,系统程序是默认预置在rom中(因为ram是易失性存储介质,因而不可能提前放在ram中),系统程序的自加载过程会将其可读写段(.data/.bss段)加载到ram中,有时候甚至会将其只读段(.text/.rodata段)也复制到ram中执行。由于加载过程是一个将数据从rom复制到ram的过程,其消耗的时间较长,因此在芯片仿真时会采用加速的方法以去除这个过程。现有芯片仿真一般采用以下几种方案:

4.1)利用ram模型,提前将所有数据转换成芯片仿真可以使用的十六进制hex格式文件,通过rtl(register transfer level,寄存器转换级电路)的readmemh函数后门将这种hex文件(又称为vhx十六进制格式文件,参看下文vhx格式说明)加载到ram模型中,仿真时通过提供ram启动模式来执行已经存放在ram模型中的测试程序。此方案由于进行了提前加载,所以系统程序执行时可以跳过自加载过程。但此方案的缺点是提前加载的文件中.text/.rodata段也会占用ram空间,而对于某些芯片极限设计ram过小的场景的仿真,该方法无法使用。此外,该方法中真实场景的程序实际上是被修改了的,rom里的执行程序的功能是无法在仿真时被测试到,存在一定的漏测风险。

5.其中,vhx是verilog专用的仿真内存模型文件,可以被verilog系统函数$readmemx加载到一个verilog内存模型中,请参考以下vhx格式文件的例子:

[0006][0007][0008]

和普通的hex文件相比,vhx格式文件多了“@偏移”的标记,指示后续的一段十六进制表达的数据位于内存模型的哪个偏移地址,因此用多个“@偏移”可以表达离散的数据内容。

[0009]

2)尽可能地不使用数据段,仅在寄存器内和在栈上操作数据。此方案的缺点是测试用例执行的不是真实场景的程序,且无法编写强大功能的测试用例进行仿真,由于执行的程序本身只使用了cpu芯片的一部分功能,很多时候cpu芯片的bug并无法在仿真时完全检测到,存在遗漏bug的风险。

[0010]

因此,业内需要一种能够在仿真时既省略了加载过程又节省了ram开销,同时还能

使用真实场景的程序进行测试的方法。

技术实现要素:

[0011]

为了解决上述问题,本发明提供一种转换二进制文件产生离散已加载仿真内存模型的方法,通过一种离散后门加载方案,即离线实现加载器,将二进制程序拆分到rom模型和ram模型中,不需要分析符号表就能直接加载到内存模型中,以实现在仿真时既省略了加载过程,又节省了ram开销,能够使用真实场景的程序进行仿真测试。

[0012]

为达到上述目的,本发明提供了一种转换二进制文件产生离散已加载仿真内存模型的方法,其通过将srec文件信息提取出来并转换成多个vhx内存模型的hex文件,具体包括:

[0013]

步骤s1:将系统程序的可执行文件链接为已加载的形式;

[0014]

步骤s2:将已加载形式的可执行文件转换为srec十六进制格式文件;

[0015]

步骤s3:解析srec十六进制格式文件,提取其中每个段信息中的类型、基址与长度,并将srec十六进制格式文件转换为vhx内存的十六进制格式文件;

[0016]

步骤s4:在芯片仿真时,通过脚本分析vhx内存的十六进制格式文件,并根据不同段加载地址的不同将vhx内存的十六进制格式文件拆分并加载到不同的内存仿真模型文件中。

[0017]

在本发明一实施例中,其中,步骤s1的链接方法为对链接脚本进行处理,具体为:

[0018]

通过编辑链接器脚本,使链接地址与加载地址相同。

[0019]

在本发明一实施例中,其中,步骤s2是通过标准二进制工具进行格式转换,标准二进制工具包括objcopy。

[0020]

在本发明一实施例中,其中,步骤s3中进行解析的工具为srec解析器。

[0021]

在本发明一实施例中,其中,步骤s3中的每个段包括:.text段、.rodata段、.data段及.bss段。

[0022]

在本发明一实施例中,其中,步骤s4加载到不同的内存模型文件的过程具体为:

[0023]

将拆分后的vhx内存的十六进制格式文件通过后门加载到不同的内存仿真模型中,所述后门包括rtl的readmemh函数。

[0024]

本发明提供的转换二进制文件产生离散已加载仿真内存模型的方法,与现有技术相比,不需要分析符号表就能直接加载到内存模型中,且在仿真时既省略了加载过程,又节省了ram开销,还能够使用真实场景的程序进行仿真测试,降低了由于部分程序在仿真时检测不到而产生的风险。

附图说明

[0025]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0026]

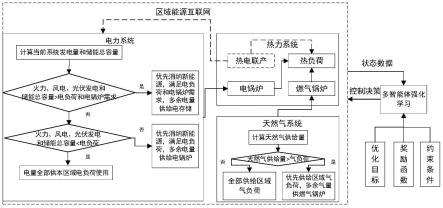

图1为本发明一实施例的流程图。

具体实施方式

[0027]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有付出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0028]

通常情况下,操作二进制文件转换成hex文件是链接器和加载器的标准功能,此处不再赘述,但是普通的十六进制hex只会将二进制本身转换成连续的十六进制数据内容,里面既没有地址信息,也无法区分程序的段。而srec格式是一种摩托罗拉公司创建的hex格式,和普通的二进制格式不同,它用于将程序本身转换为离散的十六进制格式,变成一段一段的十六进制,能够包含起始地址和大小信息,摩托罗拉原意是使用该格式可以减小二进制的大小,当链接地址不连续时,段与段之间的填充不用生成到十六进制文件中,因此srec格式的hex文件中可以带有段的基址和大小信息,本实施例所采用的是摩托罗拉srec十六进制格式。但是由于srec格式的地址信息是链接地址并不是加载地址,即它是程序存放在存储介质(例如rom)中的偏移,而不是最后cpu使用的地址,因此本实施例是将srec格式文件信息提取出来,并转换成多个vhx内存模型hex文件的工具,以实现转换二进制文件产生离散已加载仿真内存模型。图1为本发明一实施例的流程图,如图1所示,本实施例提供一种转换二进制文件产生离散已加载仿真内存模型的方法,其通过将srec文件信息提取出来并转换成多个vhx内存模型hex文件(面向verilog hdl内存模型的hex文件),具体包括:

[0029]

步骤s1:将系统程序的可执行文件链接为已加载的形式,以实现离线加载;

[0030]

在本实施例中,其中,步骤s1的链接方法为对链接脚本进行处理,具体为:

[0031]

通过编辑链接器脚本(例如lds脚本),使链接地址与加载地址相同。

[0032]

步骤s2:将已加载形式的可执行文件转换为摩托罗拉srec十六进制格式文件;

[0033]

在本实施例中,其中,步骤s2是通过标准二进制工具进行格式转换,标准二进制工具包括objcopy(gnu实用工具程序)。

[0034]

步骤s3:解析srec十六进制格式文件,提取其中每个段信息中的类型、基址与长度,并将srec十六进制格式文件转换为vhx内存的十六进制格式文件;

[0035]

在本实施例中,其中,步骤s3中进行解析的工具为srec解析器。

[0036]

在本实施例中,其中,步骤s3中的每个段包括:.text段、.rodata段、.data段及.bss段。

[0037]

由于此时的可执行文件是已加载形式,vhx格式是标准格式的,已经生成vhx内存的十六进制格式后,可以调用rtl的readmemh函数进行自动加载,因此,链接地址的基址和最终符号表的加载地址一致,不需要分析符号表就能直接加载到内存模型中,此时可以看到生成的vhx内存的十六进制格式文件是离散形式,不同的段前面可设置有“@加载地址”标记。

[0038]

步骤s4:在芯片仿真时,通过脚本分析vhx内存的十六进制格式文件,并根据不同段加载地址的不同将vhx内存的十六进制格式文件拆分并加载到不同的内存仿真模型文件(hex文件)中。

[0039]

在本实施例中,其中,步骤s4加载到不同的内存模型文件的过程具体为:

[0040]

将拆分后的vhx内存的十六进制格式文件通过后门加载到不同的内存仿真模型

中,所述后门包括rtl的readmemh函数。

[0041]

此时,.text段和.rodata段能够留在rom内存模型中,而.data段和.bss段能够留在ram内存模型中。

[0042]

本发明提供的转换二进制文件产生离散已加载仿真内存模型的方法,与现有技术相比,不需要分析符号表就能直接加载到内存模型中,且在仿真时既省略了加载过程,又节省了ram开销,还能够使用真实场景的程序进行仿真测试,降低了由于部分程序在仿真时检测不到而产生的风险。

[0043]

本领域普通技术人员可以理解:附图只是一个实施例的示意图,附图中的模块或流程并不一定是实施本发明所必须的。

[0044]

本领域普通技术人员可以理解:实施例中的装置中的模块可以按照实施例描述分布于实施例的装置中,也可以进行相应变化位于不同于本实施例的一个或多个装置中。上述实施例的模块可以合并为一个模块,也可以进一步拆分成多个子模块。

[0045]

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。