一种具有过冲抑制和自适应补偿的多种ldo输出电压电路

技术领域

1.本实用新型涉及低噪声低压差稳压器电路技术领域,尤其涉及一种具有过冲抑制和自适应补偿的多种ldo输出电压电路。

背景技术:

2.随着科技的进步,越来越多的功能需要被集成到芯片中,低耗能和小型化是系统级芯片(soc)在先进电子设备中的必然发展趋势。为了延长电池寿命和节约能耗,芯片内的电路功能仅在需要时使用,并在其余时间保持关闭状态。此外,soc解决方案需要完全集成的低功耗电源管理集成电路(pmic)。

3.目前的pmic通常是高效开关dc-dc转换器和低噪声低压差稳压器(ldo)的组合,以在芯片上产生多个清洁电源。由于严格的延迟要求以及其他关键性能,包含高性能模数转换器(adc)和压控振荡器(vco)等现代系统模块需要非常干净和高性能的电压源。因此,嵌入式系统中使用的ldo需要具有响应速度快、低噪声、过冲电压小、低功耗和多种输出电压挡位及面积小等性能。

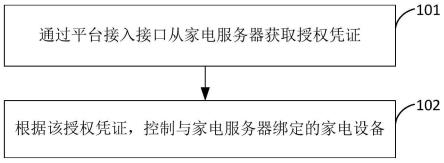

4.传统ldo电路结构图1所示,主要包括误差放大器(ea)、功率管(mp)、反馈电路网络及相应负载等。其中有些ldo片外接有大电容,该电容通常为uf级别;或者有些在无外接片外电容情况,为了系统稳定性也会在片内加有较大的电容。随着芯片小型化的发展,传统的这些ldo结构早已无法满足,但是在无片外或片内加的大电容时,又会对ldo响应速度和防过冲能力等性能提出更高要求。总体来说,传统ldo电路主要存在如下不足:(1)面积较大,由于片内增加的电容和功率管个数较多;(2)功耗较高;(3)响应速度慢,带载能力弱;(4)过冲电压大,易造成被供电模块功能异常;(5)稳定性差,由于当负载电流变化时,前面的补偿电路不能跟随其的变化。

技术实现要素:

5.本实用新型的目的是提供一种具有过冲抑制和自适应补偿的多种ldo输出电压电路,其具有功耗较低、相应速度快、带载能力强、面积小、能够实现过冲抑制和自适应补偿的优点。

6.本实用新型的目的是通过以下技术方案实现的:

7.一种具有过冲抑制和自适应补偿的多种ldo输出电压电路,包括:不同基准电压产生模块、误差放大器、中间级、功率管、防过冲模块、自适应弥勒补偿模块、以及反馈网络;其中:

8.所述误差放大器的基准电压输入端连接所述不同基准电压产生模块,所述误差放大器的反馈输入端连接所述反馈网络的第一端口;所述误差放大器的输出端经所述中间级连接所述功率管的栅极,所述误差放大器的电源极以及功率管的源极均连接vdd,所述功率管的漏极以及所述反馈网络的第二端口连接电路的输出端;所述防过冲模块连接所述中间级,以及电路的输出端;所述自适应密勒补偿模块的一端连接误差放大器的输出端,另一端

连接电路的输出端。

9.由上述本实用新型提供的技术方案可以看出:(1)无外接片外电容和片内增加电容,因此,可以减小电路面积;(2)在误差放大器与功率输出级之间由中间级进行连接,可以起到增大增益和提升驱动能力,以提高响应速度;(3)通过防过冲模块在检测电流的同时还给中间级提供偏置电压,降低了静态功耗,并且能够对电路的输出端电压实现过冲抑制;(5)通过自适应弥勒补偿模块进行自适应补偿,能够提高电路稳定性。

附图说明

10.为了更清楚地说明本实用新型实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他附图。

11.图1为本实用新型背景技术提供传统ldo电路结构示意图;

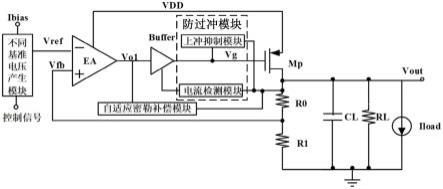

12.图2为本实用新型实施例提供的一种具有过冲抑制和自适应补偿的多种ldo输出电压电路的示意图;

13.图3为本实用新型实施例提供的中间级的结构示意图;

14.图4为本实用新型实施例提供的电流检测模块的结构示意图;

15.图5为本实用新型实施例提供的上冲抑制模块的结构示意图;

16.图6为本实用新型实施例提供的自适应弥勒补偿模块的结构示意图;

17.图7为本实用新型实施例提供的不同基准电压产生模块的结构示意图。

具体实施方式

18.下面结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型的保护范围。

19.首先对本文中可能使用的术语进行如下说明:

20.术语“包括”、“包含”、“含有”、“具有”或其它类似语义的描述,应被解释为非排它性的包括。例如:包括某技术特征要素(如原料、组分、成分、载体、剂型、材料、尺寸、零件、部件、机构、装置、步骤、工序、方法、反应条件、加工条件、参数、算法、信号、数据、产品或制品等),应被解释为不仅包括明确列出的某技术特征要素,还可以包括未明确列出的本领域公知的其它技术特征要素。

21.术语“由

……

组成”表示排除任何未明确列出的技术特征要素。若将该术语用于权利要求中,则该术语将使权利要求成为封闭式,使其不包含除明确列出的技术特征要素以外的技术特征要素,但与其相关的常规杂质除外。如果该术语只是出现在权利要求的某子句中,那么其仅限定在该子句中明确列出的要素,其他子句中所记载的要素并不被排除在整体权利要求之外。

22.除另有明确的规定或限定外,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如:可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也

可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本文中的具体含义。

23.下面对本实用新型所提供的一种具有过冲抑制和自适应补偿的多种ldo输出电压电路进行详细描述。本实用新型实施例中未作详细描述的内容属于本领域专业技术人员公知的现有技术。本实用新型实施例中未注明具体条件者,按照本领域常规条件或制造商建议的条件进行。本实用新型实施例中所用试剂或仪器未注明生产厂商者,均为可以通过市售购买获得的常规产品。

24.本实用新型实施例提供一种具有过冲抑制和自适应补偿的多种ldo输出电压电路,如图2所示,其主要包括:不同基准电压产生模块、误差放大器(ea)、中间级(buffer)、功率管(mp)、防过冲模块(由电流检测模块和上冲抑制模块组成)、自适应弥勒补偿模块、以及反馈网络(由电阻r0与r1组成);此外还包括一些负载,由于无外接片外电容和片内增加电容,因此图2中的cl主要是指被供电电路的寄生电容,rl和iload分别为负载电阻和负载电流。总体来说:

25.所述误差放大器的基准电压输入端连接所述不同基准电压产生模块,所述误差放大器的反馈输入端连接所述反馈网络的第一端口;所述误差放大器的输出端经所述中间级连接所述功率管的栅极,通过所述中间级对所述误差放大器的输出端进行增益,所述误差放大器的电源极以及功率管的源极均连接vdd,所述功率管的漏极以及所述反馈网络的第二端口连接电路的输出端(即整个电路的输出端);

26.所述防过冲模块连接所述中间级,以及电路的输出端;通过所述防过冲模块为所述中间级提供偏置电压,且偏置电压的大小由所述防过冲模块根据电路的输出端的电压大小调节,同时,通过所述防过冲模块对电路的输出端的电压进行过冲抑制;

27.所述自适应密勒补偿模块的一端连接误差放大器的输出端,另一端连接电路的输出端,根据误差放大器的输出端的电流与以及电路的输出端的电流进行自适应补偿。

28.为了更加清晰地展现出本实用新型所提供的技术方案及所产生的技术效果,下面针对电路各个部分的结构及相关原理进行介绍。

29.一、中间级(buffer)。

30.本实用新型实施例中,在误差放大器与功率输出级之间由buffer作为中间级进行连接,可以起到增大增益和提升驱动能力,以提高系统响应速度,如图3所示,提供了中间级的结构示例,使用了5个mos管与1个npn管,其中,5个mos管包括:pmos管pm0、第一pmos管pm1、nmos管nm0、第一nmos管nm1、第二nmos管nm2,npn管记为qn0,其中vo1是误差放大器的输出端电压,vg是中间级输出给功率管的栅极电压,第一nmos管nm1的栅极电压vn1是由电流检测模块提供的偏置电压,nmos管nm0二极管(即它的栅极与漏极)连接作电阻,nm2管起复位作用。

31.中间级主要结构如下:pmos管pm0与第一pmos管pm1的源极连接vdd(电源端),pmos管pm0、第一pmos管pm1及第二nmos管nm2的栅极相连接,并且与pmos管pm0的漏极、第二nmos管nm2的漏极以及npn管的qn0的集电极连接;第一pmos管pm1的漏极、第二nmos管nm2的源极、以及第一nmos管nm1的漏极连接在一起作为中间级的输出端;npn管qn0的基极作为中间级的输入端,与所述误差放大器的输出端连接,npn管qn0的发射极与nmos管nm0的栅极以及

漏极连接;nmos管nm0与第一nmos管nm1的源极接地,第一nmos管mos管nm1作为中间级的电流源,其栅极连接所述防过冲模块中的电流检测模块输出端。

32.二、防过冲模块。

33.由于电路输出端电流的变化,ldo反馈环路系统无法快速的反应,使得在电路的输出端电压会产生过冲现象,最终影响被供电模块(负载电路)的稳定性。

34.为了能够快速感知电路输出端电流的变化,同时结构简单和低功耗,因此在电路中增加了电流检测模块;同样为解决在电路输出端电压上冲的问题,增加了上冲抑制模块,二者共同构成防过冲模块,下面针对电流检测模块与上冲抑制模块分别进行介绍。

35.1、电流检测模块。

36.所述电流检测模块一端连接所述中间级的电流源,另一端连接电路的输出端,用于为所述中间级提供偏置电压,图4提供了电流检测模块的示例,主要包括两个mos管,分别为第二pmos管pm2与第三nmos管nm3,结构如下:第二pmos管pm2的源极连接vdd,栅极连接电路的输出端(vout),漏极连接第三nmos管nm3的漏极;第三nmos管nm3的漏极与栅极连接,并与所述中间级电流源的栅极相连接,源极接地。

37.电流检测模块输出电压vn1用于给中间级中的第一nmos管nm1提供偏置电压,当电路的输出端电流突然增大时,第二pmos管pm2的栅极电压降低,第二mos管pm2漏电流增大,这里第二nmos管nm2二极管(即它的栅极与漏极)连接做电阻,使得电压vn1电压增大,中间级中第一nmos管nm1电流增大,最终使得中间级输出端(vg)达到一个快速放电的效果,提高了中间级输出端的响应速度。电流检测模块在检测电流的同时还给中间级提供偏置电压,因此,降低了静态功耗。

38.电流检测模块和中间级可以很好的防止电路的输出端电流从小突变到大,引起的电路的输出端电压下冲的问题,将下冲最低电压点控制在一定范围,同时电流检测模块在电路正常工作时,只是作为偏置电路给中间级中的nm1管提供偏置电压,不会增加额外的静态功耗。

39.2、上冲抑制模块。

40.为解决在电路的输出端电流从大突变到小时,由于中间级输出端无法快速跟随电路的输出端的变化,两个输出端之间反应时间有一定差值,该差值部分时间输出电流一直给负载电容,造成电路的输出端电压上冲现象,本实用新型实施例中设计了上冲抑制模块来解决以上问题,所述上冲抑制模块一端连接所述中间级的输出端,另一端连接电路的输出端,用于实现过冲抑制。

41.如图5所示,提供了上冲抑制模块的示例,其主要包括:6个mos管,1个pnp管与1个npn管,其中,6个mos管包括:第三pmos管pm3、第四pmos管pm4、第五pmos管pm5、第四pmos管nm4、第五pmos管nm5、第六pmos管nm6,pnp管记为qp0,npn管为第一npn管qn1。主要结构如下:

42.第三pmos管pm3、第四pmos管pm4及第五pmos管pm5的源极连接vdd;第三pmos管pm3的栅极与漏极连接,并与第一npn管qn1的基极以及pnp管qp0的发射极连接;第四pmos管pm4的栅极与漏极连接,并与第五pmos管pm5的栅极以及第六nmos管nm6的漏极连接,第五pmos管pm5的漏极连接所述中间级的输出端;第六nmos管nm6的栅极与第一npn管qn1的集电极共同连接电路的输出端,第六nmos管nm6的源极作为第一外部偏置电压输入端,输入第一外部

偏置电压vn2;pnp管qp0的基极连接所述中间级的输出端,集电极连接第四nmos管nm4的漏极,第四nmos管nm4的栅极为第二外部偏置电压输入端,输入第二外部偏置电压vn3,第四nmos管nm4的源极与第五nmos管nm5的源极接地;第五nmos管nm5的栅极与漏极连接,并与第一npn管qn1的发射极连接。

43.本实用新型实施例中,为了便于描述过冲抑制的原理,可以将上冲抑制模块分为两部分:

44.(1)第一部分是用于在电路的输出端电流从大突变到小时对电路的输出端电压实现快速放电,其包括图5中的第三pmos管pm3、pnp管qp0、第四nmos管nm4、第五nmos管nm5和第一npn管qn1等元器件,在当电路输出端的电流从大突变到小时引起中间级输出端电流变化时,通过pnp管qp0对变化电流进行放大传给第一npn管qn1,以达到对电流的输出端电压快速泄电的目的,以防止多余电流不断给负载电容充电抬高电路的输出端电压。

45.(2)第二部分是用于限制电路的输出端上冲电压的最大值,其包括图5中的第六nmos管nm6、第四pmos管pm4和第五pmos管pm5等元器件,当电路的输出端上冲电压值vout与第一外部偏置电压vn2的差值大于第六nmos管nm6管的阈值电压时,通过第四pmos管pm4和第五pmos管pm5组成的电流镜电路给功率管栅极快速充电,以实现将栅极电压(也即中间级输出端电压)快速拉升起来,可以更好的遏制过冲电压的峰值。

46.本实用新型实施例中,vn2与vn3都是外部偏置电路提供的偏置电压。第一外部偏置电压vn2要随着电路的输出端电压挡位选择而变化,且要保证正常工作时电路的输出端电压与vn2的差值要小于第六nmos管nm6管的阈值电压,可以使得该部分只有当电路的输出端电流从大到小变化时才会开启工作,其他时刻处于关断状态,同样由第三pmos管pm3、pnp管qp0、第四nmos管nm4、第五nmos管nm5和第一npn管qn1组成的部分也是只有当输出端电流变化时才开启工作,这样可以使不会由于下冲抑制模块的增加而增大整个电路的功耗。

47.三、自适应弥勒补偿模块。

48.稳定性作为ldo的关键性能指标,直接决定ldo功能是否可以正常实现。电路输出端电流变化会引起ldo稳定性问题,使得整个ldo反馈环路系统性能变差。为了解决该问题,本实用新型实施例设计了一种自适应密勒补偿模块电路。

49.如图6所示,提供了一种自适应密勒补偿模块电路的示例,主要包括:两个电容、两个电阻、两个cmos开关及两个反相器,两个电容称为电容c0与第一电容c1,两个电阻称为第二电阻r2与第三电阻r3,两个反相器称为第一反相器inv1与第二反相器inv2。

50.结构如下:电容c0的上极板与第一电容c1的上极板相连,并与误差放大器的输出端连接;第一电容c1的下极板与第一cmos开关的第一端口相连,电容c0的下极板与第一cmos开关的第二端口相连;第二电阻r2的第一端口与第三电阻r3的第一端口相连,并与电容c0下极板以及第一cmos开关的第二端口相连;第三电阻r3的第二端口与第二cmos开关的第一端口相连;第二电阻r2的第二端口与第二cmos开关的第二端口相连,并与电路的输出端(vout)连接。

51.两个cmos开关结构相同,第一cmos开关包括第六pmos管pm6与第七nmos管nm7,第二cmos开关包括第七pmos管pm7与第八nmos管nm8;第一cmos开关结构如下:第六pmos管pm6的漏极与第七nmos管nm7的源极相连,作为第一cmos的第一端口,第六pmos管pm6的源极与第七nmos管nm7的漏极相连,作为第一cmos开关的第二端口,第六pmos管pm6的栅极、第七

nmos管nm7的栅极均作为第一cmos开关的控制信号输入端口,单独输入对应的第一控制信号swp、第二控制信号swn,且第一控制信号swp与第二控制信号swn同时输入对应的控制信号输入端口。第二cmos开关结构如下:第七pmos管pm7的漏极与第八nmos管nm8的源极相连,作为第二cmos开关的第一端口,第七pmos管pm7的源极与第八nmos管nm8的漏极相连,作为第二cmos开关的第二端口,第七pmos管pm7的栅极、第八nmos管nm8的栅极均作为第二cmos开关的控制信号输入端口,单独输入对应的第一控制信号swp、第二控制信号swn,且第一控制信号swp与第二控制信号swn同时输入对应的控制信号输入端口。其中,两个cmos开关控制信号,即第一控制信号swp与第二控制信号swn分别由电流检测模块输出电压vn1依次经第二反相器inv2和第一反相器inv1产生,如图6下半部分所示,电流检测模块输出电压vn1经第二反相机inv2产生第一控制信号swp,再经第一反相器inv1产生第二控制信号swn。

52.其原理如下:电容c0、第一电容c1以及第一cmos开关组成自适应弥勒电容电路,第二电阻r2、第三电阻r3以及第二cmos开关组成自适应调零电阻电路;当电路的输出端的电流从小变大时,所述防过冲模块中电流检测模块产生的偏置电压vn1增大,使得第一控制信号swp为低,第二控制信号swn为高,两个cmos开关导通使得电容c0和第一电容c1并联在一起以增大密勒补偿电容,第二电阻r2和第三电阻r3并联在一起以减小调零电阻的大小,这样很好的跟踪由输出端电流增大时功率管跨导gm增大而引起零极点变化,同时改善了带宽增大了响应速率;还可以很好的解决由输出端电流变化而引起的ldo反馈环路系统稳定性问题,当电路的输出端的电流从大变小或者正常工作时,第一控制信号swp为高,第二控制信号swn为低,两个cmos开关关闭,以确保该时刻ldo反馈系统的稳定性。

53.本领域技术人员可以理解,跨导gm是mos的一项属性,含义是mos管的漏电流的变化量除以栅源电压的变化量。

54.四、不同基准电压产生模块。

55.本实用新型实施例中,所述不同基准电压产生模块包括:电阻分压网络、逻辑模块和第三cmos开关;其中:电阻分压网络输出端与误差放大器的负输入端之间由第三cmos开关控制连接,逻辑模块一端连接外部电路输入控制信号,另一端连接第三cmos开关的控制信号输入端,即当外部电路输入不同控制信号时,通过逻辑模块产生控制第三cmos开关控制信号来选通输出不同的挡位基准电压,传输给误差放大器负输入端,电阻分压网络的ibias(偏置电流)输入端连接外部偏置电路,即由外部偏置电路提供ibias。

56.如图7所示,提供了不同基准电压产生模块的示例,该示例以4bit为例,虚线框中为4bit的逻辑模块,这里电阻分压网络产生16种不同电压值,其中av_ldo_sel《3:0》为4bit外部输入控制信号,av_ldo_sel《3:0》通过反相器inv3《0:3》产生s《7,5,3,1》,通过反相器inv4《0:3》产生s《6,4,2,0》,s《7,5,3,1》和s《6,4,2,0》用于给与非门nand1《0:15》输入端进行译码产生vref_selb《0:15》,vref_selb《0:15》经反相器inv5《0:15》产生vref_sel《0:15》,vref_selb《0:15》和vref_sel《0:15》用于控制第三cmos开关,即根据不同输入控制信号av_ldo_sel《3:0》来控制第三cmos开关选通电阻分压网络不同电压值传输给误差放大器负输入端,其中反相器inv3《0:3》、反相器inv4《0:3》、反相器inv5《0:15》和与非门nand1《0:15》分别表示4个相同大小反相器inv3、4个相同大小反相器inv4、16个相同大小反相器inv5和16个相同大小与非门nand1,这里第三cmos开关为16个,16个第三cmos开关由pmos管pm8《15:0》和nmos管nm9《15:0》构成,pmos管pm8《0:15》和nmos管nm9《0:15》分别表示16个相同大

小pmos管pm8和16个相同大小nmos管nm9相关结构与前述图6中的cmos开关相同,故不做赘述。

57.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求书的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。