一种基于fpga的极化码分布式信源编解码系统的设计方法

技术领域

1.本发明属于信源编码技术领域,具体涉及一种基于fpga的极化码分布式信源编解码系统的设计方法。

背景技术:

2.随着无线传感器网络、监控技术、卫星通信等技术的发展,资源受限的终端得到了越来越广泛的应用。由于这类终端因特定场景对其低功耗、小型化的要求而面临资源限制,所以在对数据压缩编码的过程中必须要考虑计算的复杂性。传统的信源编码方案采用联合编码的方式对传输数据进行压缩,由于这种方案要求编码端进行大量的计算,所以不再适用于这些领域的终端设备。而分布式信源编码(distributed source coding,dsc)方案在编码端独立编码,在解码端利用信源之间的相关性联合解码,从而将大量的计算过程从对资源敏感的编码端转移到了对资源不敏感的解码端,因此分布式信源编码更适合编码端资源受限的场合。

3.目前学术界关于如何在fpga上实现分布式信源编码已展开大量工作。tharini c等提出采用基于空间相关性的聚类算法来提升分布式信源编码的性能,并在fpga上进行了基于低能耗技术的实现。北京邮电大学的许迪佳采用ldpc码作为信道码,在fpga上实现了基于校验子的联合分布式信源信道编译码器。四川大学的吕顺研究了ldpc码校验位的分布式信源编解码系统,设计了基于fpga的硬件实现方案,并取得了不错的效果。而极化码作为第一个被严格证明可以达到香农极限的信道编码方法,其具有更优良的检错性能、更低的编译码复杂度和更好的码率兼容性,所以设计基于fpga的极化码分布式信源编解码系统具有很高的研究价值,且目前还没有在fpga上实现基于极化码的分布式信源编解码系统的先例。

技术实现要素:

4.本发明的目的是减小编码端复杂度的同时尽可能提高信源的压缩率。本发明利用crc校验码与系统极化码组合的方式,设计了一种码率自适应方案,相比传统按固定码率进行传输的方式,此方案能更大幅度地提高信源压缩率。

5.本发明的基本思想是利用信源之间地相关性,将边信息处理模块根据二进制输入序列和交叉概率产生的一个边信息序列作为信息比特序列,将经过系统极化码编码后的校验位序列缓存至删余模块中,根据解码模块的反馈信号逐比特将校验位序列送至解码模块中,未被发送的比特位则相当于被删余,进而达到提高信源压缩率的目的。

6.其中,数据编码,对128比特的数据先进行crc校验编码得到16比特的crc校验序列,将这144比特数据作为输入进行系统极化码编码,得到112比特的极化码校验位序列,再将此序列与16比特的crc校验序列进行拼接得到的128比特序列作为编码模块的输出。在编码模块中所需的校验位索引,g矩阵等数据先通过matlab生成后再导入至vivado中生成相应的rom,以实现对数据的调用。

7.在码率自适应方案的设计中,提高信源压缩率的关键步骤是删余模块逐个传输校验序列的过程,因此如何在保证译码结果正确的前提下传输最少的码字是码率自适应方案的关键问题。删余模块在第一次向解码模块传送数据时,根据交叉概率对应的信息熵的大小先一次性传送一定位数的数据。因为当传送数据过小导致码率小于信息熵时理论上解码模块无法正确解码。解码模块根据删余模块第一次传送的数据和边信息序列,开始尝试使用极化码sc译码算法进行解码,得到一个解码序列,再将此解码序列进行crc校验,若校验失败则说明解码序列有误,则反馈一个信号给删余模块请求更多的校验比特。删余模块收到反馈信号后根据顺序再传送一位的校验比特信息给解码模块使其重新进行解码和校验,重复这个过程,直至解码和校验成功得到正确的解码序列并输出。

8.边信息处理模块,模拟了一个虚拟信道,它将信源序列以一定的交叉概率生成一个边信息给解码模块。交叉概率越大,边信息和信源序列的差异越大,解码所需要的校验位也越多。交叉概率与信源序列长度的乘积即为边信息序列与信源序列实际差异的比特数,而具体差异的比特位置,则通过一个随机序列索引在相应比特位取反实现。

9.解码模块,包括极化码译码与crc校验两个过程。其中极化码译码算法采用系统极化码sc(successive cancellation)连续消除译码算法,该算法是最经典的极化码译码算法,而且考虑到在fpga这种资源受限的平台上实现时,sc译码算法相比于scl译码算法、ca-scl译码算法,具有计算复杂度低,资源占用少,译码时延低等优点。

10.具体地,在极化码译码过程中,由于sc译码算法中的f运算较为复杂不适于在硬件上实现,故采用最小和译码算法进行优化设计。由于对数似然比在运算过程中始终是以浮点数的形式参与的计算,而在fpga中直接对浮点数进行操作较为复杂,因为fpga直接操作的是一定位数的reg类型数据。所以要将浮点数形式的对数似然比定点量化为一定比特数的定点数。若量化比特数越多,则译码过程需要占用越多的资源;若量化比特数过小,则会降低译码性能。最终本文采用4比特定点量化的方案,即所有的对数似然比用4比特表示,又由于对数似然比有正有负,且最小和译码算法需要对数似然比的正负符号值直接参与运算,所以采用补码的形式,即1000~0111对应于-8~7。

附图说明

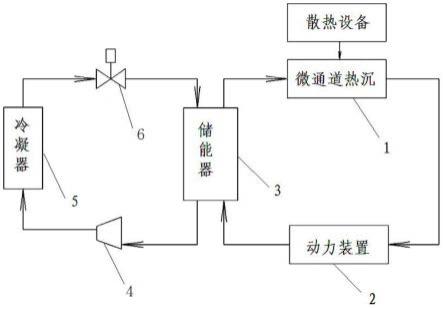

11.图1是本发明的设计流程图。

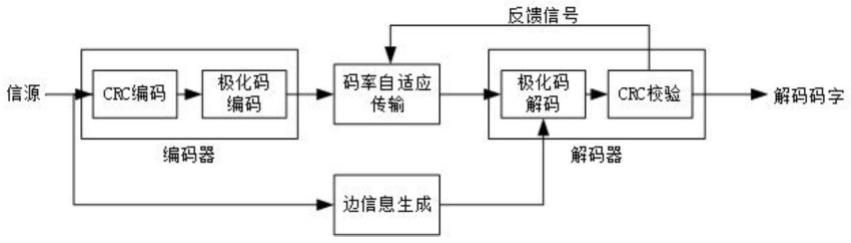

12.图2是本发明总体rtl设计图。

13.图3是本发明中的仿真波形图。

14.图4是本发明中的资源占用结果图。

具体实施方式

15.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本发明,并不用于限定本发明,所属领域技术熟悉人员根据上述发明内容,对本发明做出一些非本质的改进和调整进行具体实施,应仍属于本发明的保护范围。

16.图1中,一种基于fpga的极化码分布式信源编解码系统的设计方法,包括以下步骤:

17.(1)数据编码,将128比特的信源序列输入进编码模块,先生成crc校验序列,再进行系统极化码编码,将128比特的编码序列输出给删余模块;

18.(2)边信息生成,将128比特的信源序列输入进边信息处理模块,根据提前设定好的交叉概率大小对信源序列加入虚拟噪声,生成一个等长的边信息序列,输出给解码模块;

19.(3)数据传输,删余模块先缓存输入进来的编码序列,第一次传输数据时,根据交叉概率对应的信息熵按顺序传递一定位数的码字。后续根据是否收到解码模块输出的反馈信号再逐比特按顺序发送码字;

20.(4)数据解码与校验,接收到足够多的校验码字后译码得到正确的译码结果并输出。

21.其中,步骤1又分为以下几个步骤:

22.①

生成16比特的crc校验序列,并与128比特的信源序列拼接成144比特的序列;

23.②

将144比特长的序列进行系统极化码编码,根据校验位索引得到112比特的编码序列;

24.③

将112比特的编码序列与16比特的crc校验序列拼接后输出。

25.具体地,在所述步骤2中,输入的序列长度为128比特,设置的交叉概率为0.03,因此边信息与信源序列有round(128

×

0.03)=4位的不同。将一个随机序列的前四位作为索引将信源序列的相应位比特取反后输出作为边信息序列。

26.在所述步骤3中,交叉概率的信息熵根据以下公式计算得出:

27.h=-plog2(p)-(1-p)log2(1-p)

28.在实际设计中,设置交叉概率p=0.03,则信息熵h=0.1944。信息熵与校验序列长度的乘积为0.1944

×

128=24.8832,故删余模块在接收到编码序列后,第一次一次性传送前25比特的校验序列至解码模块。根据码率自适应方案,在后续的传输过程中,每接收到一次解码模块的反馈信号,按顺序传送下一位校验比特至解码模块。

29.具体地,在所述步骤4中,为方便在fpga中部署极化码sc译码算法,本发明采用最小和译码算法,可将复杂的f运算和g运算进行如下简化:

30.f(l1,l2)=sgn(l1)sgn(l2)min(|l1|,|l2|)

31.g(l1,l2,u)=(-1)ul1 l232.在对数似然比的量化方案上,采用4比特定点量化的方案,将原本为浮点数形式的对数似然比量化为4比特的定点数,量化公式如下:

[0033][0034]

具体地,在所述步骤4中的crc校验过程中,将144比特的极化码译码序列与一个16

×

144大小的crc校验矩阵的每一行相与再按位异或,得到一个16位的数组,若此数组为0则表示通过crc校验即解码成功,最后将此144比特的极化码译码序列中的crc校验序列剔除后,将剩余的128比特的解码结果输出,并使输出有效信号拉高。

[0035]

参照图2,基于fpga的极化码分布式信源编解码系统一共由四个模块组成。encode为编码模块,复杂数据编码;bsc为边信息生成模块,完成对边信息的处理;del为删余模块,为码率自适应方案的核心模块,负责传输校验位数据;decode为解码模块,负责极化码解码

和crc校验。系统输入时钟clk频率设置为200mhz。信源序列source采用串行的方式输入到系统中。复位信号rst由开发板io引脚控制,有效方式为低电平有效。

[0036]

参照图3,基于fpga的极化码分布式信源编解码系统设计完成后,为验证系统功能正确性,使用vivado自带的仿真工具,通过编写testbench进行仿真验证。仿真参数进行如下配置:码长n=256,信息比特数k=128,码率r=0.5,交叉概率p=0.03。从仿真波形图中可以看见,删余模块第一次传送了25比特的校验序列至解码模块,第一次解码失败后,删余模块继续逐比特传送,当一共传送了30比特的校验序列后,解码模块得到了正确的译码结果,输出128比特的解码序列decode_data,并使输出有效信号out_en拉高。

[0037]

参照图4,基于fpga的极化码分布式信源编解码系统综合完成后,资源占用情况符合开发板资源限制。

[0038]

本发明提出的一种基于fpga的极化码分布式信源编解码系统的设计方法,在xilinx公司的以virtex-7系列芯片xc7vx485tffg1761-2为主控芯片的vc707评估板上进行了设计实现,并使用128比特的随机二进制序列进行了性能测试,实验数据表明该系统的吞吐量能达到497kbps。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。