1.本发明涉及回旋加速器高频低电平系统设计技术,具体涉及一种基于脉冲闭环模式的回旋加速器优化启动装置。

背景技术:

2.回旋加速器高频腔启动过程遇到三个难点:第一个难点是要躲过次级电子倍增效应区域,因为次级电子倍增效应会限制高频系统的功率提升;第二个难点是要找到调谐点,因为调谐点找不到,即使跨越了次级电子倍增效应区域,仍然会限制高频系统的功率提升,找到调谐点的困难在于:中国原子能院设计的紧凑型回旋加速器,其次级电子倍增区域的起始点功率更低,将近为几十毫瓦,是现有技术级电子倍增区域的起始点最低1瓦的100多倍,在超低功率下找到调谐点,其设计难度更大;第三个难点在于:即使找到了调谐点、跨越了次级电子倍增效应区域,但在功率提升后的高电平连续信号阶段又会遇到新的问题:一方面要求信号为高功率信号,一方面当高功率信号时,如果腔体的品质因数q值稍微差一点,就会在连续信号阶段出现击穿和烧毁腔体的现象。例如当找到调谐点后,采用脉冲展宽的方式跨越电子倍增区域,脉冲展宽到50%后就成为连续信号、在连续信号下进入功率提升和正常运行阶段,后二个阶段要求功率保持高功率,但由于是连续的高功率信号,当积累到一定程度时又会击穿和烧毁高频腔体。

技术实现要素:

3.本发明针对现有技术存在的问题,提出一种基于脉冲闭环模式的回旋加速器优化启动装置,第一目的在于解决超低功率下找到调谐点的问题,第二目的在于解决高功率连续信号下容易击穿和烧毁腔体的问题。

4.本发明为解决其技术问题提出以下技术方案:

5.一种基于脉冲闭环模式的回旋加速器优化启动装置,该装置包括基于脉冲闭环模式的用于查找调谐点的调谐模块、基于脉冲闭环模式的低电平调制输出模块、基于脉冲闭环模式的幅度解调模块、基于脉冲闭环模式的cpu、基于脉冲闭环模式的数字控制器;该基于脉冲闭环模式的cpu设有用于控制高频腔启动过程的状态机,该状态机包括高频腔启动过程中的关闭状态s0、低功率调谐状态s1、脉冲搜索状态s2、功率提升状态s3、正常运行状态s4;该基于脉冲闭环模式的数字控制器设有pid调谐算法单元、dsp平衡算法单元、以及接收来自模拟电路的信号并实现与cpu的通信;所述pid调谐算法单元通过加快pid运算速率避免腔体失谐;所述dsp平衡算法单元通过调节电容马达保证两组腔体腔压平衡;

6.其特征在于:该基于脉冲闭环模式的用于查找调谐点的调谐模块,通过在低功率调谐阶段和脉冲搜索阶段找到调谐点,使得腔体频率和高频信号频率达到一致,以满足给粒子加速的条件,其中,脉冲搜索阶段通过输出高功率脉冲信号跨越电子倍增效应区域;所述脉冲闭环模式,既是低功率调谐状态的闭环模式为连续闭环模式,脉冲搜索状态、功率提升状态的闭环模式为脉冲闭环模式。

7.所述脉冲闭环模式,设置只有低功率调谐状态为连续信号运行模式,而功率搜索状态、功率提升状态、正常运行状态均为脉冲信号运行模式,且只有低功率调谐状态下的调谐闭环为连续信号运行模式下的闭环,而功率搜索状态下的调谐闭环、功率提升下的调幅闭环均为脉冲信号下的闭环,所述脉冲信号下的闭环是在脉冲高电平时判断闭环。

8.所述基于脉冲闭环模式的用于查找调谐点的调谐模块,在加速器腔体到cpu之间,顺序设有腔体正向信号forward、腔体取样信号pickup1、高频开关1和高频开关2、放大器和衰减器、鉴相器、调谐参数设置模块和调谐比较器;在低功率调谐状态下,cpu状态机从关闭状态s0转向低功率调谐状态s1,并将s1发送给数字控制器,数字控制器给调谐模块的高频开关1和高频开关2、以及低电平调制输出模块的高压开关3一个低电平信号,腔体的正向信号forward与腔体取样信号pickup1通过高频开关1和高频开关2选择连接各自的放大器一路,高压开关3选择14db衰减器一路;在功率搜索状态、功率提升状态、正常运行状态下,cpu状态机根据低功率调谐状态下的连续调谐闭环信号phaseok和脉冲搜索状态下的脉冲幅度闭环信号phaseok、以及功率提升状态的脉冲幅度闭环信号vdeeok,分别将s2、s3、s4信号发送给数字控制器,数字控制器给调谐模块的高频开关1和高频开关2、以及低电平调制输出模块的高压开关3一个高电平,腔体的正向信号forward与腔体取样信号pickup1通过高频开关1和高频开关2选择连接各自的衰减器一路,高压开关3连接3db衰减器一路;从所述鉴相器引出的adc模拟信号与所述调谐参数设置值进行加减运算,并将运算结果一路通过adc发送给数字控制器,另一路发送到调谐比较器;在低功率调谐状态下,调谐模块的调谐比较器采用连续信号判断调谐闭环,在脉冲搜索状态下,调谐模块的调谐比较器均采用脉冲高电平信号判断调谐闭环,当调谐比较器判断腔体频率和高频信号频率达到一致时,分别输出调谐闭环信号phaseok,并将该信号通过数字控制器发送给cpu;所述的腔体正向信号forward、腔体取样信号pickup1由所述低电平调制输出模块的低电平输出信号驱动。

9.所述基于脉冲闭环模式的幅度解调模块在加速器腔体和cpu之间顺序设有腔体取样信号pickup2、检波器、脉冲转连续电路、调幅参数设置模块和幅度比较器;该腔体取样信号pickup2二公分后,一路经过微分电路用作打火检测判断,另外一路经过检波器检波后用作幅度闭环判断;在功率提升状态下,当检波器检波结果的电压值与调幅参数设置做差后判断若在允许范围内,则判断为幅度闭环,并输出脉冲幅度闭环信号vdee_ok给cpu。

10.所述基于脉冲闭环模式的低电平调制输出模块,沿着数字控制器到加速器腔体的方向顺序设有高频信号数字转模拟模块、幅相调制模块、3db衰减器和14db衰减器、高频开关3、数控衰减器、低电平输出信号;在低功率调谐状态时,该低电平输出信号用于驱动腔体,以获得调谐模块的腔体正向信号forward、腔体取样信号pickup1;在功率搜索状态下,cpu接收到低功率调谐状态的连续调谐闭环phaseok信号后,cpu状态机向数字控制器发送s2信号,数字控制器向高频开关3发送占空比一定的脉冲,高频开关3按照定占空比脉冲,在脉冲高电平时接3db衰减器一路,在脉冲低电平时接14db衰减器一路,此时数控衰减器为定值不变;在功率提升状态时,cpu接收到脉冲搜索状态的脉冲调谐闭环信号phaseok后,其状态机向数字控制器发送s3信号,数字控制器向高频开关3发送占空比一定的脉冲,高频开关3按照定占空比脉冲,在脉冲高电平时接3db衰减器,在脉冲低电平时接14db衰减器,同时,数字控制器控制数控衰减器不断减小衰减,进而不断提升功率,直至幅度解调模块的调幅比较器输出脉冲幅度闭环信号vdeeok给cpu,此时完成功率提升阶段,进入正常运行阶段。

11.当cpu接收到功率提升状态下的脉冲幅度闭环信号vdeeok后,其状态机向数字控制器发送s4信号,数字控制器分别给出高频开关1、2、3一个高电平信号,高频开关1、2分别选择衰减器一路,高频开关3选择3db衰减器一路,数字控制器向高频开关3发送占空比一定的脉冲,高频开关3在脉冲高电平时接3db衰减器,在脉冲低电平时接14db衰减,数控衰减器为定值不变,同时,数字控制器启动dsp平衡算法单元,进行两个腔体之间的腔压平衡。

12.所述pid调谐算法设有pid运算模块、数据算术逻辑模块、以及多总线架构;所述数据算术逻辑模块是用于pid运算中加、乘法功能的实现,所述pid运算模块是将pid数字运算算法用dsp的汇编语言描述出来并在多总线架构下,利用并行处理指令实现多条运算指令的同步进行,从而加快pid运算速率,避免腔体失谐。

13.所述pid数值运算模块,设有pid运算输出y(n)子模块、pid上一时刻pid运算输出y(n-1)子模块、pid调节系数k0、k1、k2子模块、当前时刻和上一时刻和前两时刻的x(n),x(n-1)和x(n-2)pid输入子模块;所述数据算术逻辑模块包括dsp5600系列数字信号处理器,该dsp5600系列数字信号处理器将当前时刻、上一时刻和前两时刻的pid的输入x(n),x(n-1)和x(n-2)存储到寄存器r0中,将pid调节系数k0,k1,k2存储到寄存器r3中,利用全局总线对这两个寄存器进行读写,并利用dsp中的累加器和乘法功能,采用汇编指令实现y(n)=y(n-1) k0*x(n) k1*x(n-1) k2*x(n-2),这种并行汇编指令有效提升了pid算法运算速率。

14.所述dsp平衡算法单元,设有电压平衡比值计算单元、调整电压平衡单元;该电压平衡比值计算单元用于比值关系式:其中,c12是两组腔之间的耦合电容值,分为两部分c12”和c12’,其中c12”是d1腔的电容,c12’是d2腔的电容;该调整电压平衡单元通过改变c12”和c12’的比值即可调整腔体d板电压。

15.所述基于脉冲闭环模式的cpu,采用状态机的s1、s2、s3、s4状态控制数字控制器,再由数字控制器控制高频开关1、高频开关2、高频开关3。

16.本发明的优点效果

17.1、本发明采用预调谐点 脉冲闭环模式,不仅提高了腔体启动过程中的品质因数,还避免了因功率过高而带来的安全隐患。所述预调谐点就是在二个阶段提升功率之前都找到了预调谐点。第一个预调谐点是在低功率调谐状态进入脉冲搜索状态以前找到了调谐点,使得进入脉冲搜索状态提高功率时能够做到给腔体的输入的功率最大,腔体反射回来的功率最小,也就是腔体的q值最高。第二个预调谐点是在从脉冲搜索状态进入功率提升状态以前找到了调谐点,也就是在脉冲搜索阶段进行第二次找调谐点,使得进入功率提升状态时能够做到给腔体的输入的功率最大,腔体反射回来的功率最小;所述脉冲闭环模式就是采用定占空比的脉冲代替脉冲搜索、功率提升、正常运行状态下的高电平连续模式,从而解决调试过程中功率过高烧毁发射机和耦合窗的问题,同时,由于是在脉冲高电平时判断调谐点,既不影响调谐闭环的判断也兼顾了避免功率过高烧毁发射机和耦合窗的问题。

18.2、本发明通过调谐模块、低电平调制输出模块、幅度解调模块、数字控制器的pid调谐算法单元和dsp平衡算法单元、cpu状态机的有机结合,解决了本领域长期以来加速器腔体启动过程中在超低功率下查找调谐点的难题,同时也解决了腔体启动过程由于功率变化需要二次查找调谐点的难题:通过设置调谐模块的高频开关1和高频开关2、放大器、衰减器、鉴相器,解决了超低功率下微弱信号无法被鉴相器识别和高功率信号下腔体信号进入

鉴相器会烧毁鉴相器的难题;通过pid调谐算法单元、调谐参数设置模块、以及调谐模块调谐比较器的有机结合,解决了查找调谐点时pid运算速率跟不上状态变化的难题;通过低电平调制输出模块的低电平输出信号、高频开关3、3db衰减与14db衰减和调谐模块的有机结合,不仅实现了低功率调谐状态下的调谐闭环,还实现了高功率脉冲搜索状态下的调谐闭环;通过调谐模块、幅度解调模块的调谐闭环、幅度闭环信号和cpu状态机、以及数字控制器相向结合,解决了调谐闭环的二个阶段中对高频信号1、2、3的控制问题,使得三个高频开关在超低功率时选择放大器一路和14db衰减器一路,从而使得微弱信号能够进入鉴相器的健翔范围;在高功率时高频信号1、2、3选择衰减器一路和3db衰减器一路,从而使得高功率的腔体取样信号不会因为超出鉴相器的温度范围而烧毁鉴相器。总之,通过各个模块的有机结合,相互支持和相互以来,产生了新的效果。取得了实质性的进步。

附图说明

19.图1为本发明基于脉冲闭环模式的回旋加速器优化启动装置示意图;

20.图2为发明优化启动装置的pid调谐算法示意图。

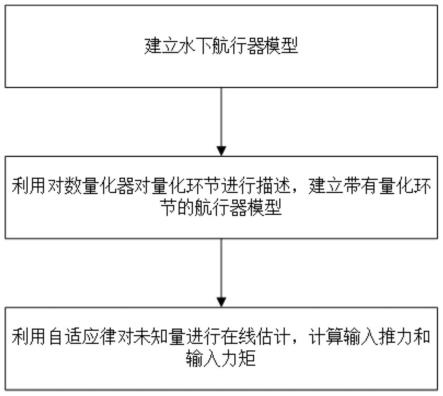

21.图3为本发明一种基于脉冲闭环模式的回旋加速器优化启动方法流程图。

具体实施方式

22.本发明设计原理

23.1、本发明创新点在于:预调谐点 脉冲闭环模式。所述预调谐点就是在二个阶段提升功率之前都找到了预调谐点。第一个预调谐点是在低功率调谐状态进入脉冲搜索状态以前找到了调谐点,使得进入脉冲搜索状态提高功率时能够做到给腔体的输入的功率最大,腔体反射回来的功率最小,也就是腔体的q值最高。第二个预调谐点是在从脉冲搜索状态进入功率提升状态以前找到了调谐点,也就是在脉冲搜索阶段进行第二次找调谐点,使得进入功率提升状态时能够做到给腔体的输入的功率最大,腔体反射回来的功率最小;所述脉冲闭环模式就是采用定占空比的脉冲代替脉冲搜索、功率提升、正常运行状态下的高电平连续模式,从而解决调试过程中功率过高烧毁发射机和耦合窗的问题,同时,由于是在脉冲高电平时判断调谐点,既不影响调谐闭环的判断也兼顾了避免功率过高烧毁发射机和耦合窗的问题。

24.2、本发明设计难点:难点之一在于实现超低功率下的调谐。1)相比现有技术最低功率1瓦,本发明低功率只有几十毫瓦,相差100多倍。由于超低功率信号下腔体信号微弱,不能进入到鉴相器的鉴相范围;2)当从低功率调谐到脉冲搜索状态,功率变化则调谐点也会发生变化,还需要重新找调谐点,重新找调谐点时,取样腔体信号是高功率信号了,高功率信号又会在进入鉴相器时把鉴相器烧毁;3)要求pid算法适应状态变化的速率,适应上一个状态和下一个状态数据处理速度的要求。pid输出结果用于控制腔体的马达,使得腔体信号和高频信号达到一致,从而实现调谐闭环,在下一个状态还没有到达之前,要求pid将上一个状态的数据处理完毕,才不至于因为上一个状态的数据还没有处理完毕就把下一个状态和上一个状态的数据混合在一起处理,导致输出错误。难点之二在于:高功率情况下既要满足高功率要求,又要防止腔体被击穿毁坏。

25.3、本发明解决方案:对于第一个难点的解决方案是:1)设置3个高频开关,在调谐

模块设置高频开关1、高频开关2,并设置高频开关1、2对应的放大器、衰减器。在低电平调制输出模块设置高频开关3,并设置3db、14db衰减器。当低功率调谐状态时,通过高频开关1、2选择放大器,放大器为25db,使得信号放大进入鉴相器范围,由此解决了信号微弱不容易键入鉴相器范围的问题,并且为了保证在低功率调谐状态给腔体输入的是超低功率信号,还需要高频开关3选择14db衰减器,保证给腔体输出的信号是几十毫伏的超低功率的信号;2)当转入功率搜索状态时,为了避免腔体取样信号烧毁鉴相器,使得高频开关1、2选择衰减器一路,这个衰减只是微弱的衰减,以不烧毁鉴相器为标准,因此,衰减器的设计要适度23db;为了保证功率搜索状态给腔体输入的是高功率信号,还需要高频开关3选择3db衰减器,通过高频开关3选择不同的衰减器提高或者降低功率。3)加快pid处理速度:方法之一几个指令一起执行,包括加法指令、乘法指令、输入指令、输出指令、移位指令,相比常规方法的指令串行执行加快了速度;加快pid的处理速度的方法之二是采用汇编语言,由于汇编语言相比其他语言更为底层,所以运算速度快;加快pid的处理速度的方法之三是采用多总线架构,相比只有一条总线的架构进一步突出了并行处理的效果。以上三种方法相互支持相互依存,缺一不可,只有三者结合才能达到最佳效果。

26.对于第二个难题的解决方案是:在功率搜索状态、功率提升状态、正式运行状态,用定长占空比的脉冲信号代替高功率连续信号;在功率搜索状态下,用脉冲高电平判断调谐闭环;在功率提升状态下,用脉冲高电平时判断幅度闭环;在正式运行状态下,将高功率连续信号变为定长占空比的脉冲信号,这样,用离散式的高功率脉冲信号代替高功率连续信号,减少了高功率信号的累计效应。由于离散式的脉冲信号的功率并没有降低,同样达到了功率搜索状态、功率提升状态、正式运行状态的高功率要求。其中,功率提升状态和正式运行状态的功率要高于脉冲搜索状态的功率,因为这个功率是脉冲搜索状态后功率提升后的功率。

27.下面结合附图对本发明做出进一步的解释:

28.一种基于脉冲闭环模式的回旋加速器优化启动装置如图1所示,该装置包括基于脉冲闭环模式的用于查找调谐点的调谐模块、基于脉冲闭环模式的低电平调制输出模块、基于脉冲闭环模式的幅度解调模块、基于脉冲闭环模式的cpu、基于脉冲闭环模式的数字控制器;该基于脉冲闭环模式的cpu设有用于控制高频腔启动过程的状态机,该状态机包括高频腔启动过程中的关闭状态s0、低功率调谐状态s1、脉冲搜索状态s2、功率提升状态s3、正常运行状态s4;该基于脉冲闭环模式的数字控制器设有pid调谐算法单元、dsp平衡算法单元、以及接收来自模拟电路的信号并实现与cpu的通信;所述pid调谐算法单元通过加快pid运算速率避免腔体失谐;所述dsp平衡算法单元通过调节电容马达保证两组腔体腔压平衡;

29.其特点是:该基于脉冲闭环模式的用于查找调谐点的调谐模块,通过在低功率调谐阶段和脉冲搜索阶段找到调谐点,使得腔体频率和高频信号频率达到一致,以满足给粒子加速的条件,其中,脉冲搜索阶段通过输出高功率脉冲信号跨越电子倍增效应区域;所述脉冲闭环模式,既是低功率调谐状态的闭环模式为连续闭环模式,脉冲搜索状态、功率提升状态的闭环模式为脉冲闭环模式。

30.补充说明1:

31.1、图1分为上、中、下三部分,最上层是调谐模块、最下层是幅度解调模块,中间是低电平输出模块,最上层、最下层都是从腔体取样,中间层是给腔体输入高频信号。从腔体

取样的目的是进行调谐闭环和幅度闭环;给腔体输入高频信号的目的是使腔体提升功率至可加速粒子的电压上,并保证腔体频率稳定在高频信号频率上,从而达到给粒子加速的目的。

32.2、但功率的提升要满足二个条件,第一是找到调谐点了,也就是调谐闭环了,这个时候向腔体输出的信号才能提升功率;第二个是幅度闭环了,虽然调谐闭环找到调谐点了,但是功率有可能还是达不到设定的高度,因此需要实现幅度闭环,也就是幅度达到设定高度。因此,中间层的低电平输出信号是一个功率从低到高的过程。

33.所述脉冲闭环模式,设置只有低功率调谐状态为连续信号运行模式,而功率搜索状态、功率提升状态、正常运行状态均为脉冲信号运行模式,且只有低功率调谐状态下的调谐闭环为连续信号运行模式下的闭环,而功率搜索状态下的调谐闭环、功率提升下的调幅闭环均为脉冲信号下的闭环,所述脉冲信号下的闭环是在脉冲高电平时判断闭环。

34.补充说明2

35.所述脉冲闭环模式,就是除了低功率调谐状态为连续闭环以外,功率搜索状态、和功率提升状态都是在脉冲信号的高电平下实现闭环的。

36.所述基于脉冲闭环模式的用于查找调谐点的调谐模块,在加速器腔体到cpu之间,顺序设有腔体正向信号forward、腔体取样信号pickup1、高频开关1和高频开关2、放大器和衰减器、鉴相器、调谐参数设置模块和调谐比较器;在低功率调谐状态下,cpu状态机从关闭状态s0转向低功率调谐状态s1,并将s1发送给数字控制器,数字控制器给调谐模块的高频开关1和高频开关2、以及低电平调制输出模块的高压开关3一个低电平信号,腔体的正向信号forward与腔体取样信号pickup1通过高频开关1和高频开关2选择连接各自的放大器一路,高压开关3选择14db衰减器一路;在功率搜索状态、功率提升状态、正常运行状态下,cpu状态机根据低功率调谐状态下的连续调谐闭环信号phaseok和脉冲搜索状态下的脉冲幅度闭环信号phaseok、以及功率提升状态的脉冲幅度闭环信号vdeeok,分别将s2、s3、s4信号发送给数字控制器,数字控制器给调谐模块的高频开关1和高频开关2、以及低电平调制输出模块的高压开关3一个高电平,腔体的正向信号forward与腔体取样信号pickup1通过高频开关1和高频开关2选择连接各自的衰减器一路,高压开关3连接3db衰减器一路;从所述鉴相器引出的adc模拟信号与所述调谐参数设置值进行减法运算,并将运算结果一路通过adc发送给数字控制器,另一路发送到调谐比较器;在低功率调谐状态下,调谐模块的调谐比较器采用连续信号判断调谐闭环,在脉冲搜索状态下,调谐模块的调谐比较器均采用脉冲高电平信号判断调谐闭环,当调谐比较器判断腔体频率和高频信号频率达到一致时,分别输出调谐闭环信号phaseok,并将该信号通过数字控制器发送给cpu;所述的腔体正向信号forward、腔体取样信号pickup1是由所述低电平调制输出模块驱动加速器腔体后,由采样电缆采样得到。

37.补充说明3

38.调谐模块与其它二个模块的关系。虽然其是一个独立模块,但调谐模块是离不开低电平输出模块的低电平输出信号:低电平输出信号驱动加速器腔体才会产生腔体正向信号forward、腔体取样信号pickup1;调谐模块还离不开cpu状态机的控制,cpu状态机控制调谐模块的高频开关1、2,同时控制高频开关3,高频开关3虽然属于低电平输出模块,但也会影响调谐模块第二个阶段也就是功率搜索阶段的调谐闭环:具体为,在功率搜索阶段,进入

高频开关1、2的腔体信号功率增强了,此时不需要选择放大器而选择衰减器,因为信号太强了所以要衰减一下才便于鉴相器鉴相,只有进入鉴相器鉴相范围才能进行后面的功率搜索状态下的调谐闭环判断。而进入高频开关1、2的腔体信号功率增强是因为高频开关选择了3db衰减器才使得进入腔体的信号功率增强。总之,调谐模块离不开其他二个模块是因为调谐模块是为二个阶段服务的,只有该调谐模块要与其它二个模块有机结合才能实现二个阶段的调谐闭环判断。

39.进一步地,所述基于脉冲闭环模式的幅度解调模块在加速器腔体和cpu之间顺序设有腔体取样信号pickup2、检波器、脉冲转连续电路、调幅参数设置模块和幅度比较器;该腔体取样信号pickup2二公分后,一路经过微分电路用作打火检测判断,另外一路经过检波器检波后用作幅度闭环判断;在功率提升状态下,当检波器检波结果的电压值与调幅参数设置做差后判断若在允许范围内,则判断为幅度闭环,并输出脉冲幅度闭环信号vdee_ok给cpu。

40.进一步地,所述基于脉冲闭环模式的低电平调制输出模块,沿着数字控制器到加速器腔体的方向顺序设有高频信号数字转模拟模块、幅相调制模块、3db衰减器和14db衰减器、高频开关3、数控衰减器、低电平输出信号;在低功率调谐状态时,该低电平输出信号驱动加速器腔体,从而通过采样电缆获得调谐模块的腔体正向信号forward、腔体取样信号pickup1;在功率搜索状态下,cpu接收到低功率调谐状态的连续调谐闭环phaseok信号后,cpu状态机向数字控制器发送s2信号,数字控制器向高频开关3发送占空比一定的脉冲,高频开关3按照定占空比脉冲,在脉冲高电平时接3db衰减器一路,在脉冲低电平时接14db衰减器一路,此时数控衰减器为定值不变;在功率提升状态时,cpu接收到脉冲搜索状态的脉冲调谐闭环信号phaseok后,其状态机向数字控制器发送s3信号,数字控制器向高频开关3发送占空比一定的脉冲,高频开关3按照定占空比脉冲,在脉冲高电平时接3db衰减器,在脉冲低电平时接14db衰减器,同时,数字控制器控制数控衰减器不断减小衰减,进而不断提升功率,直至幅度解调模块的调幅比较器输出脉冲幅度闭环信号vdeeok给cpu,此时完成功率提升阶段,进入正常运行阶段。

41.补充说明5

42.1、低电平调制输出模块和其他二类模块的关系:设置低电平调制输出模块的目的是在不同的状态下给腔体输入不同功率的信号,同时,低电平调制输出模块也需要其它二个模块的配合:在低功率调谐状态,由于其输出给腔体的信号功率很低,所以需要调谐模块的高频开关1、2通过放大器把信号放大,需要低功率输出模块的高频开关3选择14db衰减一路;在功率搜索阶段、功率提升状态、正常运行状态,由于输出给腔体的信号功率增强了,所以需要3个高频开关都选择筛检器一路或者3db衰减器;

43.2、低电平调制输出模块还通过高频开关3、数控衰减器的组合控制四种状态下输出给腔体的信号功率的大小,当低功率调谐状态时,高频开关3选择14db衰减器且数控衰减器为定值不变;在脉冲搜索状态时,高频开关3选择3db衰减器且数控衰减器为定值不变;在功率提升状态时,数字控制器控制数控衰减器不断减小衰减并且高频开关3选择3db衰减器;在正常运行阶段,高频开关3选择3db衰减器、且数控衰减器为定值不变。

44.进一步地,当cpu接收到功率提升状态下的脉冲幅度闭环信号vdeeok后,其状态机向数字控制器发送s4信号,数字控制器分别给出高频开关1、2、3一个高电平信号,高频开关

1、2分别选择衰减器一路,高频开关3选择3db衰减器一路,数字控制器向高频开关3发送占空比一定的脉冲,高频开关3在脉冲高电平时接3db衰减器,在脉冲低电平时接14db衰减,数控衰减器为定值不变,同时,数字控制器启动dsp平衡算法单元,进行两个腔体之间的腔压平衡。

45.进一步地,所述pid调谐算法设有pid运算模块、数据算术逻辑模块、以及多总线架构;所述数据算术逻辑模块是用于pid运算中加、乘法功能的实现,所述pid运算模块是将pid数字运算算法用dsp的汇编语言描述出来并在多总线架构下,利用并行处理指令实现多条运算指令的同步进行,从而加快pid运算速率,避免腔体失谐。

46.进一步地,所述pid数值运算模块,设有pid运算输出y(n)子模块、pid上一时刻pid运算输出y(n-1)子模块、pid调节系数k0、k1、k2子模块、当前时刻和上一时刻和前两时刻的x(n),x(n-1)和x(n-2)pid输入子模块;所述数据算术逻辑模块包括dsp5600系列数字信号处理器,该dsp5600系列数字信号处理器将当前时刻、上一时刻和前两时刻的pid的输入x(n),x(n-1)和x(n-2)存储到寄存器r0中,将pid调节系数k0,k1,k2存储到寄存器r3中,利用全局总线对这两个寄存器进行读写,并利用dsp中的累加器和乘法功能,采用汇编指令实现y(n)=y(n-1) k0*x(n) k1*x(n-1) k2*x(n-2);

47.补充说明6

48.这种并行汇编指令有效提升了pid算法运算速率,通过y(n)子模块的输出结果调谐马达的运动从而改变腔体的谐振频率,进而影响腔体采样信号与正向信号的相位差,使得鉴相器的输出电压趋近于设置参数模块的设置电压,所述设置参数模块的设置电压即为预设的腔体频率和高频信号频率达到一致时的腔体采样信号和腔体正向信号相位差的电压,所述鉴相器的输出电压为实际的腔体采样信号和腔体正向信号相位差的电压。

49.进一步地,所述dsp平衡算法单元,设有电压平衡比值计算单元、调整电压平衡单元;该电压平衡比值计算单元用于比值关系式:其中,c12是两组腔之间的耦合电容值,分为两部分c12”和c12’,其中c12”是d1腔的电容,c12’是d2腔的电容;该调整电压平衡单元通过改变c12”和c12’的比值即可调整腔体d板电压。

50.进一步地,所述基于脉冲闭环模式的cpu,采用状态机的s1、s2、s3、s4状态控制数字控制器,再由数字控制器控制高频开关1、高频开关2、高频开关3。

51.补充说明7

52.在低功率调谐阶段,cpu判断当前加速器腔体为开机状态,将状态机的s0转为s1并将s1发给数字控制器,数字控制器给高频开关1、2、3低电平信号,高频开关1、2分别选择放大器一路,高频开关3选择14db衰减器一路;

53.在功率搜索阶段,cpu接到调谐模块的调谐闭环信号phaseok后,将s1转为s2并将s2发给数字控制器,数字控制器给高频开关1、2、3定展宽的脉冲信号,高频开关1、2在脉冲低电平时选择放大器一路,在脉冲低电平时选择衰减器一路,高频开关3在脉冲低电平时选择14db衰减器一路,在脉冲高电平时选择3db衰减器一路;

54.在功率提升阶段,cpu接到幅度解调模块的vdeeok后,将s2转为s3并将s3发给数字控制器,数字控制器给高频开关1、2、3定展宽的脉冲信号,高频开关1、2在脉冲低电平时选择放大器一路,在脉冲低电平时选择衰减器一路,高频开关3在脉冲低电平时选择14db衰减

器一路,在脉冲高电平时选择3db衰减器一路;同时,数字控制器还控制数字衰减器减小衰减。

55.在正常运行阶段,cpu已经接到接到调谐模块的二次调谐闭环信号phaseok、以及幅度解调模块vdeeok后,将s3转为s4并将s4发给数字控制器,数字控制器给高频开关1、2、3定展宽的脉冲信号,高频开关1、2在脉冲低电平时选择放大器一路,在脉冲低电平时选择衰减器一路,高频开关3在脉冲低电平时选择14db衰减器一路,在脉冲高电平时选择3db衰减器一路;同时,数字控制器控制数字衰减器为定值不变。

56.基于上述一种基于脉冲闭环模式的回旋加速器优化启动装置,本发明还设计了一种基于脉冲闭环模式的回旋加速器优化启动方法,其特点是,包括以下步骤:

57.步骤一、初始化准备工作

58.1)建立回旋加速器低电平系统的一键启动流程;

59.2)建立cpu状态机,状态机状态为s0~s4;

60.步骤二、进入脉冲闭环模式下的低功率调谐状态并实现低功率调谐状态下的调谐闭环;

61.步骤三、进入脉冲闭环模式下的脉冲搜索状态并实现脉冲搜索状态下的调谐闭环;

62.步骤四、进入脉冲闭环模式下的功率提升状态并实现功率提升状态下的幅度闭环;

63.步骤五、进入脉冲闭环模式下的正常运行状态并实现正常运行状态下的腔压平衡。

64.进一步地,所述步骤二的进入脉冲闭环模式下的低功率调谐状态并实现低功率调谐状态下的调谐闭环,具体过程如下:

65.1)低电平调制输出模块向加速器腔体输入一个低电平脉冲信号,该低电平脉冲信号驱动加速器腔体,通过取样电缆从加速器取样获得调谐模块的腔体正向信号forward、腔体取样信号pickup1、腔体取样信号pickup2;

66.2)cpu状态机从关闭状态s0转向低功率调谐状态s1,并将s1发送给数字控制器,

67.3)数字控制器分别给调谐模块的高频开关1和高频开关2、以及低电平调制输出模块的高压开关3一个低电平信号;

68.4)腔体的正向信号forward与腔体取样信号pickup1通过高频开关1和高频开关2选择连接各自的放大器一路,保证低功率信号能够进入鉴相器鉴相范围;高压开关3选择14db衰减器一路;

69.5)从鉴相器引出的adc模拟信号与所述调谐参数设置值进行加减运算,并将运算结果一路通过adc发送给数字控制器,另一路发送到调谐比较器;

70.6)pid调谐算法单元进行低功率调谐状态下的调谐闭环运算:当判断腔体频率和高频信号频率达到一致时,输出调谐闭环信号phaseok给cpu,实现低功率调谐状态下调谐闭环,进入脉冲搜索阶段;低功率调谐状态下,调谐比较器在连续信号下判断调谐闭环。

71.进一步地,所述步骤三的进入脉冲闭环模式下的脉冲搜索状态并实现脉冲搜索状态下的调谐闭环,具体过程如下:

72.1)cpu接到低功率调谐状态下的调谐闭环信号phaseok后,将s2信号发送给数字控

制器;

73.2)数字控制器将定占空比的脉冲信号发送给高频开关3,同时发送给高频开关1、2;

74.3)调谐模块的高频开关1、高频开关2根据定占空比的脉冲信号的高电平信号选择衰减器一路,由于脉冲搜索状态下功率提高,功率提高后的腔体正向信号forward、腔体取样信号pickup1通过衰减器进入鉴相器;高频开关3根据定占空比的脉冲信号,在脉冲高电平时选择3db衰减器一路,在脉冲低电平时选择14db衰减器一路,从而实现功率搜索状态下的等宽度脉冲;

75.4)鉴相器引出的adc模拟信号与所述调谐参数设置值进行加减运算,并将运算结果一路通过adc发送给数字控制器,另一路发送到调谐比较器;

76.5)pid调谐算法单元进行脉冲搜索状态下的调谐闭环运算:当判断腔体频率和高频信号频率达到一致时,输出脉冲调谐闭环信号phaseok给cpu,实现脉冲搜索状态下的脉冲调谐闭环,并关闭调谐比较器,进入功率提升状态;在脉冲搜索状态下,调谐比较器在脉冲高电平时判断调谐点。

77.进一步地,所述步骤四的进入脉冲闭环模式下的功率提升状态并实现功率提升状态下的幅度闭环,具体过程如下:

78.1)cpu接到功率搜索状态下的脉冲调谐闭环信号phaseok后,将s3信号发送给数字控制器;

79.2)数字控制器将定占空比的脉冲信号发送给高频开关3,同时发送给高频开关1、2;

80.3)高频开关3根据定占空比的脉冲信号,在脉冲高电平时选择3db衰减器一路,在脉冲低电平时选择14db衰减器一路,从而实现功率提升状态下的等宽度脉冲;调谐模块的高频开关1、高频开关2根据定占空比的脉冲信号的高电平信号选择衰减器一路,低电平选择放大一路。

81.4)数字控制器控制数控衰减器不断减小衰减,进而不断提升功率,直至幅度解调模块的调幅比较器输出脉冲幅度闭环vdeeok信号给cpu,此时完成功率提升阶段,实现幅度闭环,进入正常运行状态。

82.进一步地,所述步骤五的进入脉冲闭环模式下的正常运行状态并实现正常运行状态下的腔压平衡,具体过程如下:

83.1)cpu接到功率提升状态下的脉冲幅度闭环信号vdee_ok后,将s4信号发送给数字控制器;

84.2)数字控制器将等宽的脉冲信号发送给高频开关3,同时发送给高频开关1、2;

85.3)高频开关3根据定占空比的脉冲信号,在脉冲高电平时选择3db衰减器一路,在低电平时选择14db衰减器一路,从而实现正常运行状态下的定占空比的脉冲;调谐模块的高频开关1、高频开关2根据等宽脉冲信号的高电平信号选择衰减器一路,低电平时选择放大一路。

86.4)数控衰减器为定值不变;

87.5)数字控制器启动dsp平衡算法单元进行两个腔体之间的腔压平衡。

88.进一步地,所述过程5)的数字控制器启动dsp平衡算法单元进行两个腔体之间的

腔压平衡,具体步骤如下:

89.1)将加速器两组腔体之间为电容耦合时,由于加工设计等因素导致的两组腔体出现电压不平衡的情况用比值关系表示:

[0090][0091]

其中,c

12

是两组腔之间的耦合电容值,分为两部分c

12”和c

12’,其中c

12”是d1腔的电容,c

12’是d2腔的电容;

[0092]

2)改变c

12”和c

12’的比值即可调整d电压,其平衡控制算法如下:鉴相器输出结果tphase决定调整电容马达的运动频率,电机运动步数设置值dsteps决定马达的运动步数,当dsteps》0,tphase》0时,d1腔组马达以2倍速率朝正方向移动,d2腔组马达停止不动;当dsteps》0,tphase《0时,d2腔组马达以2倍速朝反方向运动,d1腔组马达不动;当dsteps《0,tphase》0时,d2腔组马达以两倍速朝正方向运动,d1腔组马达不动;当dsteps《0,tphase《0时,d1腔组马达以两倍速朝反方向运动,d2腔组马达不变。

[0093]

进一步地,其特征在于:所述pid调谐算法单元进行调谐闭环运算,实现过程如下:

[0094]

1)数字式pid算法表示为:

[0095]

y(n)=y(n-1) k0x(n) k1x(n-1) k2(n-2);

[0096]

其中y(n)为pid运算输出,y(n-1)为上一时刻pid运算输出,k0、k1、k2都为pid调节系数,x(n),x(n-1)和x(n-2)为当前时刻、上一时刻和前两时刻的pid输入;

[0097]

2)在dsp的x存储器中使用r0和r3寄存器,由全局数据总线进行读写操作;

[0098]

3)将当前时刻、上一时刻和前两时刻的pid的输入x(n),x(n-1)和x(n-2)存储到寄存器r0中,将k0,k1,k2存储到寄存器r3中;

[0099]

4)利用全局总线对这两个寄存器进行读写,并利用dsp中的累加器和乘法功能、以及汇编语言实现y(n)=y(n-1) k0*x(n) k1*x(n-1) k2*x(n-2)。

[0100]

需要强调的是,上述具体实施例仅仅是对本发明的解释,其并不是对本发明的限制,本领域技术人员在阅读完本说明书后可以根据需要对上述实施例做出没有创造性贡献的修改,但只要在本发明的权利要求范围内都受到专利法的保护。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。