transceivers时,所述转换模块采用fifo实现hdmi tx控制器与serdes ip之间的发送数据信号位宽匹配工作。

13.本发明的第二方面,提供了一种hdmi tx控制器的fpga原型验证装置,所述装置包括hdmi tx控制器、fpga芯片上的serdes ip以及用于完成hdmi tx控制器和serdes ip之间接口信号匹配工作的转换模块。

14.本发明的进一步技术方案是:所述hdmi tx控制器对接所述转换模块的接口包含复位信号、系统时钟信号、控制信号、发送数据信号、热插拔检测信号和rx检测信号;所述serdes ip对接所述转换模块的接口有复位信号、时钟信号和发送数据信号。

15.本发明提供的一种hdmi tx控制器的fpga原型验证方法及验证装置,针对传统的eda仿真具有验证速度慢、验证不全面的缺点,通过利用fpga芯片上的serdes ip代替hdmi tx phy,并提供一个用于完成hdmi tx控制器和serdes ip之间接口信号匹配工作的转换模块来实现hdmi tx控制器的fpga原型验证。本发明的有益效果是:可以提高验证的效率和全面性。

附图说明

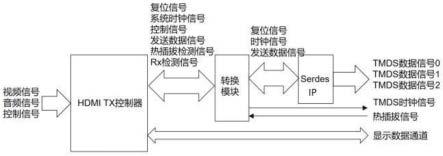

16.图1是本发明实施例中原始hdmi tx模块结构示意图;

17.图2是本发明实施例中hdmi tx控制器的fpga原型验证方法示意图;

18.图3是本发明实施例中hdmi tx控制器的fpga原型验证方法中转换模块实现方法示意图;

19.图4是本发明实施例中实现hdmi tx控制器的fpga原型验证方法的验证平台结构示意图;

20.图5是本发明实施例中实现hdmi tx控制器的fpga原型验证方法的fpga芯片结构示意图。

具体实施方式

21.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅出示了与本发明相关的部分而非全部结构。

22.本发明实施例针对一种hdmi tx控制器的fpga原型验证方法及验证装置,提供了如下实施例:

23.基于本发明的实施例1

24.本发明实施例1针对一种hdmi tx控制器的fpga原型验证方法,所述hdmi tx控制器在原始hdmi tx模块中,如图1所示,原始hdmi tx模块由hdmi tx控制器和hdmi tx phy组成,原始hdmi tx模块通过显示数据通道获取显示器的物理数据,原始hdmi tx模块的输入信号包含视频信号、音频信号、控制信号以及热插拔信号;原始hdmi tx模块的输出信号包含tmds数据通道0、tmds数据通道1、tmds数据通道2和tmds时钟通道共4对差分信号;hdmi tx控制器和hdmi tx phy之间的接口包含复位信号、系统时钟信号、控制信号、发送数据信号、热插拔检测信号和rx检测信号。

25.针对上述hdmi tx控制器的fpga原型验证方法,如图2所示,利用fpga芯片上的

serdes ip代替hdmi tx phy,并提供一个用于完成hdmi tx控制器和serdes ip之间接口信号匹配工作的转换模块。

26.参见图2所示,所述hdmi tx控制器对接所述转换模块的接口包含复位信号、系统时钟信号、控制信号、发送数据信号、热插拔检测信号和rx检测信号;所述serdes ip对接所述转换模块的接口有复位信号、时钟信号和发送数据信号。

27.参见图2-图3所示,所述转换模块将外部输入的热插拔信号直接输出给所述hdmi tx控制器。

28.参见图2-图3所示,所述hdmi tx控制器输出复位信号经所述转换模块接口信号匹配后控制所述serdes ip复位,所述serdes ip复位完成后输出复位完成信号经所述转换模块接口信号匹配后给所述hdmi tx控制器。

29.参见图2-图3所示,当所述hdmi tx控制器输出rx检测使能信号时,serdes ip并没有rx检测功能,所述转换模块收到所述hdmi tx控制器输出的rx检测使能信号后直接把rx检测信号置1输出给所述hdmi tx控制器。

30.所述系统时钟信号包括像素时钟、tmds时钟和像素重复时钟,每个像素的颜色深度为24位、30位、36位或48位中的任意一个。

31.参见图2-图3所示,系统时钟信号包含像素时钟、tmds时钟和像素重复时钟,视频数据的大小可以是24、30、36或48位。默认24位颜色深度的视频以等于像素时钟速率的tmds时钟速率运行。使用相应的更高的tmds时钟速率可以承载更高的颜色深度。可以使用像素重复方案来传输tmds速率低于25mhz的视频格式(例如,480i/ntsc的13.5mhz)。

32.参见图3所示,所述像素时钟、所述tmds时钟和所述像素重复时钟之间的关系为:所述像素重复时钟等于所述像素时钟乘以像素重复数;tmds时钟等于像素颜色深度除以24后再乘以所述像素重复时钟。

33.参见图3所示,当所述serdes ip为ultrascale fpgas transceivers时,所述转换模块采用fifo实现hdmi tx控制器与serdes ip之间的发送数据信号位宽匹配工作。

34.具体实施例中serdes ip以ultrascale fpgas transceivers为例,一路并行数据最低是两个字节20bit,而hdmi tx控制器一个通道的并行数据是10bit,所以转换模块需要完成hdmi tx控制器与serdes ip之间的发送数据信号位宽匹配工作,转换模块采用fifo实现发送数据信号位宽匹配。oddre1和obufds是ultrascale fpga的原语,实现tmds时钟差分信号输出。

35.基于本实施例的hdmi tx控制器的fpga原型验证方法,搭建了一个hdmi tx控制器的fpga原型验证平台来现实该方法,如图4所示,包括fpga芯片、uart单元、线缆驱动器、hdmi插座和电源单元,所述fpga芯片与所述uart单元双向接口连接,所述fpga芯片与所述线缆驱动器接口连接,所述线缆驱动器与所述hdmi插座接口连接,所述电源单元分别为所述fpga芯片、所述uart单元、所述线缆驱动器供电。

36.参考图5,所述fpga芯片包括控制模块、测试图生成模块、测试音频生成模块和hdmi tx模块,所述控制模块分别与所述uart单元、所述hdmi tx模块双向连接,所述控制模块的输出i2c与所述线缆驱动器(图示未显示)连接,所述控制模块与所述测试图生成模块连接,所述hdmi tx模块分别与所述测试图生成模块、测试音频生成模块接口连接,所述hdmi tx模块输出与所述线缆驱动器(图示未显示)相连,其中,所述hdmi tx模块即包括

hdmi tx控制器的fpga原型验证方法实施例1中所述的hdmi tx控制器、serdes ip以及用于hdmi tx控制器和serdes ip之间进行接口信号匹配工作的转换模块。

37.基于本发明的实施例2

38.本发明实施例2所提供的一种hdmi tx控制器的fpga原型验证装置,如图2所示,所述装置包括hdmi tx控制器、fpga芯片上的serdes ip以及用于完成hdmi tx控制器和serdes ip之间接口信号匹配工作的转换模块。

39.进一步的,所述hdmi tx控制器对接所述转换模块的接口包含复位信号、系统时钟信号、控制信号、发送数据信号、热插拔检测信号和rx检测信号;所述serdes ip对接所述转换模块的接口有复位信号、时钟信号和发送数据信号。

40.除了上述模块和部件以外,一种hdmi tx控制器的fpga原型验证装置还可以包括其他部件,然而,由于这些部件与本公开实施例的内容无关,因此在这里省略其图示和描述。

41.一种hdmi tx控制器的fpga原型验证装置的具体工作过程参照上述hdmi tx控制器的fpga原型验证方法实施例1的描述,不再赘述。

42.综合上述各实施例提供的一种hdmi tx控制器的fpga原型验证方法及验证装置,针对传统的eda仿真具有验证速度慢、验证不全面的缺点,通过利用fpga芯片上的serdes ip代替hdmi tx phy,并提供一个用于完成hdmi tx控制器和serdes ip之间接口信号匹配工作的转换模块来实现hdmi tx控制器的fpga原型验证。本发明的有益效果是:可以提高验证的效率和全面性。

43.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。