基于fpga的多路通信信号实现方法

技术领域

1.本发明属于通信技术领域,涉及一种基于fpga的多路通信信号实现方法。

背景技术:

2.在各种类型的专题试验中,为了验证各类通信信号对测控任务的影响,完成测控抗干扰能力指标体系梳理以及装备抗干扰能力评估方法的研究,需要建设速率可变的宽带信号源来进行干扰任务的模拟。当前市面上的发射源功能有限,其中大部分不支持信号速率的任意配置,而且发射宽带较小。但是目前绝大多数的侦查系统需要有很大的瞬时带宽,比如上百兆赫兹,有的甚至可达上千兆赫兹。

3.所以目前速率可任意配置的宽带信号源实现,对于实际的工程应用有较高的研究价值。针对这种大瞬时带宽的侦察系统,在进行功能及性能测试时,要求在瞬时带宽内同时具有对多种不同频率及不同调制类型的信号进行侦察接收的能力。就需要信号发射机也能够输出发射对应的大瞬时带宽及不同频率不同调制类型信号的能力。

技术实现要素:

4.本发明的目的是提供一种基于fpga的多路通信信号实现方法,解决了现有信号发射源不能同时具有对多种不同频率及不同调制类型的信号进行输出的能力。

5.本发明所采用的技术方案是,基于fpga的多路通信信号实现方法,具体包括如下步骤:

6.步骤1,将通信信号分为模拟调制信号与数字调制信号,模拟调制源选择正弦波,在生成码元时数字调制源选择m序列,通过译码模块选择本路需要输出的信号类型及调制源;

7.步骤2,将滤波模块分为两部分插值滤波;

8.步骤3,采用4路并行高速dds产生瞬时带宽;

9.步骤4,在信号生成插值滤波后,为了使信号可以在瞬时带宽内任意分布,需要生成载波信号来混频进行频谱搬移;

10.步骤5,在进行混频后,将生成的5路信号在数字域上进行叠加成一路信号,然后将叠加后的一路信号送入到dac中进行采样输出,这样即可以实现在大瞬时带宽内有多路信号同时输出。

11.本发明的特点还在于:

12.步骤1中,模拟调制信号与数字调制信号的代码均采用verilog及dds实现。

13.步骤2中,两部分插值滤波为:第一部分分为两组插值滤波,将信号频率搬移到180m时钟域,第二部分为4倍插值滤波,将信号搬移到720m时钟域。

14.步骤3中,使用4路并行高速的dds算法,在一个时钟周期内产生4个寻址,即同时查找4个正余弦查找表,即实现4路正交载波同时输出。

15.步骤3中,4路相位累加算法数学公式为:x

n p

=xn 4k,那么可得x

n 7

=x

n 3

4k,其中

n=0,1,2...即一次性得出x

n 4

、x

n 5

、x

n 6

和x

n 7

的值,k为频率控制字。

16.本发明的有益效果是,本发明的方法是信号发射源能同时具有对多种不同频率及不同调制类型的信号进行输出的能力。以fpga为依托,采用并行高速dds算法,以产生大瞬时带宽内任意变化的信号。该方法可靠有效、可扩展性强,能够满足实际的应用需求。

附图说明

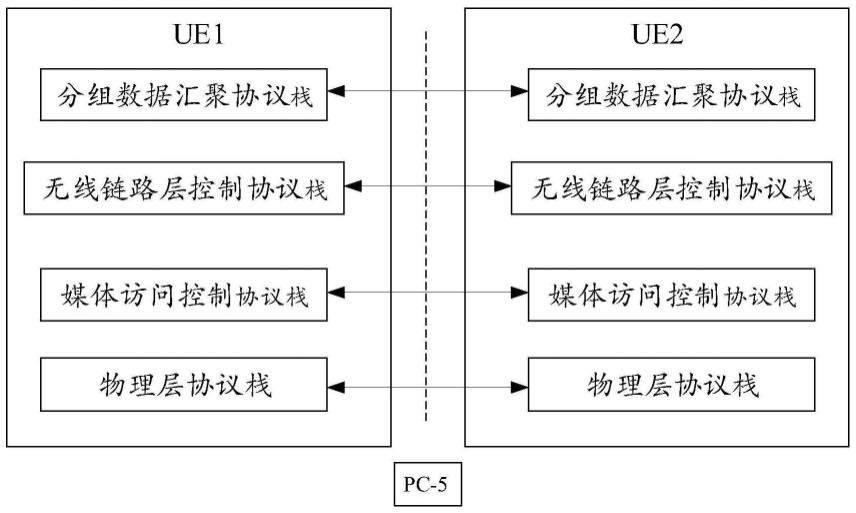

17.图1是本发明基于fpga的多路通信信号实现方法中的信号生成原理框图;

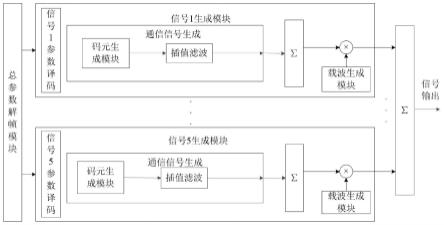

18.图2是本发明基于fpga的多路通信信号实现方法中的信号码元及滤波框图;

19.图3是本发明基于fpga的多路通信信号实现方法中的4路并行iq信号生成原理框图。

具体实施方式

20.下面结合附图和具体实施方式对本发明进行详细说明。

21.本发明基于fpga的多路通信信号实现方法,原理框图如图1所示,信号生成模块主时钟是180mhz,可同时产生共5路通信信号,每路信号采用4路并行实现方式,数据速率为720m,支持的最大带宽为576mhz。对于单路信号生成模块首先产生待调制的码元,一般采用m伪随机序列码,码元生成后根据调制方式进行插值滤波,插值完成后与载波生成模块产生的4路并行载波信号进行混频,混频完成后即可生成单路576mhz带宽的信号,将10路信号进行合路,合路完成后进行增益控制输出即可。具体按照如下步骤实施:

22.步骤1,码元生成如图2,通信信号分为模拟调制信号与数字调制信号,模拟调制源一般选择正弦波,在生成码元时数字调制源一般选择m序列。通过译码模块选择本路需要输出的信号类型及调制源。

23.步骤2,滤波模块分为两部分插值滤波,第一部分分为两组插值滤波,将信号频率搬移到180m时钟域,第二部分为4倍插值滤波,将信号搬移到720m时钟域。

24.步骤3,4路并行高速dds产生。由于受到fpga的工作时钟影响限制,使用自身时钟域无法产生较大的带宽。在采用并行高速dds算法时可产生较大的瞬时带宽满足实际应用普通dds算法为累加器寻址输出,高速并行dds为在一个时钟周期内输出多个寻址地址。

25.步骤4,载波生成与混频。在信号进行插值滤波后,为了使信号可以再大瞬时带宽内任意分布,需要生成载波信号与其混频进行频谱搬移。载波信号在生成时同样采用并行高速dds算法。

26.步骤5,5路信号同时输出,在进行混频后,将生成的5路信号在数字域上进行叠加成一路信号,然后将叠加后的一路信号送入到dac中进行采样输出,这样即可以实现在大瞬时带宽内有多路信号同时输出。

27.模拟调制信号与数字调制信号的代码均采用verilog及dds实现。在数字调制信号生成时其信号频率会存在一定的误差,为了使产生的频率值更加的准确,在码元速率选择时目前只支持几组固定的码元速率,而且在进行第一部分插值滤波时分为两组,而且其插值倍数也只是可选的几组,在码元速率确定时,第一部分的两组滤波的插值倍数也已经确定了。

28.如图3所示的并行高速dds算法的使用,传统dds算法是使用相位累加器进行地址

寻址,将寻址结果送入已经准备好的正余弦查找表中,正余弦查找表中按照地址存储了一个完整周期的正弦和余弦信号幅值。相位累加器计算公式为:x

n 1

=xn k(n=0,1,2...),k为频率控制字。

29.使用4路并行高速的dds算法,可以在一个时钟周期内产生4个寻址,即同时查找4个正余弦查找表,那么就可以实现4路正交载波同时输出,4路相位累加算法数学公式为:x

n p

=xn 4k(p代表信号个数,表示总共有多少路信号可以同时输出),那么可得x

n 7

=x

n 3

4k,其中,n表示累加次数,n=0,1,2...即一次性得出x

n 4

、x

n 5

、x

n 6

和x

n 7

的值。

30.使用4路总计iq采样率为720mhz,系统设计实现时采用2.5倍过采样率,根据采样定理,对于iq正交采样而言,系统瞬时带宽为:720

×

0.8=576mhz,系统可实现的瞬时带宽为576mhz。该并行高速实现方法结构简单、可扩展性强便于工程实现。

31.利用4路并行高速dds算法生成的载波信号频率是在-288mhz~ 288mhz之间,载波信号与生成信号进行混频,实现频谱在带宽内的搬移。

32.本发明基于fpga的多路通信信号实现方法。通过对传统dds算法进行优化,得出了易于fpga实现的多路并行高速算法,并行高速算法可以产生大瞬时带宽内任意变化的正交载频信号。以4路并行高速dds算法为依托,结合verilog在fpga中进行实现,能够输出发射对应的大瞬时带宽及不同频率不同调制类型信号。本发明已在实际工程中成功应用,该算法可靠有效、可扩展性强,能够满足实际的应用需求。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。