1.本文描述的本公开的实施例涉及半导体存储器,更具体地,涉及电子装置、主机的操作方法、存储器模块的操作方法和存储器装置的操作方法。

背景技术:

2.半导体存储器装置归类为易失性存储器装置,其中储存的数据在电源关闭时消失,诸如静态随机存取存储器(random access memory,sram)或动态随机存取存储器(dynamic random access memory,dram),或非易失性存储器装置,其中储存的数据即使在电源关闭时也能保留,诸如闪存装置、相变ram(phase-change ram,pram)、磁性ram(magnetic ram,mram)、电阻ram(resistive ram,rram)或铁电ram(ferroelectric ram,fram)。

3.需要比缓存线单位小的单位(例如,半字节单位(nibble unit)或字节单位)的读取或写入请求。部分写入操作或部分读取操作可以通过使用数据掩码功能来执行。

技术实现要素:

4.本公开的实施例提供电子装置、主机的操作方法、存储器模块的操作方法和存储器装置的操作方法,其能够支持部分写入操作并且最小化功耗。

5.根据一个实施例,具有多个存储器单元的存储器装置的操作方法包括在命令/地址输入间隔期间接收包括部分写入使能信号和多个掩码信号的部分写入命令。在接收到部分写入命令后,通过数据选通线接收数据选通信号。在数据输入间隔期间,通过多个数据线与数据选通信号同步地接收多个数据。在数据写入间隔期间,响应于部分写入使能信号,基于多个掩码信号将多个数据的一部分储存在多个存储器单元中

6.根据一个实施例,包括多个存储器装置的存储器模块的操作方法包括在第一时间接收包括部分写入使能信号和多个掩码信号的部分写入命令。通过与多个存储器装置中的第一存储器装置连接的第一数据选通线切换的第一数据选通信号被接收。在第一时间之后的选通切换间隔期间,通过与多个存储器装置中的第二存储器装置连接的第二数据选通线接收保持在逻辑高电平的第二数据选通信号。在第一时间之后的数据输入间隔期间,通过多个数据线接收多个数据。

7.根据一个实施例,与存储器模块连接的主机的操作方法包括通过将伪数据添加至小于缓存线单位的单位的第一数据,生成第二数据。在命令/地址输入间隔期间,向存储器模块输出包括部分写入使能信号(pwe)和多个掩码信号的部分写入命令。在命令/地址输入间隔之后,在数据选通切换间隔期间,向存储器模块输出数据选通信号。在命令/地址输入间隔之后,在数据输入间隔期间,通过多个数据线向存储器模块输出第二数据。

8.根据一个实施例,电子装置包括存储器接口电路,其通过命令/地址线输出包括部分写入使能信号和多个掩码信号的部分写入命令,并通过多个数据线输出包括伪数据的第一数据。存储器装置通过命令/地址线接收部分写入命令,通过多个数据线接收第一数据,

并基于多个掩码信号将第一数据的一部分储存在存储器单元中。

附图说明

9.通过参照附图详细描述本公开的实施例,本公开的上述和其他目的和特征将变得显而易见。

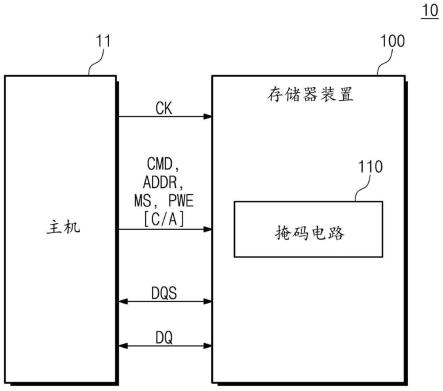

10.图1是示出根据本公开实施例的存储器系统的框图。

11.图2a和图2b是示出图1的存储器系统的操作的图。

12.图3是示出图1的存储器装置的框图。

13.图4是用于描述图1的存储器系统的写入操作的时序图。

14.图5是示出图1的存储器装置的部分写入操作的流程图。

15.图6是用于描述图1的存储器系统的部分写入操作的时序图。

16.图7a是示出图1的存储器装置的写入操作的时序图。图7b和图7c是示出图1的存储器装置的部分写入操作的时序图。

17.图8是用于描述图1的存储器系统的部分写入操作的图。

18.图9是示出根据本公开实施例的存储器系统的框图。

19.图10是用于描述图9的存储器系统的部分写入操作的图。

20.图11a是用于描述图9的每个存储器装置的部分写入操作的流程图。

21.图11b是用于描述图9的存储器系统的部分写入操作的时序图。

22.图12a是用于描述图9的每个存储器装置的部分写入操作的流程图。

23.图12b是用于描述图9的存储器系统的部分写入操作的时序图。

24.图13a和图13b是用于描述根据本公开的存储器系统的部分写入操作的时序图。

25.图14是示出应用了根据本公开的存储器装置的计算系统的框图。

26.图15是示出根据本公开实施例的储存系统的框图。

27.图16是示出图15的掩码控制电路的操作的流程图。

具体实施方式

28.下面将对本公开的实施例进行详细和清楚的描述,以使得本领域技术人员容易实施本公开。

29.图1是示出根据本公开实施例的存储器系统的框图。参照图1,存储器系统10可以包括主机11和存储器装置100。主机11可以向存储器装置100发送地址和命令,以便将数据储存在存储器装置100中或读取储存在存储器装置100中的数据。例如,主机11可以是中央处理单元(central processing unit,cpu)或存储器控制器。

30.在一个实施例中,地址可以包括行地址ra、列地址ca、库地址ba、库组地址bg、芯片标识符(id)“c”等,并且命令可以包括激活命令act、写入命令wr、部分写入命令pwr、读取命令rd、预充电命令pre等。然而,本公开不限于此。例如,地址和命令可以包括各种类型的地址和命令。

31.在一个实施例中,主机11可以向存储器装置100发送时钟信号ck和命令/地址信号c/a。主机11可以通过多个数据线dq与存储器装置100交换数据。主机11可以与存储器装置100交换数据选通信号dqs。

32.作为一个实施例,主机11可以基于诸如双数据速率(double data rate,ddr)接口的高速接口与存储器装置100通信。然而,本公开不限于此。例如,主机11可以基于各种通信接口(诸如通用串行总线(universal serial bus,usb)接口、多媒体卡(multimedia card,mmc)接口、嵌入式mmc(embedded mmc,emmc)接口、外围组件互连(peripheral component interconnection,pci)接口、快速pci-express(pci-express,pci-e)接口、高级技术附件(advanced technology attachment,ata)接口、串行ata接口、并行ata接口、小型计算机小型接口(small computer small interface,scsi)、增强型小磁盘接口(enhanced small disk interface,esdi)、集成驱动电子(integrated drive electronics,ide)接口、火线接口、通用闪存(universal flash storage,ufs)接口和快速非易失性存储器(nonvolatile memory express,nvme)接口)中的至少一种与存储器装置100进行通信。

33.在一个实施例中,主机11可以向存储器装置100发送部分写入请求。主机11可以通过命令/地址信号c/a向存储器装置100发送部分写入命令pwr。在命令/地址输入间隔期间,主机11可以通过命令/地址信号c/a输出部分写入使能信号pwe和多个掩码信号ms至存储器装置100。

34.在主机11的控制下,存储器装置100可以储存从主机11接收到的数据或者可以将储存在其中的数据提供至主机11。例如,存储器装置100可以从主机11接收时钟信号ck。存储器装置100可以通过命令/地址信号c/a从主机11接收命令cmd、地址addr、部分写入使能信号pwe、多个掩码信号ms。响应于接收到的信号,存储器装置100可通过多个数据线dq和数据选通信号dqs向主机11发送数据,或者可以通过多个数据线dq和数据选通信号dqs从主机11接收数据。

35.在一个实施例中,存储器装置100可以包括动态随机存取存储器(dram)。然而,本公开不限于此。例如,存储器装置100可以包括各种存储器装置中的至少一种,诸如静态ram(sram)、动态ram(dram)、同步dram(sdram)、只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)、闪存、相变ram(pram)、磁性ram(mram)、电阻ram(rram)、铁电ram(fram)等。

36.下面,为了容易地描述本公开的技术构思,假设存储器装置100是动态随机存取存储器(dram)并且主机11和存储器装置100基于双数据速率(ddr)接口彼此通信。

37.在一个实施例中,存储器装置100可以包括掩码电路110。掩码电路110可以接收数据选通信号dqs、部分写入使能信号pwe和多个掩码信号ms。基于数据选通信号dqs、部分写入使能信号pwe和多个掩码信号ms,掩码电路110可以将通过多个数据线dq接收的多个数据的一部分储存在多个存储器单元中。

38.如上所述,在命令/地址输入间隔期间,存储器装置100可以通过命令/地址信号c/a从主机11接收部分写入使能信号pwe和多个掩码信号ms。将参考以下附图更全面地描述掩码电路110的配置和操作方法。

39.图2a和图2b是示出图1的存储器系统10的操作的图。缓存线可以指根据主机11向存储器装置100发送的读取或写入请求的最小访问单位。每个缓存线的大小可以是例如32字节或64字节。传统的存储器系统可以以缓存线为单位访问存储器装置。因此,为了更新字节单位的数据,存储器系统可以以缓存线为单位执行读取操作,然后可以以缓存线为单位执行写入操作。

40.假设缓存线的大小为32字节。存储器装置100可以包括第0存储器单元组mcg0至第三十一存储器单元组mcg31。例如,存储器单元组mcg0至mcg31中的每个存储器单元组可以包括8个存储器单元。

41.第一数据dtl和第二数据dt2中的每一个可以包括第0字节数据bd0至第31字节数据bd31。例如,字节数据bd0至bd31中的每一个的大小可以是8位。假设第一数据dt1的第一字节数据bd1的值与第二数据dt2的第一字节数据bd1的值不同,而第一数据dt1的其余字节数据bd0和bd2至bd31的值与第二数据dt2的其余字节数据bd0和bd2至bd31的值相同。

42.主机11可以将与第一地址对应的第一数据dtl储存在存储器装置100中。例如,主机11可以将第0字节数据bd0至第31字节数据bd31的每个值储存在对应的存储器单元组。例如,主机11可以在第0存储器单元组mcg0中储存第0字节数据bd0的值,可以在第一存储器单元组mcg1中储存第一字节数据bd1的值,可以在第二存储器单元组mcg2中储存第二字节数据bd2的值,并且可以在第三存储器单元组mcg3中储存第三字节数据bd3的值。如上所述,其余字节数据bd4至bd31的值储存在其余存储器单元组mcg4至mcg31中,因此,将省略附加的描述以避免冗余。

43.主机11可以更新储存在第一存储器单元组mcgl中的数据。即,主机11可以改变与第一地址相对应的数据。为了更新储存在第一存储器单元组mcg1中的数据,主机11可以读取储存在存储器装置100中的与第一地址相对应的数据。例如,主机11可以从存储器装置100读取储存在第0存储器单元组mcg0至第31存储器单元组mcg31中的第一数据dt1。

44.例如,存储器装置100可以从第0存储器单元组mcg0读取第一数据dt1的第0字节数据bd0的值,可以从第一存储器单元组mcg1读取第一数据dt1的第一字节数据bd1的值,可以从第二存储器单元组mcg2读取第一数据dt1的第二字节数据bd2的值,并且可以从第三存储器单元组mcg3读取第一数据dt1的第三字节数据bd3的值。如上所述,从其余存储器单元组mcg4至mcg31中读取第一数据dt1的其余字节数据bd4至bd31的值,因此将省略附加的描述以避免冗余。

45.主机11可基于第一数据dtl生成第二数据dt2。为了更新储存在第一存储器单元组mcg1中的数据,主机11可以生成与缓存线单位相对应的第二数据dt2。主机11可以通过更新第一数据dt1的第一字节数据bd1生成第二数据dt2。即,第一数据dt1的第一字节数据bd1的值和第二数据dt2的第一字节数据bd1的值可以不同,而第一数据dt1的其余字节数据bd0和bd2至bd31的值可以与第二数据dt2的其余字节数据bd0和bd2至bd31的值相同。

46.主机11可以将第二数据dt2储存在存储器装置100中。例如,主机11可以向存储器装置100发送写入请求和第二数据dt2。写入请求可以包括写入命令和第一地址。存储器装置100可以响应于写入请求将第二数据dt2储存在多个存储器单元中。存储器装置100可以将第二数据dt2的第0字节数据bd0的值储存在第0存储器单元组mcg0中,可以将更新的第二数据dt2的第一字节数据bd1的值储存在第一存储器单元组mcg1中,可以将第二数据dt2的第二字节数据bd2的值储存在第二存储器单元组mcg2中,并且可以将第二数据dt2的第三字节数据bd3的值储存在第三存储器单元组mcg3中。如上所述,第二数据dt2的其余字节数据bd4至bd31的值储存在其余存储器单元组mcg4至mcg31中,因此将省略附加的描述以避免冗余。

47.如上所述,为了更新储存在第一存储器单元组mcgl中的字节单位的数据,主机11

可以从存储器装置100读取与缓存线单位相对应的第一数据dtl,并且可以储存或写入存储器装置100中的与缓存线单位相对应的第二数据dt2。

48.存储器装置可以通过数据掩码(data mask,dm)功能dm支持部分写入操作。根据ddr 4.0规范的协议,x8/x16存储器装置可以通过dm_n/dbi_n/tdqs_t信号执行数据掩码功能、数据总线反转(data bus inversion,dbi)功能和tdqs功能。数据掩码功能、数据总线反转功能和tdqs功能可以通过设置模式寄存器来使能或禁用。然而,x4存储器装置无法使用dm_n/dbi_n/tdqs_t信号。x4存储器装置不支持数据掩码功能。

49.如此,为了更新x4存储器装置中储存的小于缓存线单位的单位(例如,半字节单位或字节单位)的数据,存储器系统需要从x4存储器装置读取与缓存线单位相对应的数据并在x4存储器装置中写入与缓存线单位相对应的数据。

50.根据本公开实施例的存储器装置可以执行部分写入操作而无论dq线的数量。存储器装置100可以通过使用命令/地址线接收部分写入使能信号和多个掩码信号而不是dm_n/dbi_n/tdqs_t信号。

51.使用数据掩码功能的存储器装置可以在数据输入间隔期间从主机接收数据掩码信号。相比之下,根据本公开实施例的存储器装置可以在命令/地址输入间隔期间接收多个掩码信号。

52.将参照图2b描述更新与字节单位相对应的数据的方法。与图2a相比,根据本公开实施例的存储器系统10可以执行部分写入操作。例如,存储器系统10可以将其单位小于缓存线单位的数据写入存储器装置100中。由此,为了执行更新操作,存储器系统10可以从存储器装置100不读取与缓存线单位相对应的第一数据dt1。

53.例如,主机11可以更新储存在第一存储器单元组mcgl中的数据。通过部分写入操作,主机11可以将小于缓存线单位的单位的数据写入存储器装置100中。

54.第三数据dt3可以包括第0字节数据bd0至第三十一字节数据bd31。假设第一字节数据bd1具有有效值并且其余字节数据bd0和bd2至bd31具有伪值。

55.主机11可以生成第三数据dt3。第三数据dt3可以包括具有有效值的第一字节数据bd1以及均具有伪值的第0字节数据bd0和第二字节数据bd2至第三十一字节数据bd31。即,与第0存储器单元组mcg0和第二存储器单元组mcg2至第三十一存储器单元组mcg31相对应的数据可以是伪数据,而与第一存储器单元组mcg1相对应的数据可以是更新的第一字节数据bd1。例如,伪数据可以指给定的数据模式或随机数据模式。

56.主机11可以向存储器装置100发送部分写入请求和第三数据dt3。例如,部分写入请求可以包括部分写入命令和地址。

57.存储器装置100可以接收部分写入请求和第三数据dt3。存储器装置100可以响应于部分写入请求执行部分写入操作。存储器装置100可以在第一存储器单元组mcg1中仅写入除了伪数据之外的第一字节数据bd1。

58.如上所述,根据本公开实施例的存储器系统10可以执行部分写入操作。由此,为了更新比缓存线单位更小的单位的数据,存储器系统10可以从存储器装置100不读取与缓存线单位相对应的数据。主机11可以将更新的字节数据和伪数据发送至存储器装置100使得比缓存线单位更小的单位的数据即更新的字节数据被写入存储器装置100中。

59.图3是示出图1的存储器装置的框图。参照图1和图3,存储器装置100可以包括掩码

电路110、存储器单元阵列120、解码器130、写入驱动器和感测放大器140、命令/地址解码器150和缓冲器电路161至164。

60.存储器单元阵列120可以包括与字线(wordlines)(未示出)和位线(bitlines)(未示出)连接的多个存储器单元。在解码器130和写入驱动器和感测放大器140的控制下,多个存储器单元中的每一个可以被配置为储存数据或输出储存的数据。

61.解码器130可以控制被包括在存储器单元阵列120中的多个存储器单元。解码器130可以基于从命令/地址解码器150接收的信息(例如,解码结果)控制多个存储器单元。例如,解码器130可以对行地址ra进行解码以使能与行地址ra相对应的字线。解码器130可以对列地址ca进行解码以使能与列地址ca相对应的列选择线csl。

62.在一个实施例中,解码器130可以从掩码电路110接收列控制信号c_ctrl。解码器130可以响应于列控制信号c_ctrl控制列选择线csl。解码器130可以响应于列控制信号c_ctrl将列选择线csl设置为逻辑低“l”,使得输入数据的全部或部分不储存在存储器单元阵列120中。解码器130可以响应于列控制信号c_ctrl将列选择线csl设置为逻辑高“h”,使得输入数据的全部或部分储存在存储器单元阵列120中。

63.写入驱动器和感测放大器140可以被配置为在被包括在存储器单元阵列120中的多个存储器单元中写入数据或者输出储存在被包括在存储器单元阵列120中的多个存储器单元中的数据。

64.命令/地址解码器150可以对通过命令/地址缓冲器162接收的命令/地址信号c/a进行解码。命令/地址解码器150可以向解码器130提供解码结果。命令/地址解码器150可以解码时钟使能信号cke、芯片选择信号(chip select signal)cs_n、激活信号act_n、行地址选通(row address strobe,ras)信号ras_n、列地址选通(column address strobe,cas)信号cas_n、写入使能信号we_n和部分写入使能信号pwe以识别部分写入命令pwr。

65.部分写入命令pwr可以通过写入命令wr和部分写入使能信号pwe限定。基于对时钟使能信号cke、芯片选择信号cs_n、激活信号act_n、ras信号ras_n、cas信号cas_n和写入使能信号we_n的解码结果,命令/地址解码器150可以识别写入命令wr并且可以识别指示使能状态的部分写入使能信号pwe。因此,命令/地址解码器150可以识别部分写入命令pwr。

66.命令/地址解码器150可以响应于时钟使能信号cke、芯片选择信号cs_n、激活信号act_n、ras信号ras_n、cas信号cas_n、写入使能信号we_n和部分写入使能信号pwe,向掩码电路110输出掩码使能信号me和多个掩码信号ms。即,当接收到部分写入命令pwr时,命令/地址解码器150可以提供掩码使能信号me和多个掩码信号ms至掩码电路110。掩码使能信号me可以是用于使能内部掩码功能以便执行部分写入操作的信号。

67.例如,掩码使能信号me可以具有指示禁用状态的第一逻辑值(例如,逻辑低“l”)或指示使能状态的第二逻辑值(例如,逻辑高“h”)。由此,当部分写入使能信号pwe指示使能状态时,命令/地址解码器150可将掩码使能信号me设置为逻辑高“h”。由此,当部分写入使能信号pwe指示禁用状态时,命令/地址解码器150可将掩码使能信号me设置为逻辑低“l”。

68.时钟缓冲器161可以从主机11接收时钟信号ck。存储器装置100可以基于接收到的时钟信号ck进行操作。

69.命令/地址缓冲器162可以通过命令/地址线从主机11接收命令/地址信号c/a。命令/地址信号c/a可以通过时钟使能信号cke、芯片选择信号cs_n、激活信号act_n、ras信号

ras_n、cas信号cas_n、写入使能信号we_n、库组地址线bg0和bg1、库地址线ba0和ba1、芯片标识符线c0至c2、第十二地址线a12、第十一地址线a11、第十三地址线a13和第十七地址线a17、第十地址线a10以及第0地址线a0至第九地址线a9。

70.例如,存储器装置100可以通过库组地址线bg0和bg1从主机11接收库组地址bg,可以通过库地址线ba0和ba1从主机11接收库地址ba,并且可以通过第0地址线a0至第九地址线a9从主机11接收列地址ca。

71.在一个实施例中,命令/地址缓冲器162可以通过第十二地址线a12接收部分写入使能信号pwe。命令/地址缓冲器162可以通过第0地址线a0接收第0掩码信号ms0,可以通过第一地址线a1接收第一掩码信号ms1,可以通过第二地址线a2接收第二掩码信号ms2,可以通过第十一地址线a11接收第三掩码信号ms3,可以通过第十三地址线a13接收第四掩码信号ms4,可以通过第0芯片标识符线c0接收第五掩码信号ms5,可以通过第一芯片标识符线c1接收第六掩码信号ms6,并且可以通过第二芯片标识符线c2接收第七掩码信号ms7。

72.命令/地址缓冲器162可以将由此接收的命令/地址信号c/a提供至命令/地址解码器150。

73.dqs缓冲器163可以通过数据选通线从主机11接收数据选通信号dqs。存储器装置100可以通过使用数据选通信号dqs采样、捕获或并行化数据来检测输入数据。dq缓冲器164可以通过多个数据线dq从主机11接收输入数据。dq缓冲器164可以向掩码电路110提供输入数据。例如,输入数据din可以指示在数据输入间隔期间由存储器装置100接收的数据。

74.在一个实施例中,在突发长度为8(bl8)的情况下,dq缓冲器164可以接收输入数据din。输入数据din可以包括在第0突发长度期间传输至多个数据线dq的第0输入数据din_0、在第一突发长度期间传输至多个数据线dq的第一输入数据din_1、在第二突发长度期间传输至多个数据线dq的第二输入数据din_2,以及在第三突发长度期间传输至多个数据线dq的第三输入数据din_3。其余输入数据din_4至din_7具有与上述相似的结构,因此将省略附加的描述以避免冗余。

75.掩码电路110可以从命令/地址解码器150接收掩码使能信号me和多个掩码信号ms。掩码电路110可以从dqs缓冲器163接收数据选通信号dqs。掩码电路110可以从dq缓冲器164接收通过多个数据线dq接收的输入数据din。掩码电路110可以通过全局输入/输出线gio将输入数据din提供至写入驱动器和感测放大器140。

76.掩码电路110可以响应于掩码使能信号me执行部分写入操作或内部掩码操作。部分写入操作是指执行掩码操作使得在写入操作中数据不被写入存储器单元阵列120的部分存储器单元组(或块)中的操作。

77.在一个实施例中,当掩码使能信号me指示使能状态时,掩码电路110可以基于多个掩码信号ms0至ms7和数据选通信号dqs执行部分写入操作。例如,掩码电路110可以不基于多个掩码信号ms0至ms7将输入数据din的一部分传输至写入驱动器和感测放大器140。可选地,掩码电路110可基于多个掩码信号ms0至ms7来控制列控制信号c_ctrl,使得输入数据din的一部分不储存在存储器单元中。掩码电路110可以向解码器130输出列控制信号c_ctrl。

78.在一个实施例中,当部分写入使能信号pwe指示使能状态时,掩码电路110可确定数据选通信号dqs在选通切换间隔期间是否保持逻辑高“h”。当数据选通信号dqs在选通切

换间隔期间保持逻辑高“h”时,掩码电路110可以不将全部输入数据din传输至写入驱动器和感测放大器140。可选地,掩码电路110可以控制列控制信号c_ctrl使得全部输入数据din不储存在存储器单元中。

79.图4是用于描述图1的存储器系统的写入操作的时序图。将参考图1和图4描述写入操作。存储器系统10可以基于图4所示的时序图执行写入操作。

80.在第一时间tl(或在时钟信号ck_c的第一上升沿),主机11可以向存储器装置100发送命令和地址。主机11可以通过命令信号(例如,cmd)发送写入命令wr。主机11可以通过库组地址线(例如,bg addr)发送库组地址bg。主机11可以通过地址线(例如,addr)发送库地址ba和列地址ca。

81.在一个实施例中,在从发送写入命令和地址的时间tl开始经过写入延迟wl之后,可以通过数据线dq(例如,dq0-dq3)与数据选通信号dqs切换同步地发送输入数据din。

82.在一个实施例中,在命令/地址输入间隔tl期间,存储器装置100可以从主机11接收命令和地址。在从发送写入命令和地址的时间tl开始经过写入延迟wl之后,存储器装置100可以在数据输入间隔t2期间从主机11接收输入数据din。

83.在一个实施例中,下面的表1和表2示出了基于ddr 4.0规范的协议的命令真值表的示例。在表1中,“h”指示高电平或逻辑高,并且“l”指示低电平或逻辑低。在表2中,“v”指示定义为“h”和“l”之一的特定电平。

84.表1

[0085][0086]

可以通过如表1所示的控制时钟使能信号cke、芯片选择信号cs_n、激活信号act_n、ras信号ras_n、cas信号cas_n和写入使能信号we_n发送写入命令wr。例如,在第一时间t1,主机11可以通过将在上一周期和当前周期的时钟使能信号cke设置为逻辑高“h”,将芯片选择信号cs_n设置为逻辑低“l”,将激活信号act_n设置为逻辑高“h”,将ras信号ras_n设置为逻辑高“h”,将cas信号cas_n设置为逻辑低“l”,将写入使能信号we_n设置为逻辑低“l”来发送写入命令wr。

[0087]

表2

[0088][0089]

由上表2可知,在第一时间tl,主机11可以通过第0库组地址线bg0和第一库组地址线bg1向存储器装置100发送库组地址bg,并且可以通过第0库地址线ba0和第一库地址线ba1向存储器装置100发送库地址ba。主机11可以通过第十二地址线a12向存储器装置100发送突发斩波信号(burst chopping signal)bc。突发斩波信号bc可以指示未使用的预先或单独限定的突发长度的一部分。主机11可以通过第十地址线a10发送自动预充电信号ap。主

机11可通过第0地址线a0至第9地址线a9发送列地址ca。在第一时间t1,主机11可以将第0芯片标识符线c0至第二芯片标识符线c2、第十至第十三地址线a10、a11、a12、a13和第十七地址线a17设置为与逻辑高“h”或逻辑低“l”之一的电平。

[0090]

图5是示出图1的存储器装置的部分写入操作的流程图。参照图1和图5,在操作s110中,存储器装置100可以从主机11接收包括部分写入使能信号pwe和多个掩码信号ms的部分写入命令pwr。例如,在命令/地址输入间隔期间,存储器装置100可以通过命令/地址信号c/a接收部分写入命令pwr。

[0091]

在操作s120中,存储器装置100可以在选通切换间隔期间接收数据选通信号dqs。在数据输入间隔期间,存储器装置100可以通过多个数据线dq接收数据。

[0092]

在操作s130中,存储器装置100可以基于多个掩码信号ms使能列选择线。例如,当掩码信号指示禁用状态时,存储器装置100可以使能与对应于掩码信号的输入数据的列地址相对应的列选择线。当掩码信号指示使能状态时,存储器装置100可以禁用与对应于掩码信号的输入数据的列地址相对应的列选择线。

[0093]

在操作s140中,存储器装置100可以基于列选择线csl将数据储存在多个存储器单元中。例如,当列选择线指示使能状态时,存储器装置100可以将与列选择线相对应的输入数据储存在存储器单元中。例如,当列选择线指示禁用状态时,存储器装置100可以不将与列选择线相对应的输入数据储存在存储器单元中。即,在数据写入间隔期间,存储器装置100响应于部分写入使能信号pwe,基于多个掩码信号ms将输入数据的一部分储存在存储器单元中(例如s130、s140)。

[0094]

如上所述,存储器装置100可以通过命令/地址信号c/a接收多个掩码信号ms而不是单独的数据掩码信号dm_n。存储器装置100可以在命令/地址输入间隔期间而不是在数据输入间隔期间接收多个掩码信号ms。

[0095]

图6是用于描述图1的存储器系统的部分写入操作的时序图。在一个实施例中,存储器系统10可以基于图6所示的时序图执行部分写入操作。在第一时间t1(或在时钟信号ck_c的第一个上升沿),主机11可以向存储器装置100发送命令和地址。主机11可以通过命令线(例如,cmd)发送部分写入命令pwr。主机11可以通过库组地址线(例如,bg addr)发送库组地址bg。主机11可以通过地址线(例如,addr)发送库地址ba、列地址ca、部分写入使能信号pwe和多个掩码信号ms。

[0096]

在一个实施例中,在从发送部分写入命令pwr和地址的时间tl开始经过写入延迟wl之后,可以通过数据线dq(例如,dq0-dq3)与数据选通信号dqs切换同步地发送输入数据。

[0097]

在一个实施例中,在命令/地址输入间隔tl期间,存储器装置100可以从主机11接收部分写入命令pwr和地址。在从发送部分写入命令pwr和地址的时间tl开始经过写入延迟wl之后,存储器装置100可以在数据输入间隔t2期间从主机11接收输入数据din_0至din_7。

[0098]

主机11可以通过地址线发送部分写入使能信号pwe和多个掩码信号ms0至ms7。下面的表3和表4显示了基于ddr 4.0规范的协议的部分写入命令pwr的命令真值表示例。在表3中,“h”指示高电平或逻辑高,并且“l”指示低电平或逻辑低。在表4中,“v”指示定义为“h”和“l”之一的特定电平。

[0099]

表1

[0100][0101]

主机11可以通过第十二地址线a12向存储器装置100发送部分写入使能信号pwe。可以通过如表3所示的控制时钟使能信号cke、芯片选择信号cs_n、激活信号act_n、ras信号ras_n、cas信号cas_n、写入使能信号we_n和部分写入使能信号pwe来发送部分写入命令pwr。例如,在第一时间t1,主机11可以通过将在上一周期和当前周期的时钟使能信号cke设置为逻辑高“h”,将芯片选择信号cs_n设置为逻辑低“l”,将激活信号act_n设置为逻辑高“h”,将ras信号ras_n设置为逻辑高“h”,将cas信号cas_n设置为逻辑低“l”,将写入使能信号we_n设置为逻辑低“l”,并将部分写入使能信号pwe设置为逻辑高“h”来发送部分写入命令pwr。

[0102]

如上所述,可以依据通过第十二地址线a12接收的部分写入使能信号pwe区分写入命令wr和部分写入命令pwr。在本公开中,假设部分写入使能信号pwe设置为逻辑高“h”的情况指示部分写入命令pwr。然而,本公开不限于此。例如,部分写入使能信号pwe设置为逻辑低“l”的情况可以依据实施方式指示部分写入命令pwr。

[0103]

表2

[0104][0105]

在第一时间tl,主机11可以通过第0库组地址线bg0和第一库组地址线bg1向存储器装置100发送库组地址bg,并且可以通过第0库地址线ba0和第一库地址线ba1向存储器装置100发送库地址ba。主机11可以通过第十地址线a10发送自动预充电信号ap。主机11可以通过第三地址线a3至第九地址线a9发送列地址ca。在第一时间t1,主机11可以将第十地址线a10和第十七地址线a17设置为与逻辑高“h”或逻辑低“l”之一相对应的电平。主机11可以通过第0地址线a0向存储器装置100发送第0掩码信号ms0,可以通过第一地址线a1向存储器装置100发送第一掩码信号ms1,可以通过第二地址线a2向存储器装置100发送第二掩码信号ms2,可以通过第十一地址线a11向存储器装置100发送第三掩码信号ms3,可以通过第十三地址线a13向存储器装置100发送第四掩码信号ms4,可以通过第0芯片标识符线c0向存储器装置100发送第五掩码信号ms5,可以通过第一芯片标识符线c1向存储器装置100发送第六掩码信号ms6,并且可以通过第二芯片标识符线c2向存储器装置100发送第七掩码信号ms7。

[0106]

如上所述,根据本公开实施例的存储器系统10可以通过备用线(例如,芯片标识符线c0至c2和地址线a0至a2、a11、a12和a13)执行部分写入操作。即,存储器系统10可以通过备用线发送部分写入使能信号pwe和多个掩码信号ms0至ms7。

[0107]

在一个实施例中,多个掩码信号ms可以指示输入数据din的有效数据的位置。例如,多个掩码信号ms中的每一个可以是指示是否掩码或阻挡输入数据din的对应数据的信

号。多个掩码信号ms中的每一个可以是指示是否在存储器装置100中储存或写入输入数据din的对应数据的信号。多个掩码信号ms中的每一个可以是指示输入数据din的对应数据为有效数据或伪数据的信号。

[0108]

当掩码信号具有指示禁用状态的第一逻辑值(例,如逻辑低“l”)时,存储器装置100可以在存储器单元中储存与掩码信号相对应的输入数据。当掩码信号具有指示使能状态的第二逻辑值(例如,逻辑高“h”)时,存储器装置100可以在存储器单元中不储存与掩码信号相对应的输入数据。可选地,当掩码信号指示禁用状态时,与掩码信号相对应的输入数据可以是有效的。当掩码信号指示使能状态时,与掩码信号相对应的输入数据可能无效(即,与掩码信号相对应的输入数据可能是伪数据)。

[0109]

在命令/地址输入间隔tl期间,主机11可以将部分写入使能信号pwe设置为逻辑高“h”,可以将第0掩码信号ms0设置为逻辑低“l”,并且可以将第一掩码信号ms1至第七掩码信号ms7设置为逻辑高“h”。在这种情况下,因为部分写入使能信号pwe指示使能状态并且第0掩码信号ms0指示禁用状态,所以存储器装置100可以将与第0掩码信号ms0相对应的输入数据din_0储存在多个存储器单元中。因为第一掩码信号ms1至第七掩码信号ms7指示使能状态,所以存储器装置100可以在多个存储器单元中不储存与第一掩码信号ms1至第七掩码信号ms7相对应的输入数据din_1至din_7。

[0110]

图7a是示出图1的存储器装置的写入操作的时序图。图7b和图7c是示出图1的存储器装置的部分写入操作的时序图。假设突发长度bl为8。参照图3和图7a至图7c,存储器装置100可以响应于写入命令wr将全部输入数据储存在存储器单元阵列120中。存储器装置100可以响应于部分写入命令pwr将输入数据的全部或部分储存在存储器单元阵列120中。

[0111]

如图7a所示,在写入操作(wr)中,掩码电路110可以允许全部输入数据din_0至din_7储存在存储器单元阵列120中。掩码电路110可以通过全局输入/输出线gio将输入数据din_0至din_7传输至写入驱动器和感测放大器140。掩码电路110可以控制列控制信号c_ctrl,从而使能与输入数据din_0至din_7中的每一个的列地址相对应的列选择线csl。因为使能了与输入数据din_0至din_7中的每一个的列地址相对应的列选择线csl,所以输入数据din_0至din_7均可以储存在存储器单元阵列120中。

[0112]

掩码电路110可以基于掩码使能信号me、多个掩码信号ms和数据选通信号dqs控制列控制信号c_ctrl,从而执行部分写入操作。掩码电路110可以通过全局输入/输出线gio基于掩码使能信号me、多个掩码信号ms和数据选通信号dqs将输入数据din的全部或部分传输至写入驱动器和感测放大器140。

[0113]

在部分写入操作(pwr)中,假设在命令/地址输入期间tl,部分写入使能信号pwe为逻辑高“h”,第0掩码信号ms0为逻辑高“h”,第一掩码信号ms1至第七掩码信号ms7为逻辑低“l”。

[0114]

与图7a类似,如图7b所示,掩码电路110可以通过全局输入/输出线gio将全部输入数据din_0至din_7传输至写入驱动器和感测放大器140。然而,掩码电路110可以控制列控制信号c_ctrl,使得与第0输入数据din_0的列地址相对应的列选择线csl禁用,与第一输入数据din_1的列地址相对应的列选择线csl使能,与第二输入数据din_2的列地址相对应的列选择线csl禁用,与第三输入数据din_3的列地址相对应的列选择线csl禁用,与第四输入数据din_4的列地址相对应的列选择线csl禁用,与第五输入数据din_5的列地址相对应的

列选择线csl禁用,与第六输入数据din_6的列地址相对应的列选择线csl禁用,与第七输入数据din_7的列地址相对应的列选择线csl禁用。

[0115]

因为仅与第一输入数据din_1的列地址相对应的列选择线csl使能,所以第一输入数据din_1可以储存在存储器单元阵列120中,而第0输入数据din_0和第二输入数据din_2至第七输入数据din_7可以不储存在存储器单元阵列120中。

[0116]

如图7c所示,掩码电路110可以通过全局输入/输出线gio仅将第一输入数据din_1传输至写入驱动器和感测放大器140。掩码电路110可以通过全局输入/输出线gio将具有伪值的第0输入数据din_0和第二输入数据din_2至第七输入数据din_7不传输至写入驱动器和感测放大器140。

[0117]

掩码电路110可以控制列控制信号c_ctrl,使得与第0输入数据din_0的列地址相对应的列选择线csl禁用,与第一输入数据din_1的列地址相对应的列选择线csl使能,与第二输入数据din_2的列地址相对应的列选择线csl禁用,与第三输入数据din_3的列地址相对应的列选择线csl禁用,与第四输入数据din_4的列地址相对应的列选择线csl禁用,与第五输入数据din_5的列地址相对应的列选择线csl禁用,与第六输入数据din_6的列地址相对应的列选择线csl禁用,与第七输入数据din_7的列地址相对应的列选择线csl禁用。

[0118]

因为仅与第一输入数据din_1的列地址相对应的列选择线csl使能,所以第一输入数据din_1可以储存在存储器单元阵列120中,而第0输入数据din_0和第二输入数据din_2至第七输入数据din_7可以不储存在存储器单元阵列120中。

[0119]

如上所述,在部分写入操作中,存储器装置100可以控制列选择线csl,使得输入数据din的一部分不储存在存储器单元阵列120中。因此,存储器装置100可以降低将第0输入数据din_0和第二输入数据din_2至第七输入数据din_7储存在存储器单元阵列120中所需的功耗。

[0120]

图8是用于描述图1的存储器系统的部分写入操作的图。将参考图8描述突发长度bl与多个掩码信号ms之间的关系。分别与多个掩码信号ms相对应的输入数据的数量可根据突发长度bl而改变。

[0121]

在一个实施例中,掩码信号ms的数量可以根据突发长度bl而改变。例如,当突发长度bl为4时,多个掩码信号ms可以包括第0掩码信号ms0至第三掩码信号ms3。当突发长度bl是8或16时,多个掩码信号ms可以包括第0掩码信号ms0至第七掩码信号ms7。

[0122]

在一个实施例中,与掩码信号相对应的输入数据的大小可以根据突发长度bl而改变。例如,当突发长度bl为4或8时,与掩码信号相对应的输入数据的大小可以与在一个突发长度期间输入的数据的大小相对应。当突发长度bl为16时,与掩码信号相对应的输入数据的大小可以与在2个突发长度期间输入的数据的大小相对应。

[0123]

当突发长度为4(bl4)时,输入数据din可以包括第0输入数据din_0至第三输入数据din_3。输入数据din可以包括在第0突发长度期间传输至多个数据线dq的第0输入数据din_0、在第一突发长度期间传输至多个数据线dq的第一输入数据din_1、在第二突发长度期间传输至多个数据线dq的第二输入数据din_2以及在第三突发长度期间传输至多个数据线dq的第三输入数据din_3。

[0124]

第0掩码信号ms0可与第0输入数据din_0相对应,第一掩码信号ms1可与第一输入数据din_1相对应,第二掩码信号ms2可与第二输入数据din_2相对应,以及第三掩码信号

ms3可与第三输入数据din_3相对应。

[0125]

当突发长度为8(bl8)时,输入数据din可以包括第0输入数据din_0至第七输入数据din_7。输入数据din可以包括在第0突发长度期间传输至多个数据线dq的第0输入数据din_0、在第一突发长度期间传输至多个数据线dq的第一输入数据din_1、在第二突发长度期间传输至多个数据线dq的第二输入数据din_2、在第三突发长度期间传输至多个数据线dq的第三输入数据din_3、在第四突发长度期间传输至多个数据线dq的第四输入数据din_4、在第五突发长度期间传输至多个数据线dq的第五输入数据din_5、在第六突发长度期间传输至多个数据线dq的第六输入数据din_6、以及在第七突发长度期间传输至多个数据线dq的第七输入数据din_7。

[0126]

第0掩码信号ms0可以与第0输入数据din_0相对应,第一掩码信号ms1可以与第一输入数据din_1相对应,第二掩码信号ms2可以与第二输入数据din_2相对应,第三掩码信号ms3可以与第三输入数据din_3相对应,第四掩码信号ms4可以与第四输入数据din_4相对应,第五掩码信号ms5可以与第五输入数据din_5相对应,第六掩码信号ms6可以与第六输入数据din_6相对应,以及第七掩码信号ms7可以与第七输入数据din_7相对应。

[0127]

当突发长度为16(bl16)时,输入数据din可以包括第0数据din_0至第15数据din_15。输入数据din可以包括在第0突发长度期间传输至多个数据线dq的第0输入数据din_0、在第一突发长度期间传输至多个数据线dq的第一输入数据din_1、在第二突发长度期间传输至多个数据线dq的第二输入数据din_2,以及在第三突发长度期间传输至多个数据线dq的第三输入数据din_3。其余输入数据din_4至din_15具有与上述相似的结构,因此将省略附加的描述以避免冗余。

[0128]

第0掩码信号ms0可以与第0输入数据din_0和第一输入数据din_1相对应,第一掩码信号msl可以与第二数据din_2和第三输入数据din_3相对应,第二掩码信号ms2可以与第四输入数据din_4和第五输入数据din_5相对应,第三掩码信号ms3可以与第六输入数据din_6和第七输入数据din_7相对应,第四掩码信号ms4可以与第八输入数据din_8和第九输入数据din_9相对应,第五掩码信号ms5可以与第十输入数据din_10和第十一输入数据din_11相对应,第六掩码信号ms6可以与第十二输入数据din_12和第十三输入数据din_13相对应,以及第七掩码信号ms7可以与第十四输入数据din_14和第十五输入数据din_15相对应。

[0129]

如上所述,掩码信号的配置和与掩码信号的配置对应的输入数据的数量可以根据突发长度而改变。在本公开中,描述了突发长度为4、8和16的示例,但是本公开不限于此。例如,突发长度可以增加或减少,并且分别与掩码信号相对应的输入数据的数量可以根据突发长度而改变。

[0130]

图9是示出根据本公开实施例的存储器系统的框图。参照图9,存储器系统1000可包括主机1100和存储器模块1200。存储器模块1200可包括寄存器时钟驱动器(register clock driver,rcd)1210和第0存储器装置1220至第七存储器装置1227。为了便于描述,将省略与上述组件相关联的附加描述以避免冗余。

[0131]

rcd 1210可以从外部装置(例如主机或存储器控制器)接收命令/地址信号c/a和时钟信号ck。rcd 1210可以基于接收到的信号向多个存储器装置1220至1227提供命令/地址信号c/a。

[0132]

多个存储器装置1220至1227中的每一个可以发送/接收对应的数据选通信号dqs。

例如,第0存储器装置1220可以通过第0数据选通线与主机1100交换第0数据选通信号dqs0。第一存储器装置1221可以通过第一数据选通线与主机1100交换第一数据选通信号dqs1。第二存储器装置1222可以通过第二数据选通线与主机1100交换第二数据选通信号dqs2。第三存储器装置1223可以通过第三数据选通线与主机1100交换第三数据选通信号dqs3。第四存储器装置1224可以通过第四数据选通线与主机1100交换第四数据选通信号dqs4。第五存储器装置1225可以通过第五数据选通线与主机1100交换第五数据选通信号dqs5。第六存储器装置1226可以通过第六数据选通线与主机1100交换第六数据选通信号dqs6。第七存储器装置1227可以通过第七数据选通线与主机1100交换第七数据选通信号dqs7。

[0133]

多个存储器装置1220至1227中的每一个可以通过对应的数据线与主机1100交换数据。假设多个存储器装置1220至1227中的每一个通过4个数据线与主机1100连接。然而,本公开不限于此。例如,与多个存储器装置1220至1227中的每一个连接的数据线的数量依据实施方式而减少或改变。

[0134]

例如,第0存储器装置1220可以通过第0数据线dq0至第三数据线dq3与主机1100交换数据。第一存储器装置1221可以通过第四数据线dq4至第七数据线dq7与主机1100交换数据。第二存储器装置1222可以通过第八数据线dq8至第十一数据线dq11与主机1100交换数据。第三存储器装置1223可以通过第十二数据线dq12至第十五数据线dq15与主机1100交换数据。第四存储器装置1224可以通过第十六数据线dq16至第十九数据线dq19与主机1100交换数据。第五存储器装置1225可以通过第二十数据线dq20至第二十三数据线dq23与主机1100交换数据。第六存储器装置1226可以通过第二十四数据线dq24至第二十七数据线dq27与主机1100交换数据。第七存储器装置1227可以通过第二十八数据线dq28至第三十一数据线dq31与主机1100交换数据。

[0135]

在一个实施例中,多个存储器装置1220至1227中的每一个可以包括参照图1至图8描述的掩码电路110。即,多个存储器装置1220至1227中的每一个均可以执行部分写入操作。

[0136]

在一个实施例中,图9中所示的存储器模块1200可以为寄存式dimm(rdimm)。然而,本公开不限于此。例如,存储器模块1200可以是负载降低的双列直插式存储器模块(load reduced dual in-line memory module,lr-dimm)的形状因素,其还包括多个数据缓冲器,多个数据缓冲器通过存储器数据线分别与多个存储器装置1220至1227连接。可以通过多个数据线dq与外部装置(例如,主机或存储器控制器)交换数据。

[0137]

例如,多个存储器装置1220至1227可以通过存储器数据线分别与多个数据缓冲器连接。多个数据缓冲器中的每一个可以与对应的数据线连接并且可以通过数据线与外部装置交换数据。多个数据缓冲器中的每一个可以通过存储器数据线中的每个将接收到的数据传输至相应的存储器装置。

[0138]

例如,第0存储器装置1220可以与第0数据缓冲器连接,第一存储器装置1221可以与第一数据缓冲器连接,第二存储器装置1222可以与第二数据缓冲器连接,第三存储器装置1223可以与第三数据缓冲器连接,第四存储器装置1224可以与第四数据缓冲器连接,第五存储器装置1225可以与第五数据缓冲器连接,第六存储器装置1226可以与第六数据缓冲器连接,并且第七存储器装置1227可以与第七数据缓冲器连接。

[0139]

图10是用于描述图9的存储器系统的部分写入操作的图。假设突发长度bl为8,多

个存储器装置1220至1227中的每一个通过4个数据线dq与主机1100连接。然而,本公开不限于此。例如,可以改变突发长度bl和与多个存储器装置中的每一个连接的数据线dq的数量。

[0140]

参照图9和图10,存储器模块1200中包括的存储器装置1220至1227的数量为8,突发长度bl为8,与多个存储器装置1220至1227中的每一个连接的数据线dq的数量为4,存储器模块1200可以通过一次写入操作储存与32字节(例如,32b)相对应的数据。因为存储器模块1200能够执行部分写入操作,所以存储器模块1200可以以半字节单位或字节单位储存数据。例如,如图2b所示,主机1100可以将第三数据dt3储存在存储器模块1200中。

[0141]

如图10所示,第0字节数据bd0可以包括第0半字节数据nd0和第一半字节数据nd1,第一字节数据bd1可以包括第二半字节数据nd2和第三半字节数据nd3,并且第二字节数据bd2可以包括第四半字节数据数据nd4和第五半字节数据nd5。第三字节数据bd3可以包括第六半字节数据nd6和第七半字节数据nd7。其余的字节数据bd4至bd31具有与上述类似的结构,因此将省略附加的描述以避免冗余。

[0142]

在一个实施例中,存储器模块1200可以以第0突发长度bl0接收第0输入数据din_0,可以以第一突发长度bl1接收第一输入数据din_1,可以以第二突发长度bl2接收第二输入数据din_2,可以以第三突发长度bl3接收第三输入数据din_3,可以以第四突发长度bl4接收第四输入数据din_4,可以以第五突发长度bl5接收第五输入数据din_5,可以以第六突发长度bl6接收第六输入数据din_6,并且可以以第七突发长度bl7接收第七输入数据din_7。

[0143]

如上所述,包括在存储器模块1200中的存储器装置1220至1227可以接收相同的命令/地址信号c/a和相同的时钟信号ck。相比之下,被包括在存储器模块1200中的存储器装置1220至1227中的每一个可以接收不同的数据选通信号dqs和不同的数据。

[0144]

第0输入数据din_0可包括第0字节数据bd0至第三字节数据bd3,第一输入数据din_1可包括第四字节数据bd4至第七字节数据bd7,第二输入数据din_2可包括第八字节数据bd8至第十一字节数据bd11,第三输入数据din_3可包括第十二字节数据bd12至第十五字节数据bd15,第四输入数据din_4可包括第十六字节数据bd16至第十九字节数据bd19,第五输入数据din_5可包括第二十字节数据bd20至第二十三字节数据bd23,第六输入数据din_6可包括第二十四字节数据bd24至第二十七字节数据bd27,第七输入数据din_7可包括第二十八字节数据bd28至第三十一字节数据bd31。

[0145]

换句话说,第0输入数据din_0可包括第0半字节数据nd0至第7半字节数据nd7,第一输入数据din_1可包括第8半字节数据nd8至第15半字节数据nd15,第二输入数据din_2可以包括第16半字节数据nd0至第23半字节数据nd23,第三输入数据din_3可以包括第24半字节数据nd24至第31半字节数据nd31,第四输入数据din_4可以包括第32半字节数据nd32至第39半字节数据nd39,第五输入数据din_5可包括第40半字节数据nd40至第47半字节数据nd47,第六输入数据din_6可包括第48半字节数据nd48至第55半字节数据nd55,第七输入数据din_7可包括第56半字节数据nd56至第63半字节数据nd63。

[0146]

包括在输入数据din中的每个半字节数据可以输入至存储器装置1220至1227中的对应存储器装置。在第0突发长度bl0,可以通过多个数据线dq0至dq3输入第0个半字节数据nd0至第0存储器装置1220,可以通过多个数据线dq4至dq7输入第一半字节数据nd1至第一存储器装置1221,可以通过多个数据线dq8至dq11输入第二半字节数据nd2至第二存储器装

置1222,可以通过多个数据线dq12至dq15输入第三半字节数据nd3至第三存储器装置1223,可以通过多个数据线dq16到dq19输入第四半字节数据nd4至第四存储器装置1224,可以通过多个数据线dq20到dq23输入第五半字节数据nd5至第五存储器装置1225,可以通过多个数据线dq24至dq28输入第六半字节数据nd6至第六存储器装置1226,以及通过多个数据线dq29到dq31输入第七半字节数据nd7至第七存储器装置1227。

[0147]

在第一突发长度bl1,可以通过多个数据线dq0至dq3输入第八半字节数据nd8至第0存储器装置1220,可以通过多个数据线dq4到dq7输入第九半字节数据nd9至第一存储器装置1221,可以通过多个数据线dq8至dq11输入第十半字节数据nd10至第二存储器装置1222,可以通过多个数据线dq12至dq15输入第十一半字节数据nd11至第三存储器装置1223,可以通过多个数据线dq16至dq19输入第十二半字节数据nd12至第四存储器装置1224,可以通过多个数据线dq20至dq23输入第十三半字节数据nd13至第五存储器装置1225,可以通过多个数据线dq24至dq28输入第十四半字节数据nd14至第六存储器装置1226,以及可以通过多个数据线dq29至dq31输入第十五半字节数据nd15至第七存储器装置1227。如在上文的描述中,其余的半字节数据nd16至nd63储存在存储器装置1220到1227中,因此,将省略附加的描述以避免冗余。

[0148]

即,第0存储器装置1220可以接收半字节数据nd0、nd8、nd16、nd24、nd32、nd40、nd48和nd56,第一存储器装置1221可以接收半字节数据nd1、nd9、nd17、nd25、nd33、nd41、nd49和nd57,第二存储器装置1222可以接收半字节数据nd2、nd10、nd18、nd26、nd34、nd42、nd50和nd58,第三存储器装置1223可以接收半字节数据nd3、nd11、nd19、nd27、nd35、nd43、nd51和nd59,第四存储器装置1224可以接收半字节数据nd4、nd12、nd20、nd28、nd36、nd44、nd52和nd60,第五存储器装置1225可以接收半字节数据nd5、nd13、nd21、nd29、nd37、nd45、nd53和nd61,第六存储器装置1226可以接收半字节数据nd6、nd14、nd22、nd30、nd38、nd46、nd54和nd62,以及第七存储器装置1227可以接收半字节数据nd7、nd15、nd23、nd31、nd39、nd47、nd55和nd63。

[0149]

因为第二半字节数据nd2和第三半字节数据nd3是有效的而其余的半字节数据nd0、nd1和nd4到nd63是伪数据,所以接收第二半字节数据nd2的第二存储器装置1222和接收第三半字节数据nd3的第三存储器装置1223可以是目标装置,以及其余存储器装置1220、1221、1224、1225、1226和1227可以是非目标存储器装置。

[0150]

例如,目标存储器装置可以指示接收全部或部分输入数据作为有效数据的存储器装置,并且非目标存储器装置可以是仅接收伪数据的存储器装置。可选地,目标存储器装置可以指示接收数据选通信号dqs切换的存储器装置,而非目标存储器装置可为接收保持逻辑高“h”的数据选通信号dqs的存储器装置。

[0151]

在一个实施例中,在主机1100的控制下,输出至目标存储器装置的数据选通信号dqs可以切换,并且输出至非目标存储器装置的数据选通信号dqs可以不切换。主机1100可以将输出至非目标存储器装置的数据选通信号dqs设置为逻辑高“h”。

[0152]

如上所述,根据本公开实施例的存储器系统1000可以执行部分写入操作。存储器装置100可通过多个掩码信号ms0至ms7和/或数据选通信号dqs确定输入数据是否有效。

[0153]

图11a是用于描述图9的每个存储器装置的部分写入操作的流程图。参照图9和图11a,在操作s210中,存储器装置1220至1227中的每一个可以接收包括部分写入使能信号

pwe和多个掩码信号ms的部分写入命令。操作s210类似于图5的操作s110,因此将省略附加的描述以避免冗余。

[0154]

在操作s220中,存储器装置1220至1227中的每一个可以确定是否接收到数据选通信号dqs切换。当确定存储器装置1220至1227中的每一个均接收到数据选通信号dqs切换时,可以执行操作s230;当确定存储器装置1220至1227中的每一个没有接收到数据选通信号dqs切换时,可以执行操作s260。即,接收数据选通信号dqs切换的目标存储器装置可执行操作s230,而未接收数据选通信号dqs切换的非目标存储器装置可执行操作s260。

[0155]

在操作s230中,每个目标存储器装置可以通过多个数据线dq接收输入数据din。在操作s240中,每个目标存储器装置可以基于多个掩码信号ms使能列选择线。操作s240类似于图5的操作s130,因此将省略附加的描述以避免冗余。

[0156]

在操作s250中,每个目标存储器装置可以基于列选择线csl将数据储存在多个存储器单元中。操作s250类似于图5的操作s140,因此将省略附加的描述以避免冗余。

[0157]

在操作s260中,每个非目标存储器装置可以通过多个数据线dq接收输入数据din。例如,每个非目标存储器装置可以通过多个数据线dq接收伪数据。每个非目标存储器装置可以不执行操作s250和操作s260。

[0158]

在一个实施例中,因为每个非目标存储器装置仅接收伪数据,所以每个非目标存储器装置可以禁用列选择线。可选地,每个非目标存储器装置可以保持列选择线的禁用状态。每个非目标存储器装置可以不将接收到的输入数据(即,伪数据)储存在多个存储器单元中。

[0159]

图11b是用于描述图9的存储器系统的部分写入操作的时序图。仅第一字节数据bd1可以具有有效数据值,并且其余字节数据bd0和bd2至bd31可以具有伪数据值。即,主机1100可以对第一字节数据bd1执行部分写入操作。为了描述方便,将省略与上述组件相关联的附加描述以避免冗余。

[0160]

存储器系统1000可以基于图11b所示的时序图来执行部分写入操作。在第一时间t1,主机1100可以向存储器模块1200发送命令和地址。主机1100可以通过命令线(例如,cmd)发送部分写入命令pwr。主机1100可以通过库组地址线(例如bg addr)发送库组地址bg。主机1100可以通过地址线(例如,addr)发送库地址ba、列地址ca、部分写入使能信号pwe和多个掩码信号ms。

[0161]

在一个实施例中,在从发送部分写入命令pwr和地址的时间tl起经过写入延迟wl之后,可以通过数据线dq0至dq31发送输入数据din。

[0162]

在一个实施例中,在命令/地址输入间隔tl期间,存储器模块1200可以从主机1100接收部分写入命令pwr和地址。在从发送部分写入命令pwr和地址的时间tl起经过写入延迟wl之后,存储器模块1200可以在数据输入间隔t2期间从主机1100接收输入数据。上文已描述了部分写入命令pwr的命令真值表,因此将省略附加描述以避免冗余。

[0163]

在一个实施例中,输入数据的第一字节数据bd1可以具有有效值,并且其余字节数据bd0和bd2至bd31可以具有伪值。第0输入数据din_0的一部分可以具有有效值。第一数据din_1至第七数据din_7的全部都可以具有伪值。第0输入数据din_0的第二半字节数据nd2和第三半字节数据nd3可以具有有效值。第0输入数据din_0的第0字节数据nd0、第一字节数据nd1、第四字节数据nd4、第五字节数据nd5、第六字节数据nd6和第七半字节数据nd7可以

具有伪值。

[0164]

因为第一字节数据bdl被包括在第0输入数据din_0中,所以在第一时间tl,主机1100可以设置部分写入使能信号pwe为逻辑高“h”,可以设置第0掩码信号ms0为逻辑低“l”,并且可以设置第一掩码信号ms1至第七掩码信号ms7为逻辑高“h”。

[0165]

在第0突发长度bl0处,存储器模块1200可以接收包括有效值的输入数据(例如,第0输入数据din_0)。在第一突发长度bl1至第七突发长度bl7,存储器模块1200可以接收包括伪值的输入数据(例如,第一输入数据din_1至第七输入数据din_7)。

[0166]

因为第0掩码信号ms0处于指示禁用状态的逻辑低“l”,所以存储器模块1200可以在存储器单元中储存与第0掩码信号相对应的输入数据的全部或部分(例如,第0输入数据din_0)。因为第一掩码信号ms1至第七掩码信号ms7处于指示使能状态的逻辑高“h”,所以存储器模块1200可以在存储器单元中不储存与第一掩码信号ms1至第七掩码信号ms7相对应的输入数据(例如,第一输入数据din_1至第七输入数据din_7)。

[0167]

即使第0掩码信号ms0处于逻辑低“l”,有效数据也可能不会输入至多个存储器装置1220至1227。即,即使掩码信号指示禁用状态,与掩码信号相对应的部分输入数据可以具有伪值。即,第0输入数据din_0可以包括伪数据。由此,可以通过数据选通信号dqs确定在一个突发长度期间输入至存储器模块1200的数据(即,突发数据)(例如,第0输入数据din_0)是否有效。

[0168]

因为第0输入数据din_0的第二半字节数据nd2和第三半字节数据nd3具有有效值,第0输入数据din_0的其余半字节数据nd0、nd1、nd4、nd5、nd6和nd7具有伪值,第二存储器装置1222和第三存储器装置1223可以接收有效数据,而其余存储器装置1220、1221、1224、1225、1226和1227可以接收伪数据。

[0169]

在一个实施例中,第二数据选通信号dqs2和第三数据选通信号dqs3可以在主机1100的控制下切换。在主机1100的控制下,第二数据选通信号dqs2和第三数据选通信号dqs3可以在从第二时间t2起的写入前导延迟twpre之前开始切换。在主机1100的控制下,第二数据选通信号dqs2和第三数据选通信号dqs3可以从发送最后输入数据(例如,第七输入数据din_7)的第三时间t3起切换至写入后导延迟twpst经过的时间。即,第二数据选通信号dqs2和第三数据选通信号dqs3可以在选通切换间隔t3期间切换。

[0170]

例如,可以通过设置模式寄存器设置写入前导延迟twpre。例如,可以通过模式寄存器的设置将写入前导延迟twpre设置为1tck或2tck。写入后导延迟twpst可以具有预先确定的值。例如,写入后导延迟twpst可以是0.5tck。

[0171]

在主机1100的控制下,第0数据选通信号dqs0、第一数据选通信号dqs1、第四数据选通信号dqs4、第五数据选通信号dqs5、第六数据选通信号dqs6和第七数据选通信号dqs7在选通切换间隔t3期间可以不切换。即,主机1100可以在选通切换间隔t3期间将第0数据选通信号dqs0、第一数据选通信号dqs1、第四数据选通信号dqs4、第五数据选通信号dqs5、第六数据选通信号dqs6和第七数据选通信号dqs7设置为逻辑高“h”。

[0172]

如上所述,主机1100可以允许输出至目标存储器装置(例如,1222和1223)的数据选通信号dqs切换并且可以通过多个数据线dq输出数据。主机1100可以在选通切换间隔t3期间将输出至非目标存储器装置(例如,1220、1221、1224、1225、1226和1227)的数据选通信号dqs设置为逻辑高“h”,并且可以通过多个数据线dq输出伪数据。

[0173]

多个存储器装置1220至1227中的每一个可以通过部分写入使能信号pwe、多个掩码信号ms和数据选通信号dqs执行部分写入操作。因为部分写入使能信号pwe处于逻辑高“h”,所以多个存储器装置1220至1227中的每一个均可以识别部分写入命令pwr。

[0174]

因为第一掩码信号ms1至第七掩码信号ms7处于逻辑高“h”,所以多个存储器装置1220至1227中的每一个可以识别第一输入数据din_1至第七输入数据din_7是伪数据。多个存储器装置1220至1227中的每一个可以禁用与第一输入数据din_1至第七输入数据din_7相对应的列选择线。多个存储器装置1220至1227中的每一个可以在存储器单元中不储存第一输入数据din_1至第七输入数据din_7。

[0175]

多个存储器装置1220至1227中的每一个可以确定是否接收到数据选通信号dqs切换。在选通切换间隔t3期间,多个存储器装置1220至1227中的每一个可以确定对应的数据选通信号dqs是否切换。当确定数据选通信号dqs在选通切换间隔t3期间切换时,多个存储器装置1220至1227中的每一个可以确定输入数据的全部或部分是有效数据。当数据选通信号dqs在选通切换间隔t3期间处于逻辑高“h”时,多个存储器装置1220至1227中的每一个可以确定全部输入数据是伪数据。

[0176]

例如,在选通切换间隔t3期间,目标存储器装置1222和1223可以确定数据选通信号dqs切换。因为第二数据选通信号dqs2在选通切换间隔t3期间切换并且第0掩码信号ms0处于禁用状态,所以第二存储器装置1222可以在存储器单元中储存第二半字节数据nd2。因为第三数据选通信号dqs3在选通切换间隔t3期间切换并且第0掩码信号ms0处于禁用状态,所以第三存储器装置1223可以在存储器单元中储存第三半字节数据nd3。

[0177]

在选通切换间隔t3期间,非目标存储器装置1220、1221和1224至1227可以确定数据选通信号dqs保持逻辑高“h”。因为在选通切换间隔t3期间对应的数据选通信号dqs0、dqs1和dqs4至dqs7处于逻辑高“h”,非目标存储器装置1220、1221和1224至1227可以确定全部输入数据是伪数据。非目标存储器装置1220、1221和1224至1227可以在存储器单元中不储存在第0突发长度bl0期间接收的输入数据。非目标存储器装置1220、1221和1224至1227可以不储存全部输入数据到存储器单元中。

[0178]

图12a是用于描述图9的每个存储器装置的部分写入操作的流程图。参照图9和图12a,在操作s310中,存储器装置1220至1227中的每一个可以接收包括部分写入使能信号pwe和多个掩码信号ms的部分写入命令pwr。操作s310类似于图11a的操作s210,因此将省略附加描述以避免冗余。

[0179]

在操作s320中,存储器装置1220至1227中的每一个可以确定是否接收到数据选通信号dqs切换。当确定存储器装置1220至1227中的每一个均接收到数据选通信号dqs切换时,可以执行操作s330;当确定存储器装置1220至1227中的每一个没有接收到数据选通信号dqs切换时,可以不执行操作s330至操作s350。即,接收数据选通信号dqs切换的目标存储器装置可以执行操作s330,而接收保持在逻辑高“h”的数据选通信号dqs的非目标存储器装置可以不执行操作s330至操作s350。

[0180]

操作s330至操作s350类似于图11a的操作s230至操作s250,因此将省略附加的描述以避免冗余。与图11a相比,每个非目标存储器装置可以通过多个数据线dq不接收输入数据din。

[0181]

图12b是用于描述图9的存储器系统的部分写入操作的时序图。主机1100可以在选

通切换间隔t3期间将输出至非目标存储器装置1220、1221、1224、1225、1226和1227的数据选通信号dqs设置为逻辑高“h”,可以甚至通过多个数据线dq不输出伪数据。非目标存储器装置1220、1221、1224、1225、1226和1227可以在命令/地址输入间隔t1期间接收部分写入命令pwr和地址,可以在数据输入间隔t2期间不接收输入数据,可以在选通切换间隔t3期间接收保持在逻辑高“h”的数据选通信号dqs。

[0182]

与图11b类似,主机1100可以在命令/地址输入间隔t1期间向目标存储器装置1222和1223提供部分写入命令pwr和地址,可以在数据输入间隔t2期间分别向目标存储器装置1222和1223提供半字节数据nd2和nd3,并且可以在选通切换间隔t3期间分别向目标存储器装置1222和1223提供数据选通信号dqs2和dqs3切换。

[0183]

图13a和图13b是用于描述根据本公开的存储器系统的部分写入操作的时序图。参照图9和图13a,主机1100可以通过写入命令wr和数据选通信号dqs执行部分写入操作。假设在第0至第七突发长度bl0到bl7期间,主机1100向第二存储器装置1222和第三存储器装置1223输出有效数据并且向其余的存储器装置1220、1221、1224、1225、1226和1227输出伪数据。

[0184]

如上表1和表2所示,在命令/地址输入间隔tl期间,主机1100可以控制命令/地址信号c/a向存储器模块1200输出写入命令wr。

[0185]

在选通切换间隔t3期间,主机1100可以输出数据选通信号dqs切换至目标存储器装置1222和1223。在选通切换间隔t3期间,主机1100可以输出保持在逻辑高“h”的数据选通信号dqs至非目标存储器装置1220、1221、1224、1225、1226和1227。

[0186]

在数据输入间隔t2期间,主机1100可以向目标存储器装置1222和1223输出有效数据。在数据输入间隔t2期间,主机1100可以向非目标存储器装置1220、1221、1224、1225、1226和1227输出伪数据。

[0187]

目标存储器装置1222和1223可以响应于写入命令wr将接收到的输入数据储存在存储器单元中。在选通切换间隔t3期间,由于接收到保持在逻辑高“h”的数据选通信号dqs,非目标存储器装置1220、1221、1224、1225、1226和1227可以确定全部输入数据是伪数据。因为确定全部输入数据是伪数据,非目标存储器装置1220、1221、1224、1225、1226和1227可以不将全部输入数据储存在存储器单元阵列120中。

[0188]

参照图9和图13b,存储器系统1000可以通过部分写入命令pwr、数据选通信号dqs和数据掩码信号dm_n执行部分写入操作。因为使用数据掩码信号dm_n,所以假设多个存储器装置1220至1227是x8存储器装置。存储器系统1000可以通过同时使用数据掩码信号dm_n和部分写入命令pwr以半字节为单位执行部分写入操作。

[0189]

在一个实施例中,第0存储器装置1220可以通过第0数据线dq0至第七数据线dq7与主机1100交换数据。第一存储器装置1221可以通过第八数据线dq8至第十五数据线dq15与主机1100交换数据。第二存储器装置1222可以通过第十六数据线dq16至第二十三数据线dq23与主机1100交换数据。第三存储器装置1223可以通过第二十四数据线dq24至第三十一数据线dq31与主机1100交换数据。第四存储器装置1224可以通过三十二数据线dq32至第三十九数据线dq39与主机1100交换数据。第五存储器装置1225可以通过第四十数据线dq40至第四十七条数据线dq47与主机1100交换数据。第六存储器装置1226可通过第四十八数据线dq48至第五十五数据线dq55与主机1100交换数据。第七存储器装置1227可以通过第五十六

数据线dq56至第六十三数据线dq63与主机1100交换数据。

[0190]

在一个实施例中,第0存储器装置1220可以通过第0数据掩码线从主机1100接收第0数据掩码信号dm_n0,第一存储器装置1221可以通过第一数据掩码线从主机1100接收第一数据掩码信号dm_n1,第二存储器装置1222可以通过第二数据掩码线从主机1100接收第二数据掩码信号dm_n2,第三存储器装置1223可以通过第三数据掩码线从主机1100接收第三数据掩码信号dm_n3,第四存储器装置1224可以通过第四数据掩码线从主机1100接收第四数据掩码信号dm_n4,第五存储器装置1225可以通过第五数据掩码线从主机1100接收第五数据掩码信号dm_n5,第六存储器装置1226可以通过第六数据掩码线从主机1100接收第六数据掩码信号dm_n6,第七存储器装置1227可以通过第七数据掩码线从主机1100接收第七数据掩码信号dm_n7。

[0191]

在一个实施例中,主机1100可以通过使用部分写入命令pwr和数据掩码信号dm_n以半字节为单位执行部分写入操作。例如,如上表3和表4所示,在命令/地址输入间隔t1期间,主机1100可以控制命令/地址信号c/a以将部分写入命令pwr输出至存储器模块1200。主机1100可以将部分写入使能信号pwe和多个掩码信号ms发送至存储器模块1200。

[0192]

在一个实施例中,多个掩码信号ms可以指示是否分别通过第0数据线dq0至第三数据线dq3、第八数据线dq8至第十一数据线dq11、第十六数据线dq16至第十九数据线dq19、第二十四数据线dq24至第二十七数据线dq27、第三十二数据线dq32至第三十五数据线dq35、第四十数据线dq40至第四十三数据线dq43、第四十八数据线dq48至第五十数据线dq51、以及第五十六数据线dq56至第五十九数据线dq59接收到掩码输入数据。

[0193]

每个数据掩码信号dm_n可以指示是否分别通过第四数据线dq4至第七数据线dq7、第十二数据线dq12至第十五数据线dq15、第二十数据线dq20至第二十三数据线dq23、第二十八数据线dq28至第三十一数据线dq31、第三十六数据线dq36至第三十九数据线dq39、第四十四数据线dq44至第四十七数据线dq47、第五十二数据线dq52至第五十五dq55、以及第六十数据线dq60至第六十三数据线dq63接收到掩码输入数据。

[0194]

图11b的多个掩码信号ms中的每一个均可以指示在一个突发长度中是否掩码输入至每个存储器装置的全部数据。例如,在第0存储器装置1220中,第0掩码信号ms0可以指示在第0突发长度bl0期间是否掩码通过第0数据线dq0至第三数据线dq3输入的第0半字节数据nd0。

[0195]

相比之下,图13b的多个掩码信号ms中的每一个可以指示在一个突发长度中是否掩码输入至每个存储器装置的数据的一部分。例如,在第0存储器装置1220中,第0掩码信号ms0可以指示在第0突发长度bl0期间是否掩码通过第0数据线dq0至第三数据线dq3输入的第0半字节数据nd0。在第0突发长度bl0期间输入的第0数据掩码信号dm_n0可以指示在第0突发长度bl0期间是否掩码通过第四数据线dq4至第七数据线dq7输入的第一半字节数据nd1。

[0196]

在存储器系统1000仅使用数据掩码信号dm_n的情况下,存储器系统1000可以以字节为单位执行部分写入操作。根据本公开实施例的存储器系统1000可以通过使用数据掩码信号dm_n和部分写入命令pwr以半字节为单位执行部分写入操作。

[0197]

与图11b类似,主机1100可以在选通切换间隔t3期间将与非目标存储器装置1220、1221、1224、1225、1226和1227相对应的数据选通信号设置为逻辑高“h”。

[0198]

图14是示出应用了根据本公开的存储器装置的计算系统2000的框图。参照图14,计算系统2000可以包括计算机、便携式计算机、超移动个人计算机(umpc)、工作站、服务器计算机、上网本、个人数字助理(pda)、便携式计算机、网络平板电脑、无线电话、移动电话、智能手机、数码相机、数码录音机、数码音频播放器、数码图片记录器、数码图片播放器、数码录像机、数码视频播放器、能够在无线环境中传输或接收信息的装置以及包括家庭网络在内的各种电子装置中的一种。

[0199]

计算系统2000可以包括处理器2100、存储器模块2200、芯片组2300、图形处理单元(gpu)(或图形模块)2400、输入/输出装置2500和储存装置2600。处理器2100可以执行计算系统2000的整体操作。处理器2100可以执行计算系统2000中的各种操作。

[0200]

存储器模块2200可以与处理器2100直接连接。例如,存储器模块2200可以是双列直插式存储器模块(dimm)的形式,并且存储器模块2200可以安装在直接与处理器2100连接的dimm插槽中并可与处理器2100进行通信。在一个实施例中,存储器模块2200可以包括参考图1至图8描述的存储器装置。参考图9至图13描述的存储器模块2200可以执行部分写入操作。

[0201]

芯片组2300可以与处理器2100电连接并且可以在处理器2100的控制下控制计算系统2000的硬件。例如,芯片组2300可以单独地通过主总线与gpu 2400、输入/输出装置2500和存储器装置2600连接,并可以执行主总线的桥接操作。

[0202]

gpu 2400可以执行用于输出计算系统2000的图像数据的一组计算操作。在一个实施例中,gpu 2400可以以片上系统的形式嵌入在处理器2100中。

[0203]

在一个实施例中,gpu 2400可以包括参照图1至图13描述的存储器装置或存储器模块。

[0204]

输入/输出装置2500包括将数据或指令输入至计算系统2000或将数据输出至外部装置的各种装置。储存装置2600可以用作计算系统2000的大容量储存介质。储存装置2600可以包括诸如硬盘驱动器(hdd)、固态驱动器(ssd)、存储器卡、存储器棒的大容量储存介质。

[0205]

图15是示出根据本公开实施例的储存系统的框图。参照图15,储存系统3000可以包括主机3100和储存装置3200。在一个实施例中,储存系统3000可以是信息处理装置(诸如个人计算机(pc)、笔记本电脑、服务器、工作站、智能手机、平板电脑、数码相机和黑匣子)之一,其被配置为处理各种信息并储存处理后的信息。

[0206]

主机3100可以控制储存系统3000的整体操作。例如,主机3100可以向储存装置3200发送用于在储存装置3200中储存数据“data”或读取储存在储存装置3200中的数据“data”的请求(rq)。在一个实施例中,主机3100可以是处理器核(诸如中央处理单元(cpu)或应用处理器,或者可以是通过网络连接的计算节点),其被配置为控制储存系统3000。

[0207]

在一个实施例中,主机3100可以包括主机控制器3110和主机存储器3120。主机控制器3110可以被配置为控制主机3100的整体操作或允许主机3100控制储存装置3200。主机存储器3120可以是用于主机3100的缓冲器存储器、缓存存储器或工作存储器。

[0208]

储存装置3200可以在主机3100的控制下操作。储存装置3200可以包括储存控制器3210、非易失性存储器装置3220和缓冲器存储器3230。在主机3100的控制下,储存控制器3210可以将数据储存在非易失性存储器装置3220中或者可以读取储存在非易失性存储器

装置3220中的数据。在一个实施例中,储存控制器3210可以执行各种管理操作以有效地使用非易失性存储器装置3220。

[0209]

储存控制器3210可以包括中央处理单元(cpu)3211、闪存转换层(flash translation layer,ftl)3212、纠错码(error correction code,ecc)引擎3213、高级加密标准(advanced encryption standard,aes)引擎3214、缓冲器接口电路3215、主机接口电路3216和存储器接口电路3217。

[0210]

cpu 3211可以执行储存控制器3210的整体操作。ftl 3212可以执行用于有效使用非易失性存储器装置3220的各种操作。例如,主机3100可以通过使用逻辑地址管理储存装置3200的储存空间。ftl 3212可以被配置为管理来自主机3100的逻辑地址与储存装置3200的物理地址之间的地址映射。ftl 3212可以执行磨损均衡操作以防止非易失性存储器装置3220的存储器块中的特定存储器块的过度退化。可以通过ftl 3212的磨损均衡操作提高非易失性存储器装置3220的寿命。ftl 3212可以对非易失性存储器装置3220执行垃圾收集操作以确保空闲存储器块。

[0211]

在一个实施例中,ftl 3212可以以硬件或软件的形式实现。在以软件形式实现ftl 3212的情况下,与ftl 3212相关联的程序代码或信息可以储存在缓冲器存储器3230或缓存存储器(例如,sram)(未示出)中并且可以由cpu 3211执行。在ftl 3212以硬件的形式实现的情况下,可以独立于cpu 3211提供被配置为执行ftl 3212的操作的硬件加速器。

[0212]

ecc引擎3213可以对从非易失性存储器装置3220读取的数据执行错误检测和纠正。例如,ecc引擎3213可以为待写入非易失性存储器装置3220中的数据生成纠错码(或(多个)奇偶校验位(parity bit))。由此生成的纠错码(或奇偶校验位)可以与待写入的数据一起储存在非易失性存储器装置3220中。之后,当从非易失性存储器装置3220读取写入的数据时,ecc引擎3213可以基于读取数据和对应的纠错码(或相应的奇偶校验位)检测并纠正读取数据的错误.

[0213]

aes引擎3214可以对从主机3100接收的数据执行加密操作或者可以对从非易失性存储器装置3220接收的数据执行解密操作。在一个实施例中,加密操作和解密操作可以基于对称密钥算法执行。

[0214]

缓冲器接口电路3215可以被配置为按照预限定的通信协议与缓冲器存储器3230通信。在一个实施例中,预限定的接口协议可以包括各种接口协议中的至少一种,诸如双数据速率(ddr)、低功耗ddr(lpddr)和通用串行总线(usb)。缓冲器接口电路3215可以向缓冲器存储器3230发送基于预限定的接口协议的信号。缓冲器接口电路3215可以从缓冲器存储器3230接收基于预限定的接口协议的信号。

[0215]

响应于来自cpu 3211或直接存储器存取(dma)引擎的请求,缓冲器接口电路3215可以将数据储存在缓冲器存储器3230中或者可以读取储存的数据。缓冲器接口电路3215可以向缓冲器存储器3230发送命令/地址信号c/a。缓冲器接口电路3215可以通过多个数据线dq与缓冲器存储器3230交换数据。缓冲器接口电路3215可以与缓冲器存储器3230交换数据选通信号dqs。

[0216]

缓冲器接口电路3215可以以字节或半字节为单位以及以缓存线为单位从cpu 3211接收读取或写入请求。缓冲器接口电路3215可以用缓冲器存储器3230执行部分写入操作。

[0217]

在一个实施例中,缓冲器接口电路3215可以包括掩码控制电路3218。掩码控制电路3218可以响应于从cpu 3211接收的部分写入请求控制多个掩码信号ms、部分写入使能信号pwe和数据选通信号dqs。

[0218]

掩码控制电路3218可以将部分写入命令pwr发送至缓冲器存储器3230。掩码控制电路3218可以在命令/地址输入间隔中通过第十二地址线a12输出部分写入使能信号pwe。在命令/地址输入间隔中,掩码控制电路3218可以通过第0地址线a0输出第0掩码信号ms0,可以通过第一地址线a1输出第一掩码信号ms1,可以通过第二地址线a2输出第二掩码信号ms2,可以通过第十一条地址线a11输出第三掩码信号ms3,可以通过第十三地址线a13输出第四掩码信号ms4,可以通过第0芯片标识符线c0输出第五掩码信号ms5,可以通过第一芯片标识符线c1输出第六掩码信号ms6,并且可以通过第二芯片标识符线c2输出第七掩码信号ms7。

[0219]

掩码控制电路3218可以生成多个掩码信号。掩码控制电路3218可以设置与包括有效数据的输入数据的突发长度相对应的掩码信号以指示禁用状态,并且可以设置与仅包括伪数据(即,不包括有效数据的输入数据)的输入数据的突发长度相对应的掩码信号以指示使能状态。多个掩码信号可以指示在整个突发长度期间输入至缓冲器存储器3230的数据中的有效数据的位置。

[0220]

例如,在掩码控制电路3218在第0突发长度bl0期间将第一字节数据bd1输出至缓冲器存储器3230的情况下,在命令/地址输入间隔期间,掩码控制电路3218可以设置第0掩码信号ms0为逻辑低“l”,可以设置其余的掩码信号ms1至ms7为逻辑高“h”。

[0221]

掩码控制电路3218可以向缓冲器存储器3230发送指示数据是否有效的数据选通信号dqs。在选通切换间隔t3期间,与目标存储器装置连接的数据选通信号dqs可以在掩码控制电路3218的控制下切换。掩码控制电路3218可以在选通切换间隔t3期间将与非目标存储器装置连接的数据选通信号dqs设置为逻辑高“h”。

[0222]

为了以半字节或字节为单位更新数据,掩码控制电路3218可以从cpu 3211接收地址和数据。掩码控制电路3218可以从cpu 3211接收与字节单位相对应的地址和数据。在下文中,如图2b所示,假设掩码控制电路3218更新储存在第一存储器单元组mcg1中的数据。

[0223]

掩码控制电路3218可基于从cpu 3211接收的数据生成第三数据dt3。掩码控制电路3218可通过使用从cpu 3211接收的数据作为第一字节数据bd1以及添加伪数据生成第三数据dt3。掩码控制电路3218可以生成第三数据dt3,其包括具有有效值的第一字节数据bd1和均具有伪值的第0字节数据bd0和第二字节数据bd2至第三十一字节数据bd31。例如,伪值可以指给定值或随机值。掩码控制电路3218可通过多个数据线dq将第三数据dt3发送至缓冲器存储器3230。

[0224]

缓冲器存储器3230可以是被配置为暂时储存输入至储存控制器3210的数据的写入缓冲器或读取缓冲器。可选地,缓冲器存储器3230可以被配置为储存储器存控制器3210操作所需的各种信息。例如,缓冲器存储器3230可以储存由ftl 3212管理的映射表。可选地,缓冲器存储器3230可以储存与ftl 3212相关联的软件、固件或信息。

[0225]

缓冲器存储器3230可以在缓冲器接口电路3215的控制下操作。例如,响应于从缓冲器接口电路3215接收的信号,缓冲器存储器3230可以储存数据或者可以将储存的数据提供至缓冲器接口电路3215。在一个实施例中,缓冲器存储器3230可以是动态随机存取存储

器(dram)装置,但本公开不限于此。缓冲器存储器3230可以执行参考图1至图14描述的部分写入操作。

[0226]

主机接口电路3216可以按照预限定的接口协议与主机3100通信。在一个实施例中,预限定的接口协议可以包括用于各种接口的协议中的至少一种,诸如ata(高级技术附件)接口、sata(串行ata)接口、e-sata(外部sata)接口、scsi(小型计算机小型接口)接口、sas(串行附接scsi)接口、pci(外围组件互连)接口、pcie(快速pci)接口、nvme(快速nvm)接口、ieee 1394接口、usb(通用串行总线)接口、sd(安全数字)卡接口、mmc(多媒体卡)接口、emmc(嵌入式多媒体卡)接口、ufs(通用闪存)接口、eufs(嵌入式通用闪存)接口、cf(紧凑式闪存)卡接口或网络接口。主机接口电路3216可以从主机3100接收基于预限定的接口协议的信号并且可以基于接收到的信号进行操作。可选地,主机接口电路3216可以向主机3100发送基于预限定的接口协议的信号。

[0227]

存储器接口电路3217可以按照预限定的通信协议与非易失性存储器装置3220通信。在一个实施例中,预限定的接口协议可以包括用于各种接口的协议中的至少一个,诸如切换接口和开放nand闪存接口(open nand flash interface,onfi)。在一个实施例中,存储器接口电路3217可以基于切换接口与非易失性存储器装置3220通信。在这种情况下,存储器接口电路3217可以通过多个信道ch与非易失性存储器装置3220通信。在一个实施例中,多个信道ch中的每一个可以包括被配置为传输各种控制信号(例如,/ce、cle、ale、/we、/re和r/b)、数据信号和数据选通信号的多个信号线。

[0228]

图16是示出图15的掩码控制电路的操作的流程图。参照图15和图16,在操作s410中,掩码控制电路3218可以从cpu 3211或dma引擎(未示出)接收写入请求和第四数据dt4。第四数据dt4可以是小于缓存线单位的半字节单位或字节单位的数据。在下文中,假设第四数据dt4为字节单位的数据。例如,假设写入请求包括写入命令和地址,该地址指示图2b的第一存储器单元组mcg1。

[0229]

在操作s420中,掩码控制电路3218可以基于第四数据dt4生成第三数据dt3。掩码控制电路3218可以通过使用字节单位的第四数据dt4作为第一字节数据bd1并添加伪数据生成第三数据dt3。

[0230]

在操作s430中,掩码控制电路3218可基于第三数据dt3生成多个掩码信号ms。因为有效的第一字节数据bd1被包括在第0输入数据din_0中,所以掩码控制电路3218可以将第0掩码信号ms0设置为逻辑低“l”,并且可以将其余的掩码信号ms1至ms7设置为逻辑高“h”。

[0231]

在操作s440中,掩码控制电路3218可以在命令/地址输入间隔期间向缓冲器存储器3230输出包括部分写入使能信号pwe和多个掩码信号ms的部分写入命令pwr。例如,掩码控制电路3218可以在命令/地址输入间隔期间通过第十二地址线a12输出指示使能状态的部分写入使能信号pwe。

[0232]

在命令/地址输入间隔中,掩码控制电路3218可以通过第0地址线a0输出指示禁用状态的第0掩码信号ms0,可以通过第一地址线a1输出指示使能状态的第一掩码信号ms1,可以通过第二地址线a2输出指示使能状态的第二掩码信号ms2,可以通过第十一地址线a11输出指示使能状态的第三掩码信号ms3,可以通过第十三地址线a13输出指示使能状态的第四掩码信号ms4,可以通过第0芯片标识符线c0输出指示使能状态的第五掩码信号ms5,可以通过第一芯片标识符线c1输出指示使能状态的第六掩码信号ms6,并且可以通过第二芯片标

识符线c2输出指示使能状态的第七掩码信号ms7。

[0233]

在操作s450中,掩码控制电路3218可以在选通切换间隔期间输出数据选通信号dqs至缓冲器存储器3230。如图9所示,在缓冲器存储器3230包括多个存储器装置的情况下,在选通切换间隔期间,掩码控制电路3218可以输出切换的数据选通信号dqs至目标存储器装置,可以输出保持在逻辑高“h”的数据选通信号dqs至非目标存储器装置。

[0234]

在操作s460中,掩码控制电路3218可以通过多个数据线dq输出第三数据dt3至缓冲器存储器3230。如图9所示,在缓冲器存储器3230包括多个存储器装置的情况下,掩码控制电路3218可以将数据输出至目标存储器装置和非目标存储器装置。此外,掩码控制电路3218可以向目标存储器装置输出数据而可以向非目标存储器装置不输出数据。

[0235]

如上所述,存储器系统可以执行部分写入操作。主机可以在命令/地址输入间隔期间通过使用命令/地址信号而不使用单独的数据掩码信号向存储器装置发送多个掩码信号和部分写入使能信号。响应于部分写入命令,存储器装置可以基于多个掩码信号和数据选通信号将输入数据的全部或部分储存在存储器单元中。

[0236]

根据本公开,可以通过通过命令/地址线向存储器装置发送多个掩码信号执行部分写入操作。因此,提供了能够最小化功耗的电子装置、主机的操作方法、存储器模块的操作方法和存储器装置的操作方法。

[0237]

如本领域中的传统,可以根据执行所描述的一个或多个功能的块来描述和图示实施例。这些在本文中可被称为单元或模块等的块由模拟和/或数字电路(诸如逻辑门、集成电路、微处理器、微控制器、存储器电路、无源电子组件、有源电子组件、光学组件、硬连线电路等)物理实现,并且可以可选地由固件和/或软件驱动。例如,电路可以体现在一个或多个半导体芯片中,或者在诸如印刷电路板等的基板支撑件上。构成块的电路可以由专用硬件或由处理器(例如,一个或多个可编程的微处理器和相关电路)或由执行块的一些功能的专用硬件和执行块的其他功能的处理器的组合来实现。在不背离本公开的范围的情况下,实施例的每个块可以物理地分离为两个或更多个交互和离散的块。同样地,在不背离本公开的范围的情况下,实施例的块可以物理地组合成更复杂的块。实施例的一方面可以通过储存在非暂时性储存介质内并且由处理器执行的指令来实现。

[0238]

虽然已经参考本公开的实施例描述了本公开,但是对于本领域普通技术人员显而易见的是,在不背离以下的权利要求中提出的本公开设定的精神和范围的情况下,可以对其进行各种改变和修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。