1.本实用新型属于时钟拓扑结构的技术领域,具体涉及一种数字板卡时钟拓扑结构。

背景技术:

2.随着移动通信技术和数字技术的不断发展,尤其是5g移动通信技术的发展,对数字板卡的质量要求也越来越高,即现有的数字板卡包含有更多的功能,集成有更多的电路结构。

3.现有的数字板卡的主要技术指标是要实现高速实时数据采集和通信,高速接口丰富,速率高等特点,难度相对比较高。

4.现有的数字板卡中的许多集成的电路都需要时钟信号,在现有的设计中,需要采用多个晶体以作为时钟源,但多个独立的时钟源会带来这些时钟与靶标同步的问题,提高了系统成本,同时增大了对于电路板面积的要求;除此,多个时钟源将会带来抖动和高功耗的问题。

技术实现要素:

5.本实用新型的目的在于针对现有技术中的上述不足,提供一种数字板卡时钟拓扑结构,以解决现有数字板卡的多个时钟源带来的抖动和高功耗的问题。

6.为达到上述目的,本实用新型采取的技术方案是:

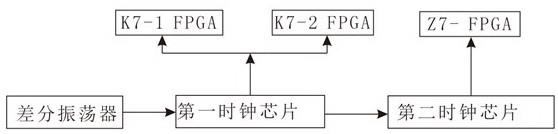

7.一种数字板卡时钟拓扑结构,其包括差分振荡器;差分振荡器与第一时钟芯片输入端电性连接;第一时钟芯片输出端分别与k7-1 fpga芯片、k7-2 fpga芯片和第二时钟芯片的输入端电性连接;第二时钟芯片的输出端与z7 fpga芯片电性连接。

8.进一步地,差分振荡器为sit9121差分振荡器;

9.第一时钟芯片和第二时钟芯片均为adi adclk854bcpz时钟芯片;

10.k7-1 fpga芯片和k7-2 fpga芯片均为xc7k325t-2ffg900i pl芯片;

11.z7 fpga芯片为xc7z100-2ffg900i pl芯片。

12.进一步地,sit9121差分振荡器与第一时钟芯片的clk0端口信号相连;第一时钟芯片的out1端口与第二时钟芯片的clk0端口信号连接。

13.进一步地,第一时钟芯片的out0端口、out2端口、out3端口、out4端口、out5端口、out6端口、out8端口、out9端口、out10端口、out11端口分别与k7-2 fpga芯片的bank116端口、k7-1 fpga芯片的bank34端口、k7-1 fpga芯片的bank117端口、k7-1 fpga芯片的bank115端口、k7-1 fpga芯片的bank116端口、k7-1 fpga芯片的bank118端口、k7-2 fpga芯片的bank118端口、k7-2 fpga芯片的bank115端口、k7-2 fpga芯片的bank117端口、k7-2 fpga芯片的bank34端口电性相连。

14.进一步地,第二时钟芯片的out0端口、out1端口、out2端口、out3端口、out4端口、out5端口、out6端口、out7端口、out8端口分别与z7 fpga芯片的bank111端口、z7 fpga芯片

的bank112端口、z7 fpga芯片的bank110端口、z7 fpga芯片的bank35端口、fmc1芯片的m2c-clk1端口、z7 fpga芯片的bank109端口、fmc1芯片的m2c-clk0端口、fmc0芯片的m2c-clk1端口、fmc0芯片的m2c—clk0端口电性连接。

15.本实用新型提供的数字板卡时钟拓扑结构,具有以下有益效果:

16.本实用新型将sit9121差分振荡器作为主要的时钟源,并只需采用一个时钟源,配合两个adi adclk854bcpz时钟芯片即可实现对多个处理器,如k7-1 fpga芯片、k7-2 fpga芯片和z7 fpga芯片,提供不同的时钟源,以将时钟信号分配至数字板卡中的不同处理器以及不同的功能模块中;本实用新型有效的解决了使用多个独立的时钟源带来的时钟与靶标同步的问题,同时,降低了板卡成本,降低了数字板卡面积,且实现了数字板卡的低抖动和低功耗。

附图说明

17.图1为数字板卡时钟拓扑结构的原理框图。

18.图2为数字板卡时钟拓扑结构电路图。

19.图3为数字板卡外围电路图。

具体实施方式

20.下面对本实用新型的具体实施方式进行描述,以便于本技术领域的技术人员理解本实用新型,但应该清楚,本实用新型不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本实用新型的精神和范围内,这些变化是显而易见的,一切利用本实用新型构思的实用新型创造均在保护之列。

21.根据本技术的一个实施例,参考图1,本方案的数字板卡时钟拓扑结构,包括差分振荡器;差分振荡器与第一时钟芯片输入端电性连接;第一时钟芯片输出端分别与k7-1 fpga芯片、k7-2 fpga芯片和第二时钟芯片的输入端电性连接;第二时钟芯片的输出端与z7 fpga芯片电性连接。

22.本实施例采用差分振荡器作为独立的时钟源,并通过第一时钟芯片和第二时钟芯片将该独立的信号分配至k7-1 fpga芯片、k7-2 fpga芯片和z7 fpga芯片。

23.为进一步清楚描述本实施例,本实施例选用如下型号进行说明:

24.差分振荡器为sit9121差分振荡器;

25.第一时钟芯片和第二时钟芯片均为adi adclk854bcpz时钟芯片,lvds最高输出1.2 ghz,coms输出最高250mhz,可对低抖动、低功耗应用进行优化。

26.k7-1 fpga芯片和k7-2 fpga芯片均为xc7k325t-2ffg900i pl芯片,其逻辑资源丰富,数据处理运算能力极强,外挂高速fmc高速扩张接口,可以灵活的是实现各种数字采集板卡子卡无缝对接。

27.z7 fpga芯片为xc7z100-2ffg900i pl芯片,其逻辑资源丰富,数据处理运算能力极强,5个hr bank,3个hp bank,4个gtx bank。芯片集成dual-core arm cortex-a9 mpcore,ps支持丰富的外设接口,ddr3、quad-spi、nand、emmc、 uart、can、usb 2.0、i2c、spi等外设接口。

28.参考图2,sit9121差分振荡器与第一时钟芯片的clk0端口信号相连;第一时钟芯

片的out1端口与第二时钟芯片的clk0端口信号连接。

29.具体的,sit9121差分振荡器将156.25mhz的lvds信号传输至第一块adi adclk854bcpz时钟芯片的clk0端口。

30.第一块adi adclk854bcpz时钟芯片将156.25mhz的lvds信号从out1端口传输至第二块adi adclk854bcpz时钟芯片的clk0端口。

31.参考图2和图3,第一块adi adclk854bcpz时钟芯片将时钟信号通过输出端口进一步传输至k7-1 fpga芯片和k7-2 fpga芯片中,其具体端口对应关系如下:

32.第一时钟芯片的out0端口、out2端口、out3端口、out4端口、out5端口、out6端口、out8端口、out9端口、out10端口、out11端口分别与k7-2 fpga芯片的bank116端口、k7-1 fpga芯片的bank34端口、k7-1 fpga芯片的bank117端口、k7-1 fpga芯片的bank115端口、k7-1 fpga芯片的bank116端口、k7-1 fpga芯片的bank118端口、k7-2 fpga芯片的bank118端口、k7-2 fpga芯片的bank115端口、k7-2 fpga芯片的bank117端口、k7-2 fpga芯片的bank34端口电性相连。

33.参考图2和图3,第二块adi adclk854bcpz时钟芯片将时钟信号通过输出端口进一步传输至z7fpga芯片、fmc1芯片和fmc0芯片中,其具体端口对应关系如下:

34.第二时钟芯片的out0端口、out1端口、out2端口、out3端口、out4端口、out5端口、out6端口、out7端口、out8端口分别与z7 fpga芯片的bank111端口、z7 fpga芯片的bank112端口、z7 fpga芯片的bank110端口、z7 fpga芯片的bank35端口、fmc1芯片的m2c-clk1端口、z7 fpga芯片的bank109端口、fmc1芯片的m2c-clk0端口、fmc0芯片的m2c-clk1端口、fmc0芯片的m2c—clk0端口电性连接。

35.本实用新型将sit9121差分振荡器作为主要的时钟源,并只需采用一个时钟源,配合两个adi adclk854bcpz时钟芯片即可实现对多个处理器,如k7-1 fpga芯片、k7-2 fpga芯片和z7 fpga芯片,提供不同的时钟源,以将时钟信号分配至数字板卡中的不同处理器以及不同的功能模块中;本实用新型有效的解决了使用多个独立的时钟源带来的时钟与靶标同步的问题,同时,降低了板卡成本,降低了数字板卡面积,且实现了数字板卡的低抖动和低功耗。

36.虽然结合附图对实用新型的具体实施方式进行了详细地描述,但不应理解为对本专利的保护范围的限定。在权利要求书所描述的范围内,本领域技术人员不经创造性劳动即可做出的各种修改和变形仍属本专利的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。