1.本发明涉及一种防止晶体管的错误导通的镜像钳位电路。

背景技术:

2.被称为镜像钳位(mirror clamping)的方法作为用于防止诸如mosfet(金属氧化物半导体场效应晶体管)、igbt(绝缘栅双极晶体管)等晶体管的错误导通的方法而被人们所熟知。在镜像钳位中,如果目标晶体管是mosfet,则用于镜像钳位的开关被插入在晶体管的栅极与基准电位之间,该晶体管的源极被供给有基准电位。该开关配置有例如mosfet。通过在晶体管关断时保持开关的导通,晶体管的vgs(晶体管栅极与源极之间的电压)被强制保持在大约0v,以防止晶体管的栅极电压上升。如果目标晶体管是igbt,则开关被插入在晶体管的栅极与基准电位之间,晶体管的发射极被供给有基准电位。

3.此外,在镜像钳位中,利用将晶体管的栅极电压与预定基准电压进行比较的比较器来接通开关。这种镜像钳位在例如专利文献1中被公开。

4.引用列表

5.专利文献

6.专利文献1:日本特开2016-171720号公报(图9)

技术实现要素:

7.技术问题

8.已知的镜像钳位配置的不便之处在于为了实现高操作速度,需保持向上述比较器供给相对大的电流,因此苦于功耗增加。

9.针对上述背景,本发明的目的是提供一种允许功耗降低的镜像钳位电路。

10.问题的解决方案

11.根据本发明的一个方面,一种镜像钳位电路包括:

12.比较器,其具有:

13.第一输入端子,其可连接到晶体管的第一控制端子,该晶体管具有

14.第一控制端子,其连接到一个端子被供给有输出电压的电阻器的另一端子,以及

15.第一端子,其被供给有基准电位;以及

16.第二输入端子,其被供给有基准电压;

17.晶体管开关,其具有基于从所述比较器输出的比较信号被供给有控制端子电压的第二控制端子,该晶体管开关被插入在第一控制端子和基准电位之间;

18.or电路,其被供给有基于所述控制端子电压和所述输出电压的信号;以及

19.电流供给器,其被配置为基于所述or电路的输出来改变供给到所述比较器的电流量(第一配置)。

20.在上述第一配置中,还可以提供锁存电路,所述锁存电路被配置为当输出电压处于高电平时将控制端子电压锁存为低电平(第二配置)。

21.在上述第一或第二配置中,还可以提供延迟电路,所述延迟电路被配置为延迟控制端子电压并且输出延迟信号作为延迟的结果,并且基于控制端子电压的信号可以是延迟信号(第三配置)。

22.在上述第一至第三配置中的任一配置中,电流供给器可以包括:

23.第一恒流源;

24.第一电流镜,其被配置为基于由第一恒流源生成的第一输入电流来生成第一输出电流;

25.第二电流镜,其被配置为基于第一输入电流生成第二输出电流;

26.开关,其设置在第二输出电流流过的路径中,该开关被配置为基于or电路的输出而导通和关断。

27.这里,当开关导通时,可以基于通过将第一输出电流和第二输出电流结合在一起而生成的电流来向比较器供应电流(第四配置)。

28.在上述第四配置中,第一电流镜、第二电流镜和所述开关可以配置有pmos晶体管(第五配置)。

29.在上述第一至第五配置中的任一配置中,晶体管开关可以是nmos晶体管(第六配置)。

30.根据本发明的另一方面,一种ic封装包括:根据上述任一配置的镜像钳位电路;输出端子,其被配置为向外部输出输出电压;镜像钳位端子,其被配置为允许第一控制端子连接到外部;以及基准电位端子,其被配置为允许向其施加基准电位(第七配置)。

31.在上述第七配置中,还可以提供:脉冲生成器,其被配置为基于输入信号生成脉冲;逻辑电路;隔离变压器,其被配置为将脉冲传输到逻辑电路;以及开关臂,其被配置有串联连接在电源电压和基准电位之间的开关元件,该开关臂被配置为通过由所述逻辑电路驱动来生成输出电压(第八配置)。

32.本发明的有益效果

33.利用根据本发明的镜像钳位电路,可以降低功耗。

附图说明

34.图1是示出根据本发明示例性实施例的栅极驱动器的配置的图。

35.图2是示出比较器和电流供给器的具体电路配置的示例的图。

36.图3是示出根据本发明示例性实施例的镜像钳位电路的操作示例的时序图。

37.图4是示出根据变型例的栅极驱动器的配置的图。

38.图5是示出根据变型例的镜像钳位电路的操作示例的时序图。

具体实施方式

39.在下文中,将参考附图描述本发明的示例性实施例。

40.《栅极驱动器的配置》

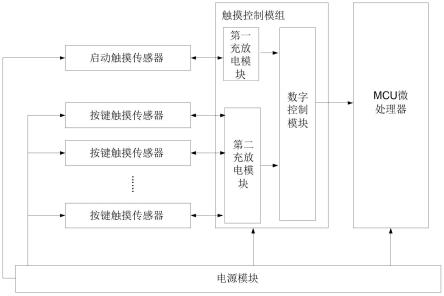

41.图1是示出根据本发明示例性实施例的栅极驱动器10的配置的图。如图1所示,栅极驱动器10是驱动nmos晶体管m1的栅极的装置。

42.栅极驱动器10包括初级电路1、次级电路2和隔离变压器3。栅极驱动器10是ic封

装,其包括gnd1端子、vcc1端子、ina端子、inb端子、gnd2端子(基准电位端子)、vcc2端子、out端子(输出端子)和mc端子(镜像钳位端子),上述这些端子是用于与外部建立电连接的外部端子(引线端子)。

43.初级电路1包括第一施密特触发器(schmitt trigger)11、第二施密特触发器12、and电路13、脉冲生成器14和第一uvlo(欠电压锁定(undervoltage lock-out))电路15。

44.次级电路2包含逻辑电路21、pmos晶体管22、nmos晶体管23、镜像钳位电路24、第二uvlo电路25以及ovp(过电压保护(overvoltage protection))电路26。

45.设置隔离变压器3以将初级电路1和次级电路2连接在一起。隔离变压器3将初级电路1和次级电路2彼此隔离,同时将来自初级电路1的信号传输到次级电路2。

46.第一uvlo电路15监测施加到vcc1端子的电源电压vcc1,并且当电源电压vcc1下降到指定电压以下时,第一uvlo电路15关闭初级电路1。

47.第一施密特触发器11将从外部输入到ina端子的第一输入信号in1传输到and电路13的第一输入端子。第二施密特触发器12将从外部输入到inb端子的第二信号in2传输到and电路13的第二输入端子。

48.and电路13输出被输入到其第一输入端子的信号电平和将输入到其第二输入端子的信号电平反转而得到的电平的逻辑积。因此,当第一输入信号in1和第二输入信号in2都处于低电平,或者第一输入信号in1处于低电平且第二输入信号in2处于高电平,或者第一输入信号in1和第二输入信号in2都处于高电平时,and电路13的输出处于低电平;并且当第一输入信号in1处于高电平且第二输入信号in2处于低电平时,and电路13的输出处于高电平。

49.当由and电路13的输出从高电平下降到低电平触发时,脉冲生成器14生成具有比and电路13的输出更小宽度的脉冲,并且将该脉冲输出到隔离变压器3的初级侧。由供给到隔离变压器3的初级侧的脉冲引起的电流变化在隔离变压器3的次级侧中产生电流,并且该电流被供给到逻辑电路21。在这种状态下,逻辑电路21输出高电平信号,该高电平信号被输入到pmos晶体管22的栅极和nmos晶体管23的栅极。

50.这里,pmos晶体管22(开关元件)和nmos晶体管23(开关元件)通过串联连接在施加到vcc2端子的电源电压vcc2和施加到gnd2端子的第二接地gnd2之间而构成开关臂。具体地,pmos晶体管22的源极连接到电源电压vcc2的施加端子。pmos晶体管22的漏极在节点n2处连接到nmos晶体管23的漏极。nmos晶体管23的源极连接到第二接地gnd2的施加端子。

51.节点n1连接到逻辑电路21的输出端子,在节点n1处pmos晶体管22的栅极和nmos晶体管23的栅极连接在一起。

52.节点n2连接到out端子。电阻器r1的一个端子外部连接到out端子。电阻器r1的另一端子连接到nmos晶体管m1的栅极(第一控制端子)。nmos晶体管m1的源极(第一端子)外部连接到gnd2端子。用作次级电路2的基准电位的第二接地gnd2不同于施加到gnd1端子且用作初级电路1的基准电位的第一接地gnd1。

53.这里,在来自逻辑电路21的高电平信号被施加到节点n1的情况下,pmos晶体管22关断,nmos晶体管23导通,并且作为out端子处的电压的输出电压out等于第二接地gnd2(低电平)。因此,nmos晶体管m1关断。

54.相比之下,接着由and电路13的输出从低电平上升至高电平而被触发,脉冲生成器

14生成具有比and电路13的输出更小宽度的脉冲,并且将该脉冲输出到隔离变压器3的初级侧。由供给到隔离变压器3的初级侧的脉冲引起的电流变化在隔离变压器3的次级侧中产生电流,并且该电流被供给到逻辑电路21。在这种状态下,逻辑电路21输出施加到节点n1的低电平信号。

55.在这种状态下,pmos晶体管22导通,nmos晶体管23关断,并且输出电压out等于电源电压vcc2(高电平)。因此,nmos晶体管m1导通。

56.由栅极驱动器10驱动的晶体管可以配置有igbt而不是nmos晶体管m1。在这种情况下,电阻器r1的另一端子连接到igbt的栅极,gnd2端子连接到igbt的发射极。

57.第二uvlo电路25监测施加到vcc2端子的电源电压vcc2。当电源电压vcc2下降到指定电压以下时,第二uvlo电路25关闭次级电路2。ovp电路26是检测电源电压vcc2中的过电压的电路。

58.《镜像钳位的配置》

59.接下来,将描述次级电路2中的镜像钳位电路24的配置。镜像钳位电路24是防止nmos晶体管m1在关断状态下错误导通的电路。

60.如图1所示,镜像钳位电路24包括比较器241、锁存电路242、nmos开关243、or电路244和电流供给器245。

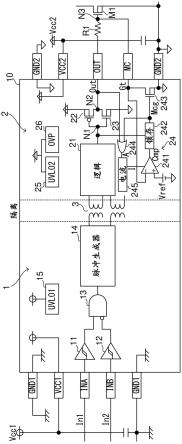

61.mc端子外部连接到节点n3,电阻器r1的另一端子和nmos晶体管m1的栅极连接到节点n3。比较器241的反相输入端子(-)连接到mc端子。因此,比较器241的反相输入端子(-)被供给有mc端子处的电压,即,nmos晶体管m1的第一栅极电压gt。将预定基准电压vref施加到比较器241的非反相输入端子( )。

62.比较器241向锁存电路242输出作为第一栅极电压gt与基准电压vref的比较结果的比较信号cmp。根据节点n1处的电压电平(即,输出电压out的电平),锁存电路242在输出具有相同于第二栅极电压mcg的电平的比较信号cmp本身与输出不论比较信号cmp如何而被锁存为低电平的第二栅极电压mcg之间切换。

63.作为nmos晶体管的nmos开关243被插入在mc端子和gnd2端子之间。具体地,nmos开关243的漏极连接到mc端子。nmos开关243的源极连接到gnd2端子。即,nmos开关243被插入在nmos晶体管m1的栅极和第二接地gnd2(基准电位)之间。

64.第二栅极电压(控制端子电压)mcg被施加到nmos开关243的栅极(第二控制端子)。第二栅极电压mcg被输入到or电路244的第一输入端子,并且输出电压out被输入到or电路244的第二输入端子。电流供给器245依据or电路244的输出电平在将具有基准电流量的电流供给到比较器241和将具有从基准电流量起增加的电流量的电流供给到比较器241之间切换。

65.《比较器和电流供给器的配置》

66.图2是示出比较器241和电流供给器245的具体电路配置的示例的图。

67.比较器241包括pmos晶体管241a和241b、电流镜cm241、缓冲器bf、钳位器clp和分压电阻器r21至r24。

68.pmos晶体管241a的源极连接到电流供给器245。pmos晶体管241a的栅极被供给有预定基准电压ref,该预定基准电压ref是通过利用分压电阻器r21和r22将高于第二接地gnd2的电压除以基准电压(作为示例,5v)(下文中称为上侧电压)而得到的。

69.pmos晶体管241b的源极连接到电流供给器245。pmos晶体管241b的栅极被供给有分压电压mcd,该分压电压mcd是通过利用分压电阻器r23和r24对第一栅极电压gt(参见图1)进行分压而得到的。

70.配置有pmos晶体管的钳位器clp的源极和栅极连接到用于上侧电压的施加端子。钳位器clp的漏极连接到pmos晶体管241b的栅极。

71.电流镜cm241配置有nmos晶体管n1和n2。更具体地,nmos晶体管n1的漏极和栅极短路。nmos晶体管n1和n2的栅极连接在一起。nmos晶体管n1和n2的源极都连接到第二接地gnd2的施加端子。

72.pmos晶体管241a的漏极连接到nmos晶体管n1的漏极。出现在pmos晶体管241b的漏极和nmos晶体管n2的漏极连接在一起的节点n241处的信号经由缓冲器bf被输出为比较信号cmp(参见图1)。

73.电流供给器245包括恒流源245a、pmos晶体管(开关)245c、配置有pmos晶体管的电流镜cm1和配置有pmos晶体管的电流镜cm2。

74.电流镜cm1包括作为输入侧晶体管的pmos晶体管pm1,并且将由恒流源245a生成的输入电流i1乘以1,以便输出该结果作为输出电流i2。

75.电流镜cm2包括作为输入侧晶体管的pmos晶体管pm1,并且将输入电流i1乘以x(x》1)以便输出该结果作为输出电流i3。pmos晶体管245c的漏极连接到电流镜cm2的输出侧pmos晶体管pm2的源极,并且pmos晶体管245c的源极连接到上侧电压的施加端子。pmos晶体管245c的栅极被供给有or电路244的输出信号。因此,当or电路244的输出处于低电平并且pmos晶体管245c导通时,生成输出电流i3。当or电路244的输出处于高电平并且pmos晶体管245c关断时,未生成输出电流i3。

76.输出电流i2和i3被结合在一起以生成供给电流i4。当未生成输出电流i3时,输出电流i2本身成为供给电流i4。供给电流i4在pmos晶体管241a和241b之间分配并提供给pmos晶体管241a和241b。

77.这里,供给电流i4在流过供给电流i4的pmos晶体管241a和241b的电流之间如何分配是依据基准电压ref和分压电压mcd而改变的。

78.当分压电压mcd低于基准电压ref时,pmos晶体管241b比pmos晶体管241a允许更多的电流流过,因此比较信号cmp处于高电平。

79.相反,当分压电压mcd高于基准电压ref时,pmos晶体管241a比pmos晶体管241b允许更多的电流流过,因此比较信号cmp处于低电平。

80.因此,在图1所示的配置中,通过比较器241将第一栅极电压gt与之进行比较的基准电压vref由基准电压ref和生成分压mcd的分压比限定。

81.当pmos晶体管245c根据or电路244的输出而关断时,未生成输出电流i3,因此具有基于输出电流i2生成的基准电流量的供给电流i4在pmos晶体管241a和241b之间分配并提供给pmos晶体管241a和241b。

82.相比之下,当pmos晶体管245c根据or电路244的输出而导通时,生成输出电流i3,因此具有从基准量起增加的电流量的供给电流i4(即,通过将输出电流i2与i3结合在一起而生成的电流)在pmos晶体管241a和241b之间分配并提供给pmos晶体管241a和241b。因此,比较器241的操作速度提升。

83.《镜像钳位电路的操作》

84.接下来,将基于先前描述的图1中的配置和图3中的时序图来描述镜像钳位电路24的操作。图3自上而下示出了输出电压out、第一栅极电压gt、比较信号cmp、第二栅极电压mcg、作为or电路244的输出的or输出a、以及来自电流供给器245的供给电流i。在先前描述的图2的配置中,供给电流i对应于供给电流i4。

85.在图3中,紧接着输出电压out从高电平变为低电平的时刻t1之前,第一栅极电压gt处于高电平,因此比较信号cmp处于低电平。当输出电压out处于高电平时,如果nmos开关243导通,则过电流从out端子经由电阻器r1和mc端子流到nmos开关243,因此优选nmos开关243保持关断。因此,当输出电压out处于高电平时,锁存电路242将第二栅极电压mcg锁存为低电平。由于输出电压out处于高电平,所以or输出a处于高电平。所以,图2中的pmos晶体管245c关断,并且供给电流i处于基准电平。

86.当输出电压out在时刻t1从高电平变为低电平时,由于电阻器r1,第一栅极电压gt开始从输出电压out缓慢下降。当输出电压out处于低电平时,锁存电路242输出比较信号cmp的电平本身作为第二栅极电压mcg。

87.因此,输出电压out和第二栅极电压mcg都处于低电平,因此or输出a处于低电平。因此,图2中的pmos晶体管245c被接通,并且供给电流i现在具有从基准电平起增加的电平。以这种方式,比较器241的操作速度可以预先提升,以便为了由比较器241检测由于第一栅极电压gt的下降而已经达到基准电压vref的第一栅极电压gt而做好准备。

88.然后,当第一栅极电压gt在时刻t2下降并达到基准电压vref时,比较器241将比较信号cmp变为高电平,并且第二栅极电压mcg也变为高电平。因此,nmos开关243被接通,nmos晶体管m1的vgs被强制为大约0v,并且可以防止nmos晶体管m1的栅极电压的上升。以这种方式,可以防止nmos晶体管m1的错误导通。

89.由于第二栅极电压mcg处于高电平,所以or输出a处于高电平,并且供给电流i下降到基准电平。

90.在时刻t2之后,第一栅极电压gt下降至低电平。

91.然后,当输出电压out在时刻t3从低电平变为高电平时,第一栅极电压gt开始缓慢上升,并且第二栅极电压mcg被锁存电路242锁存为低电平,如前所述。因此,nmos开关243被关断。由于输出电压out处于高电平,所以or输出a处于高电平,并且供给电流i处于基准电平。

92.然后,当第一栅极电压gt在时刻t4上升至基准电压vref时,比较信号cmp变为低电平。在时刻t4之后,第一栅极电压gt上升至高电平。

93.如上所述,仅在输出电压out和第二栅极电压mcg都处于低电平的有限时段(从时刻t1到时刻t2的时段)期间供给电流i增加。因此,可以降低功耗,同时仅在必要时提高比较器241的操作速度。

94.《变型例》

95.图4是示出根据前述实施例的变型例的包括镜像钳位电路24x的栅极驱动器10的配置的图。

96.图4中所示的镜像钳位电路24x的配置与先前描述的实施例(图1)中的镜像钳位电路的配置的差异在于,镜像钳位电路24x包括延迟电路246。

97.更具体地,延迟电路246设置在锁存部件242之后的级中,并且延迟从锁存电路242输出的第二栅极电压mcg,以便将延迟信号dly输出到or电路244的第一输入端子。

98.图5是示出根据这样的变型例的镜像钳位电路24x的操作的时序图。

99.在图5所示的时刻t1,当输出电压out从高电平变为低电平时,or电路244的or输出a从高电平变为低电平,并且供给电流i增加到基准电平以上。然后,当输出电压out在时刻t2下降至基准电压vref时,比较信号cmp变为高电平,并且第二栅极电压mcg变为高电平。因此,nmos开关243被接通。

100.此后,在从时刻t2延迟了延迟时间td的时刻t21处,延迟信号dly变为高电平。因此,or输出a变为高电平,并且供给电流i下降到基准电平。

101.这里,如图5所示,延迟时间td被设定为长于第一栅极电压gt需要从基准电压vref下降到低电平的时间tgt。以这种方式,直到第一栅极电压gt完全变为低电平,供给电流i可以保持稳定而不出现变化。

102.《其他》

103.应当理解,上述实施例在每个方面都是说明性的而非限制性的。本发明的范围不由上文给出的实施例的描述限定,而是由所附权利要求书限定,并且包含在不脱离与权利要求书等同的范围和意义的情况下进行的任何修改。

104.工业适用性

105.本发明可应用于例如栅极驱动器。

106.附图标记列表

107.10:栅极驱动器,1:初级电路,11:第一施密特触发器,12:第二施密特触发器,13:and电路,14:脉冲生成器,15:第一uvlo电路,2:次级电路,21:逻辑电路,22:pmos晶体管,23:nmos晶体管,24:镜像钳位电路,241:比较器,242:锁存电路,243:nmos开关,244:or电路,245:电流供给器,246:延迟电路,25:第二uvlo电路,26:ovp电路,r1:电阻器,m1:nmos晶体管。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。