1.本发明涉及一种信号检测电路,特别是涉及一种可降低制程偏移影响的信号检测电路。

背景技术:

2.在现有的检测信号电路中,为了检测待测信号的大小,经常为待测信号与参考电压设置两个独立的电流路径,经过振幅检测器分别滤成直流电压后,再通过比较器来比较信号大小。

3.然而,在上述的架构中,在制作两个独立的电流路径时,常因制程偏移量的不同而造成比较器比较后的误差量较大的问题。

4.因此,如何通过电路设计的改良,来降低制程偏移影响,以克服上述缺陷,已成为该领域内所需要解决的重要课题之一。

技术实现要素:

5.本发明所要解决的技术问题在于,针对现有技术的不足提供一种可降低制程偏移影响的信号检测电路。

6.为了解决上述的技术问题,本发明所采用的一种技术方案是提供一种信号检测电路,其包括输入开关电路、振幅检测电路、时钟产生电路及积分电路。输入开关电路经配置以接收参考电压及输入电压,且由切换信号组控制,以选择性地输出该参考电压或该输入电压。振幅检测电路经配置以对该输入开关电路的输出进行检测,以对应产生振幅电压。时钟产生电路经配置以产生该切换信号组。其中,该切换信号组用于控制该输入开关电路交替进入一第一阶段及一第二阶段,且该输入开关电路经控制以在该第一阶段输出该参考电压,且在该第二阶段输出该输入电压。积分电路经配置以将该振幅电压作为输入并进行累计,并在一预定时间区间内产生对应一累计结果的一积分电压。其中,该预定时间区间包括以该第一阶段及该第二阶段为循环的多个周期。

7.本发明的一个有益效果在于,本发明所提供的信号检测电路,通过使用输入开关电路选择让输入信号以及参考电压在不同阶段进入振幅检测电路与积分电路,由于共用后端的电路,输入信号与参考电压将经历相同的电路偏移量,因此,可以减少采用不同路径时,因制程偏压产生的误差。

8.为了能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与图示,然而所提供的图示仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

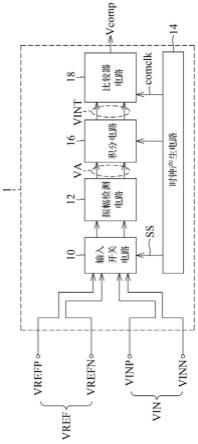

9.图1为本发明实施例的信号检测电路的功能模块图。

10.图2为本发明实施例的信号检测电路的电路布局图。

11.图3为本发明实施例的信号检测电路的第一信号时序图。

12.图4为本发明实施例的信号检测电路的第二信号时序图。

13.图5为本发明另一实施例的信号检测电路的电路布局图。

具体实施方式

14.以下通过特定的具体实施例来说明本发明所公开的涉及“信号检测电路”的实施方式,本领域技术人员可由本说明书所公开的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以实施或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本发明的构思下进行各种修改与变更。另外,事先声明,本发明的附图仅为简单示意说明,并非根据实际尺寸所描绘。以下实施例将进一步详细说明本发明的相关技术内容,但所公开的内容并非用以限制本发明的保护范围。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

15.图1为本发明实施例的信号检测电路的功能模块图。参阅图1所示,本发明实施例提供一种信号检测电路1,其包括输入开关电路10、振幅检测电路12、时钟产生电路14及积分电路16。

16.输入开关电路10经配置以接收参考电压vref及输入电压vin,且由切换信号组ss控制,以选择性地输出参考电压vref或输入电压vin。

17.请先参阅图2,图2为本发明实施例的信号检测电路的电路布局图。举例而言,参考电压vref为一对差分参考电压,包括第一参考电压vrefp及第二参考电压vrefn,且输入电压vin为一对差分输入电压,包括第一输入电压vinp及第二输入电压vinn。

18.在图2的实施例中,响应于输入电压vin为差分信号,输入开关电路10可例如为一复用器,其电路简化后可如图2所示包括第一开关s1、第二开关s2、第三开关s3及第四开关s4,且具有第一输出端o1及第二输出端o2。第一开关s1、第二开关s2、第三开关s3及第四开关s4可分别为n型或p型的金属氧化物半导体场效电晶体(metal oxide semiconductor field effect transistor,mosfet),但本发明不限于此。

19.其中,第一开关s1连接于第一输出端o1且接收第一参考电压vrefp,第二开关s2连接于第一输出端o1且接收第一输入电压vinp,第三开关s3连接于第二输出端o2且接收第二输入电压vinn,第四开关s4连接于第二输入端o2且接收第二参考电压vrefn。

20.请再次参考图1,振幅检测电路12用于对输入开关电路10的输出进行检测,以对应产生振幅电压va。举例而言,振幅检测电路12可为图2的整流器120,或是任何能将输入信号依据其大小转换成单纯输出高电位或低电位的电路,但本发明不限于此。

21.如图2所示,整流器120可具有第一检测输出端do1及第二检测输出端do2,且经配置以对应第一输出端o1及第二输出端o2的输出于第一检测输出端do1及第二检测输出端do2产生包括第一振幅电压va1及第二振幅电压va2的振幅电压va。

22.另一方面,时钟产生电路14用以产生切换信号组ss(如图1所示)。切换信号组ss主要用于控制输入开关电路10交替进入第一阶段及第二阶段。详细而言,在第一阶段下,输入开关电路10经控制以输出参考电压vref,且在第二阶段输出输入电压vin。

23.此外,当上述切换方式应用于图2的实施例时,切换信号组ss可包括第一切换信号φ1及第二切换信号φ2,且第一切换信号φ1用于控制第一开关s1及第四开关s4在第一阶段导通,第二切换信号φ2用于控制第二开关s2及第三开关s3在第二阶段导通,以使输入开

关电路10在第一阶段于第一输出端o1及第二输出端o2分别输出第一参考电压vrefp及第二参考电压vrefn,以及在第二阶段于第一输出端o1及第二输出端o2分别输出第一输入电压vinp及第二输入电压vinn。

24.请再次参考图1,积分电路16用以将振幅电压va作为输入并进行累计,并在预定时间区间内产生对应累计结果的积分电压vint。其中,预定时间区间涵盖以第一阶段及第二阶段为循环的多个周期。

25.举例而言,积分电路16可在单一周期中,分别对第一阶段下的振幅电压va(该阶段为根据参考电压vref产生)及第二阶段下的振幅电压va(该阶段为根据输入电压vin产生)采样后执行减法处理。因此,经过相当于该预定时间区间的多个周期后,即可依据所累计的积分电压vint判断输入电压vin是高于或低于参考电压vref。

26.以此方式,请参考图2,积分电路16可包括采样电路160及积分放大器162。其中,采样电路160用以在第一阶段对第一振幅电压va1及第二振幅电压va2采样。

27.如图2所示,采样电路160可包括第一采样电容c1、第二采样电容c2、第五开关s5、第六开关s6、第七开关s7及第八开关s8。第五开关s5、第六开关s6、第七开关s7及第八开关s8可分别为n型或p型的金属氧化物半导体场效电晶体(metal oxide semiconductor field effect transistor,mosfet),但本发明不限于此。

28.第一采样电容c1连接于第一检测输出端do1及第一节点n1之间,第二采样电容c2连接于第二检测输出端do2及第二节点n2之间。第五开关s5的一端连接于第一节点n1,另一端接收共模电压vcm。第六开关s6一端连接于第二节点n2,另一端接收共模电压vcm。第七开关s7连接于第一节点n1及第三节点n3之间,第八开关s8连接于第二节点n2及第四节点n4之间。

29.另一方面,积分放大器162用于在第二阶段将采样电路160采样的第一振幅电压va1及第二振幅电压va2进行保持以分别进行累计。

30.因此,如图2所示,积分放大器162可包括全差分放大器fda、第一反馈电容cfb1及第二反馈电容cfb2。

31.全差分放大器fda具有一非反转输入端(左侧 端)、一反转输入端(左侧-端)、一反转输出端(右侧 端)及一非反转输出端(右侧-端),其中,非反转输入端连接于第三节点n3,且反转输入端连接于第四节点n4。第一反馈电容cfb1连接于非反转输入端及反转输出端之间,第二反馈电容cfb2连接于反转输入端及非反转输出端之间。

32.如图2所示,第五开关s5及第六开关s6由第一切换信号φ1控制,以在第一阶段导通,在第二阶段关断,第七开关s7及第八开关s8由第二切换信号φ2控制,以在第二阶段导通,在第一阶段关断。在本发明的实施例中,积分电路16可用低通滤波器或是电容来进行替换,但本发明不限于此。

33.以下将参阅图3说明图2的信号检测电路的检测机制。图3为本发明实施例的信号检测电路的第一信号时序图。如图所示,示出了包括时间点t1至时间点t9在内的时序图。其中,在图3的实施例中,参考电压vref在时间点t1至t5的区间内小于输入电压vin,在时间点t5至时间点t9的区间内大于输入电压vin。

34.以下以时间点t2作为起始点,在时间点t2至t3之间,进入第一阶段,第一切换信号φ1为高电位,第二切换信号φ2为低电位,代表第一开关s1、第四开关s4、第五开关s5及第

六开关s6均导通,第二开关s2、第三开关s3、第七开关s7及第八开关s8均关断,此时,参考电压vref输入整流器120,产生低电位的振幅电压va。针对此振幅电压va,第一采样电容c1对第一振幅电压va1及共模电压vcm之间的差值采样,第二采样电容c2对第二振幅电压va2及共模电压vcm之间的差值采样,据此可对振幅电压va采样。

35.接着,在时间点t3至t4之间,进入第二阶段,第一切换信号φ1为低电位,第二切换信号φ2为高电位,代表第一开关s1、第四开关s4、第五开关s5及第六开关s6均关断,第二开关s2、第三开关s3、第七开关s7及第八开关s8均导通,此时,输入电压vin输入整流器120,产生高电位的振幅电压va。此高电位的振幅电压va将与第一阶段已经采样的低电位的振幅电压va相减,进而将相减的结果经由全差分放大器fda放大后保持于第一反馈电容cfb1及第二反馈电容cfb2,以产生积分电压vint。

36.由图3可知,由于参考电压vref在时间点t2至t5的区间内小于输入电压vin,因此积分电压vint由时间点t2至t5逐渐递减,据此,在以第一阶段及第二阶段为循环的多个周期后,例如时间点t5,可将积分电压vint输出作为累计结果,据此判定参考电压vref与输入电压vin之间的大小关系。

37.另一方面,由于参考电压vref在时间点t6至t9的区间内大于输入电压vin,因此积分电压vint由时间点t6至t9逐渐递增,也可在多个周期后将递增后的积分电压vint输出作为累计结果。

38.另外,需要说明的是,图2的积分放大器162还包括第一重置开关sr1、第二重置开关sr2及第三重置开关sr3。第一重置开关sr1连接于全差分放大器fda的非反转输入端及反转输出端之间,第二重置开关sr2连接于全差分放大器fda的反转输入端及非反转输出端之间,第三重置开关sr3连接于第三节点n3及第四节点n4之间。

39.相应的,时钟产生电路14还产生一重置信号rst,以在预定时间区间之前及之后的一重置时间区间内控制第一重置开关sr1、第二重置开关sr2及第三重置开关sr3导通,且在预定时间区间内关断。例如,重置时间区间可为图3的时间点t1至t2之间以及t5至t6之间,预定时间区间可例如为时间点t2至t5之间。在第一重置开关sr1、第二重置开关sr2及第三重置开关sr3导通后,将可重置所保持的积分电压vint,以重新进行检测。

40.以下将参阅图4,以另一实施例说明图2的信号检测电路的检测机制。图4为本发明实施例的信号检测电路的第二信号时序图。如图所示,示出了包括时间点t1至时间点t9在内的时序图。其中,在图4的实施例中,参考电压vref不变,而输入电压在时间点t1至t5的区间内小于参考电压vref,在时间点t5至t9的区间内大于参考电压vref。

41.以下以时间点t2作为起始点,在时间点t2至t3之间,进入第一阶段,第一切换信号φ1为高电位,第二切换信号φ2为低电位,代表第一开关s1、第四开关s4、第五开关s5及第六开关s6均导通,第二开关s2、第三开关s3、第七开关s7及第八开关s8均关断,此时,参考电压vref输入整流器120,产生高电位的振幅电压va。针对此振幅电压va,第一采样电容c1对第一振幅电压va1及共模电压vcm之间的差值采样,第二采样电容c2对第二振幅电压va2及共模电压vcm之间的差值采样,据此可对振幅电压va采样。

42.接着,在时间点t3至t4之间,进入第二阶段,第一切换信号φ1为低电位,第二切换信号φ2为高电位,代表第一开关s1、第四开关s4、第五开关s5及第六开关s6均关断,第二开关s2、第三开关s3、第七开关s7及第八开关s8均导通,此时,输入电压vin输入整流器120,产

生低电位的振幅电压va。此低电位的振幅电压va将与第一阶段已经采样的高电位的振幅电压va相减,进而将相减的结果经由全差分放大器fda放大后保持于第一反馈电容cfb1及第二反馈电容cfb2,以产生积分电压vint。

43.由图4可知,由于参考电压vref在时间点t2至t5的区间内大于输入电压vin,因此积分电压vint由时间点t2至t5逐渐递增,据此,在以第一阶段及第二阶段为循环的多个周期后,例如时间点t5,可将积分电压vint输出作为累计结果,据此判定参考电压vref与输入电压vin之间的大小关系。

44.因此,上述实施例使用输入开关电路10选择让输入电压vin以及参考电压vref在不同阶段进入振幅检测电路12与积分电路16,由于共用后端的电路,输入电压vin与参考电压vref将经历相同的电路偏移量,因此,可以减少采用不同路径时,因制程偏压产生的误差。

45.在一些实施例中,信号检测电路1还选择性地包括比较器电路18,经配置以通过其之第一输入端及第二输入端接收积分电路16产生的积分电压vint(即图2中反转输出端及非反转输出端的电压)并进行比较,以产生比较结果信号vcomp作为累计结果。相应的,在此实施例中,时钟产生电路14还用以产生比较时钟信号comclk,以在预定时间区间(例如图3、4的时间点t2至t5)结束时控制比较器电路18产生并输出比较结果信号vcomp。

46.请先参阅图5,图5为本发明另一实施例的信号检测电路的电路布局图。在另一实施例中,积分放大器162还选择性地包括斩波电路(chopping circuit),例如分别连接于全差分放大器fda的输入端及输出端的第一斩波电路cc1及第二斩波电路cc2,其可被设计在特定时间点作动。第一斩波电路cc1具有分别连接第三节点n3及第四节点n4的二输入端,及分别连接非反转输入端(左侧 端)及反转输入端(左侧-端)的二输出端。第二斩波电路cc2具有分别连接反转输出端(右侧-端)及非反转输出端(右侧 端)的二输入端及分别连接比较器电路18的第一输入端及第二输入端的二输出端。

47.例如,第一斩波电路cc1及第二斩波电路cc2可于预定数量的多个周期内一起作动,使比较器电路18可将信号传输路径上的偏移量抵消,使比较结果信号vcomp最佳化。

48.举例而言,上述偏移量可为全差分放大器fda所产生的偏移量,而特定数量的多个周期可为4个周期。在4个周期中的第一区间,例如,前两个周期中,第一斩波电路cc1及第二斩波电路cc2可经配置以依据第一切换信号φ1及第二切换信号φ2,使比较器电路18比较反转输出端(右侧-端)的信号与非反转输出端(右侧 端)的信号,而在4个周期中的第二区间,例如,后两个周期中,第一斩波电路cc1及第二斩波电路cc2经配置以依据第一切换信号φ1及第二切换信号φ2,使比较器电路18转换为比较非反转输出端(右侧 端)的信号与反转输出端(右侧-端)的信号,可达成平均抵消两输出端偏移量的效果,使比较结果信号vcomp最佳化。

49.实施例的有益效果:

50.本发明的一个有益效果在于,本发明所提供的信号检测电路,通过使用输入开关电路选择让输入信号以及参考电压在不同阶段进入振幅检测电路与积分电路,由于共用后端的电路,输入信号与参考电压将经历相同的电路偏移量,因此,可以减少采用不同路径时,因制程偏压产生的误差。

51.另一方面,本发明所提供的信号检测电路可选择性地包括比较器电路及斩波电

路,以实现平均抵消两输出端偏移量的效果,并产生最佳化的比较结果信号vcomp作为累计结果。

52.以上所公开的内容仅为本发明的优选实施例,本发明所要求的专利保护范围并不以此为限,所以凡是运用本发明说明书及图示内容所做的等效技术变化,均在本发明所要求的专利保护范围内。

53.附图标记说明:

54.1:信号检测电路

55.10:输入开关电路

56.12:振幅检测电路

57.120:整流器

58.14:时钟产生电路

59.16:积分电路

60.18:比较器电路

61.160:采样电路

62.162:积分放大器

63.c1:第一采样电容

64.c2:第二采样电容

65.cc1:第一斩波电路

66.cc2:第二斩波电路

67.cfb1:第一反馈电容

68.cfb2:第二反馈电容

69.comclk:比较时钟信号

70.do1:第一检测输出端

71.do2:第二检测输出端

72.fda:全差分放大器

73.n1:第一节点

74.n2:第二节点

75.n3:第三节点

76.n4:第四节点

77.o1:第一输出端

78.o2:第二输出端

79.rst:重置信号

80.s1:第一开关

81.s2:第二开关

82.s3:第三开关

83.s4:第四开关

84.s5:第五开关

85.s6:第六开关

86.s7:第七开关

87.s8:第八开关

88.sr1:第一重置开关

89.sr2:第二重置开关

90.sr3:第三重置开关

91.ss:切换信号组

92.t1至t9:时间

93.va:振幅电压

94.va1:第一振幅电压

95.va2:第二振幅电压

96.vcm:共模电压

97.vcomp:比较结果信号

98.vin:输入电压

99.vinn:第二输入电压

100.vinp:第一输入电压

101.vint:积分电压

102.vref:参考电压

103.vrefn:第二参考电压

104.vrefp:第一参考电压

105.φ1:第一切换信号

106.φ2:第二切换信号

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。