一种基于aether工具的pdk开发方法

技术领域

1.本发明涉及pdk开发领域,尤其涉及一种基于aether工具的pdk开发方法。

背景技术:

2.eda工具可以大幅度提高芯片设计的效率,使得芯片设计成本可以控制在一个合理的范围内。与eda工具紧密绑定的半导体ip,伴随着eda工具的进步获得了蓬勃发展。国内下游应用产业的高速发展,为国产eda企业成长提供了广阔的空间。而现实情况是,工艺设计组件cadence pdk以及ads pdk成为下游厂商几乎是唯一选择。选择性的匮乏,也就意味着国内产业链存在有着极大的风险值。此方法配合设计公司可以让国内整个eda市场形成一个良性的闭环。

3.此外,目前主流的pdk开发方法是pdk开发工程师从工厂得到的工艺参数文件获取工艺信息,各部分的工程师独立完成,缺少各部分之间的配合。特别是在pdk的回调功能函数以及版图开发方法中,对于代码中存在的语法错误乃至代码要实现的效果,需要在搭建好pdk基本框架的基础上,软件才能调用pdk,而后才是验证代码的正确性,验证过程繁琐且冗杂。期间发现一些bug需要人员从pdk工具包里众多的可能的部分反复检查,凭借软件提示和经验判断问题可能存在的位置,耗费大量的时间和精力,对于经验相对较少的开发人员,很难判断问题存在的位置。

技术实现要素:

4.为解决现有技术存在的不足,本发明提出一种基于华大九天开发的aether工具下的pdk开发方法,核心思想是通过pbq软件与aether工具的相互配合,可实时判断代码的语法正确性以及功能的完整性;通过pdk基础包以及drc、lvs文件的相互配合验证,面对问题可迅速抉择出修改哪部分能成为问题最优解。具有整体架构的优势,提高了设计的正确性,极大的缩短了开发周期。

5.另外本发明旨在加速pdk开发,增加ic设计者对eda工具的可选选项。同时减少pdk设计中出现的错误,去除传统pdk开发验证的冗长操作。

6.为了实现上述目的,本发明采用以下技术方案:

7.一种基于aether工具的pdk开发方法,包括以下步骤:

8.s1、准备阶段:

9.获取待处理的文件,所述文件包括:用于设计器件缩略图的symbol和开发回调功能函数callback的器件开发文档、用于撰写设计规则检查drc文件的工艺设计文档、用于原理图仿真的器件模型文件;

10.根据所述器件开发文档创建:callback文件夹、src文件夹、tf文件夹;

11.自定义库名称,建立以库名称命名的文件夹;

12.创建两份用于argus软件使用的rule文件,其中,第一rule文件用于设计规则检查drc,第二rule文件用于版图原理图匹配检查lvs;

13.s2、开发阶段:

14.s2-1:在pbq软件下新建epdk工程;按如下方式设置epdk工程的路径参数:

15.将库路径,设置为所述s1中创建的库名称命名的文件夹的路径,

16.将回调功能函数callback路径,设置为所述s1中创建的所述callback文件夹的路径,

17.将源代码路径,设置为所述s1中创建的所述src文件夹的路径,

18.将技术文件路径,设置为所述s1中创建的所述tf文件夹;

19.路径参数设置完成后,pbq软件会自动建立epdk工程;

20.根据所述s1中的所述器件开发文档,在epdk工程里编写display.drf和techfile.tf

21.s2-2:根据所述s1中的器件开发文档和工艺设计文档,

22.在pbq软件里,调用aether工具,在aether工具里画出器件的symbol

23.s2-3:将所述s2-2得到的一个symbol复制成2个,分别命名为spectre、sdl,分别用于生成spectre网表和sdl网表;其中spectre网表于原理图仿真,sdl网表用于lvs;

24.s2-4:根据所述s1中的器件开发文档和工艺设计文档,

25.在pbq软件里选择epdk工程下的器件,

26.在pbq软件里,调用aether工具,在aether工具里编辑器件的用于描述单个组件和组件库的参数和参数属性的cdf

27.在aether工具里为器件添加参数,设置属性;

28.s2-5:根据所述s1中的器件开发文档和工艺设计文档,

29.在pbq软件里,运用tcl语言开发出callback对应的功能,以达到规避常见错误;

30.s2-6:使用pbq软件的检查symbol功能,调用aether工具,在aether工具里改变器件的参数值,判断是否达到所述s2-5描述的规避常见错误的效果,若未达到,返回s2-5,成功则进入s2-7;

31.s2-7:根据所述s1中的器件开发文档和工艺设计文档,

32.在pbq软件里,运用python语言开发与器件对应的版图

33.s2-8:选择pbq软件里的查看版图的功能,调用aether工具,在aether工具里改变器件的参数值,判断版图是否达到所述s1中的器件开发文档要求的效果,若未达到,返回s2-7,若达到,则进行下一步;

34.s2-9:利用pbq软件的编译功能编译出epdk基础包;

35.s2-10:利用argus软件下的drstudio工具,

36.导入所述s1中创建的所述第一rule文件,

37.根据所述s1中的工艺设计文档编写drc代码,存入第一rule文件,形成到更新后的第一rule文件;

38.drstudio工具具有判断函数选择是否符合要求的功能,使用上述功能,判断函数选择是否符合要求;

39.s2-11:利用argus软件下的drstudio工具,

40.导入所述s1中创建的所述第二rule文件,

41.根据所述s1中的工艺设计文档,所述s2-3中的sdl网表以及所述s2-7中开发出的

版图,编写lvs代码,存入第二rule文件,形成到更新后的第二rule文件;

42.drstudio工具具有判断函数选择是否符合要求的功能,使用上述功能,判断函数选择是否符合要求;

43.s3、联合测试

44.s3-1:在aether工具里加载所述s2-9中得到的所述pdk基础包,调入器件,进行网表生成判断,判断spectre是否正常输出spectre网表,spectre网表格式是否符合仿真要求,若不能,运用tcl语言编写网表函数,返回步骤s2-4;

45.s3-2:在aether工具里加载所述s2-9中得到的所述pdk基础包,调入器件,进行网表生成判断,判断sdl格式网表是否符合所述s2-11步骤需要的网表格式,若不能,运用tcl语言编写网表函数,返回步骤s2-4;

46.s3-3:在aether工具里读取所述s2-9中得到的所述pdk基础包,搭测试案例,在argus软件里,读取所述s2-10中更新后的第一rule文件,进行drc测试,判断是否符合所述s1中所述工艺文档要求,若不符合返回s2-10修改;

47.s3-4:在aether工具里读取所述s2-9中得到的所述pdk基础包,搭测试案例,在argus软件里,读取所述s2-11中更新后的第二rule文件,进行lvs测试,判断是否符合所述s1中所述工艺文档要求,若不符合返回s2-11修改;

48.s4:将以下四个部分放入同一个文件目录下,形成完整的pdk包:

49.所述s1中获取的所述器件模型文件,

50.所述s2-9中得到的所述pdk基础包,

51.所述s2-10中更新后的第一rule文件,作为drc文件;

52.所述s2-11中更新后的第二rule文件,作为lvs文件。

53.作为优选,在所述s2-5中,开发出所述callback对应的功能之后,还包括以下步骤:

54.采用pbq软件的编译功能,判断是否存在语法错误,若存在错误可在pbq工具里修改,若编译通过,则进入s2-6。

55.作为优选,所述s2-7中,开发出与器件对应的所述版图之后,还包括以下步骤:

56.采用pbq软件的编译功能,判断是否存在语法错误,若存在错误可在pbq软件里修改,若编译通过,则进入s2-8。

57.作为优选,所述s4之后,还包括以下步骤:

58.s5:撰写pdk使用说明文档、lvs使用说明文档、drc使用说明文档。

59.本发明具有如下有益效果:通过规范化的方法,减少pdk工具包开发过程中的失误,实时验证功能完整性,可以提高开发过程中验证效率。同时联合验证方法,面对问题,能快速抉择出修改哪部分可以作为最优解。能增加市场上eda工具ip的可选择项,降低ic设计成本。

附图说明

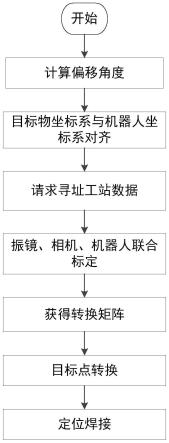

60.图1为本发明的流程图

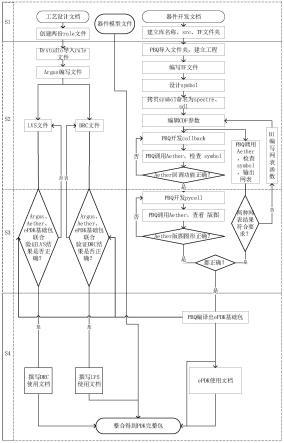

61.图2为本发明的判断是否编写网表函数流程图

具体实施方式

62.为了使本发明实施方式的目的、技术方案和优点更加清楚,下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。因此,以下对在附图中提供的本发明的实施方式的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施方式。在本技术中,某些需要应用到本领域的公知技术或常规技术手段时,申请人可能存在没有在文中具体的阐述该公知技术或/和常规技术手段是一种什么样的技术手段,但不能以文中没有具体公布该技术手段,而认为本技术不符合专利法第二十六条第三款的情况。

63.实施例:如图1所示,一种eda工具aether下pdk开发方法,包括:

64.s1、准备阶段:

65.从工厂获取待处理的文件,所述文件包括:用于设计器件缩略图的symbol和开发回调功能函数callback的器件开发文档、用于撰写设计规则检查drc文件的工艺设计文档、用于原理图仿真的器件模型文件;

66.进行文件准备,准备的文件内容包括:器件开发文档、工艺设计文档;

67.根据所述器件开发文档创建:callback文件夹、src文件夹、tf文件夹;

68.自定义器件库名称,建立以器件库名称命名的文件夹,该库文件夹名称决定了在aether工具里导入pbq软件编译出来的pdk基础包调用器件的时候,器件归属的器件库名称,后续开发不可返回更改。例如命名为

69.t_npa25_001_v1.0,意思是t公司的0.25微米氮化镓工艺器件库的001版本,创建的各个器件也都会存放在t_npa25_001_v1.0这个器件库底下;

70.创建两份用于argus软件使用的rule文件,其中,第一rule文件用于设计规则检查drc,第二rule文件用于版图原理图匹配检查lvs,例如命名为t_npa25_drc_v1.0.rule和t_npa25_lvs_v1.0.rule;

71.s2、开发阶段:

72.s2-1:在pbq软件下新建epdk工程;按如下方式设置epdk工程的路径参数:

73.将库路径,设置为所述s1中创建的库名称命名的文件夹的路径,

74.将回调功能函数callback路径,设置为所述s1中创建的所述callback文件夹的路径,

75.将源代码路径,设置为所述s1中创建的所述src文件夹的路径,

76.将技术文件路径,设置为所述s1中创建的所述tf文件夹;

77.路径参数设置完成后,pbq软件会自动建立epdk工程;

78.根据所述s1中的所述器件开发文档,在epdk工程里编写display.drf和techfile.tf。display.drf和techfile.tf决定版图的显示属性。display.drf用于显示各定义的各层的显示形状和色彩。techfile.tf用于定义各层的名称并给予各层唯一的编号。

79.s2-2:根据所述s1中的器件开发文档和工艺设计文档,

80.在pbq软件里,调用aether工具,在aether工具里画出器件的symbol

81.s2-3:将所述s2-2得到的一个symbol复制成2个,分别命名为spectre、sdl,分别用

于生成spectre网表和sdl网表;其中spectre网表于原理图仿真,sdl网表用于lvs;

82.s2-4:根据所述s1中的器件开发文档和工艺设计文档,

83.在pbq软件里选择epdk工程下的器件,

84.在pbq软件里,调用aether工具,在aether工具里编辑器件的用于描述单个组件和组件库的参数和参数属性的cdf

85.在aether工具里为器件添加参数,设置属性;

86.s2-5:根据所述s1中的器件开发文档和工艺设计文档,

87.在pbq软件里,运用tcl语言开发出callback对应的功能,以达到规避常见错误;

88.采用pbq软件的编译功能,判断是否存在语法错误,若存在错误可在pbq工具里修改,若编译通过,则进入s2-6

89.s2-6:使用pbq软件的检查symbol功能,调用aether工具,在aether工具里改变器件的参数值,判断是否达到所述s2-5描述的规避常见错误的效果,若未达到,返回s2-5,成功则进入s2-7;

90.s2-7:根据所述s1中的器件开发文档和工艺设计文档,

91.在pbq软件里,运用python语言开发与器件对应的版图

92.采用pbq软件的编译功能,判断是否存在语法错误,若存在错误可在pbq工具里修改,若编译通过,则进入s2-8

93.s2-8:选择pbq软件里的查看版图的功能,调用aether工具,在aether工具里改变器件的参数值,判断版图是否达到所述s1中的器件开发文档要求的效果,若未达到,返回s2-7,若达到,则进行下一步;

94.s2-9:利用pbq软件的编译功能编译出epdk基础包;

95.s2-10:利用argus软件下的drstudio工具,

96.导入所述s1中创建的所述第一rule文件,

97.根据所述s1中的工艺设计文档编写drc代码,存入第一rule文件,形成到更新后的第一rule文件;

98.drstudio工具具有判断函数选择是否符合要求的功能,使用上述功能,判断函数选择是否符合要求;

99.s2-11:利用argus软件下的drstudio工具,

100.导入所述s1中创建的所述第二rule文件,

101.根据所述s1中的工艺设计文档,所述s2-3中的sdl网表以及所述s2-7中开发出的版图,编写lvs代码,存入第二rule文件,形成到更新后的第二rule文件;

102.drstudio工具具有判断函数选择是否符合要求的功能,使用上述功能,判断函数选择是否符合要求;

103.s3:联合测试

104.s3-1:在aether工具里加载所述s2-9中得到的所述epdk基础包,调入器件,进行网表生成判断,判断spectre是否正常输出spectre网表,spectre网表格式是否符合仿真要求,若不能,运用tcl语言编写网表函数,返回步骤s2-4;

105.s3-2:在aether工具里加载所述s2-9中得到的所述epdk基础包,调入器件,进行网表生成判断,判断sdl格式网表是否符合所述s2-11步骤需要的网表格式,若不能,运用tcl

语言编写网表函数,返回步骤s2-4;

106.s3-3:在aether工具里读取所述s2-9中得到的所述epdk基础包,搭测试案例,在argus软件里,读取所述s2-10中更新后的第一rule文件,进行drc测试,判断是否符合所述s1中所述工艺文档要求,若不符合返回s2-10修改;

107.s3-4:在aether工具里读取所述s2-9中得到的所述epdk基础包,搭测试案例,在argus软件里,读取所述s2-11中更新后的第二rule文件,进行lvs测试,判断是否符合所述s1中所述工艺文档要求,若不符合返回s2-11修改;

108.s4:整合以下四个部分:

109.所述s1中得到的所述器件模型文件,

110.所述s2-9中得到的所述pdk基础包,

111.所述s2-10中更新后的第一rule文件,作为drc文件;

112.所述s2-11中更新后的第二rule文件,作为lvs文件。

113.并撰写pdk使用文档、drc使用文档、lvs使用文档,形成pdk完整包。

114.在pdk设计开发方法中,包含以下步骤与方法:

115.1.器件模型(device model);2.symbol&view;3.cdf(component description format,组件描述格式)&callback;4.pcell(parameterized cell,参数化单元);5.技术文件(technologyfile)pvrule(物理验证规则)文件;6.pdk验证;pdk的内容中包括设计规则文件、电学规则文件、版图层次定义文件、spice仿真模型、器件版图和器件定制参数等。本发明对其中的步骤3、4、6进行了改进,方便了pdk开发人员,提高了开发过程的规范性和便捷性,节省了开发时间,提高了准确率。

116.本技术设计到的一些缩略英文词汇注释如下:

117.pdk:工艺设计组件(全称为process design kit)

118.drc:设计规则检查(全称为design rule check)

119.lvs:版图原理图匹配检查(全称为layout versus schematics)

120.pcell:参数化单元(全称为parameterized cell)

121.cdf:组件描述格式(全称为component description format)

122.aether:aether是可提供完整的数模混合信号ic设计解决方案,包含设计数据库管理(design manager)、工艺管理(technology manager)、原理图编辑器(schematic editor)、混合信号设计仿真环境(mde)、版图编辑器(layout editor)和原理图驱动版图(schematic driven layout,sdl)等工具

123.argus:是与全定制ic设计平台aether和芯片精加工布局集成平台skipper协作,帮助ic设计人员进行drc(设计规则检查)、lvs(版图原理图匹配检查)、erc(电气规则检查)和lvl(版图与版图检查)的软件。

124.pbq:pbq是开发各种pdk,保证pdk质量的解决方案。它的主要目的是加速pdk开发和管理pdk项目高效,从而使您的设计顺利快速。它支持各种pdk项目管理、技术文件编辑、代码构建等功能编译和自动化质量保证。

125.epdk:empyrean pdk简称,表示华大九天工艺设计组件。

126.上述实施例仅列举了较佳的具体技术方案及技术手段,不排除在本发明权利要求范围内,有其他可以解决该技术问题的等换技术手段的替换形式,也应当理解为本发明要

求保护的内容。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。