1.本技术涉及电子电路技术领域,尤其涉及一种辅助电路及电子设备。

背景技术:

2.在电源向外界设备进行供电的时候,往往需要对供电系统和外置设备有保护功能,防止器件损害,或者线路损坏等。通常,实现保护功能往往需要借助于专用功能的芯片,然而,专用芯片对应的造价成本高。

技术实现要素:

3.本技术实施例公开了一种辅助电路及电子设备,用于保护供电系统的同时降低成本。

4.第一方面,本技术提供了一种辅助电路,所述辅助电路包括第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第一开关管q1、第二开关管q2、第一防反模块和第二防反模块,其中:所述第一电阻r1的第一端连接所述辅助电路的高压输入端vin ,所述第一电阻r1的第二端分别连接所述第二电阻r2的第一端、所述第三电阻r3的第一端和所述第一开关管q1的源极;所述第二电阻r2的第二端分别连接所述第四电阻r4的第一端、所述第二开关管q2的栅极和所述第一防反模块的第一端;所述第四电阻r4的第二端分别连接所述辅助电路的低压输入端vin-、所述第二开关管q2的源极和所述辅助电路的低压输出端vout-;所述第三电阻r3的第二端连接所述第一开关管q1的栅极和所述第二开关管q2的漏极;所述第一开关管q1的漏极连接所述第二防反模块的第一端;所述第一防反模块的第二端和所述第二防反模块的第二端连接所述辅助电路的高压输出端vout ;其中,所述第一开关管q1为p型mos管或p型晶体管,所述第二开关管q2为n型mos管或n型晶体管,所述第一防反模块为从自身第一端到第二端单向导通的模块,所述第二防反模块为从自身第一端到第二端单向导通的模块。

5.在本技术实施例中,摒弃了电路保护的专用芯片,使用简洁的电路逻辑实现过压、过流、短路和反接的保护,保证辅助电路的保护效果。此外,芯片的成本要远高于本技术实施例中辅助电路中的器件成本,因此,上述电路降低了产品实现的成本,增加电路方案布局的灵活性。

6.在一种可能的实现方式中,在正常工作状态下,所述第二开关管q2导通,所述第一开关管q1导通,所述辅助电路的高压输入端vin 到高压输出端vout 的通路导通;在过流状态下,所述辅助电路的高压输出端vout 将所述第二开关管q2的栅极电压拉低,所述第二开关管q2截止,所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述过流状态为所述辅助电路的电流超过阈值电流的状态;在过压状态下,所述第一防反模块和所述第二防反模块从自身的第二端到第一端

截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述过压状态为所述辅助电路的高压输出端vout 的电压超过阈值电压的状态。

7.在本技术实施例中,上述的辅助电路能够保证在正常电压电流范围内正常工作的同时,防止由于过流、过压等情况造成系统电源或者外置发生损坏的问题,从而可以保护供电过程中的电路的各个元器件。

8.在一种可能的实现方式中,在所述过流状态为短路状态的情况下,所述辅助电路的高压输出端vout 将所述第二开关管q2的栅极电压拉低为低压,所述第二开关管q2截止,所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述短路状态为所述辅助电路的高压输出端vout 和低压输出端vout-短接的状态;在反接状态下,所述第一防反模块和所述第二防反模块从自身的第二端到第一端截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述反接状态为外置电路的高压端与所述辅助电路的低压输出端vout-连接,且所述外置电路的低压端与所述辅助电路的高压输出端vout 连接的状态。

9.在本技术实施例中,上述的辅助电路能够保证在正常电压电流范围内正常工作的同时,防止由于短路、反接等情况造成系统电源或者外置发生损坏的问题,从而可以保护供电过程中的电路的各个元器件。

10.在一种可能的实现方式中,所述第一防反模块为第一二极管d1,所述第一二极管d1从自身第一端到第二端单向导通。这样,二极管能够作为最简单的单向导通器件控制电路的导通方向,防止电流倒灌,对系统电源损坏,对供电电路起到保护作用。

11.在一种可能的实现方式中,所述第二防反模块为第二二极管d2的情况下,所述第二二极管d2从自身的第一端到第二端单向导通;或,所述第二防反模块为第三开关管q3的情况下,所述第三开关管q3的栅极分别连接所述第三电阻r3的第二端、所述第二开关管q2的漏极和所述第一开关管q1的栅极;所述第三开关管q3的漏极连接所述第一开关管q1的漏极;所述第三开关管q3的源极连接所述第一防反模块的第二端和所述高压输出端vout ,所述第三开关管q3为p型mos管或p型晶体管,所述第三开关管q3的漏极为所述第二防反模块的第一端,所述第三开关管q3的源极为所述第二防反模块的第二端。这样,辅助电路能够将通过二极管或者p型开关管来确定其电流的导通方向,放置电流的倒灌,保护供电电路。

12.在一种可能的实现方式中,所述辅助电路包括所述控制端,所述控制端分别连接所述第二电阻r2的第二端、所述第四电阻r4的第一端、所述第二开关管q2的栅极和所述第一防反模块的第一端;在所述控制端的控制信号为高电平的情况下,所述第二开关管q2和所述第一开关管q1导通,所述辅助电路的高压输入端vin 到高压输出端vout 的通路导通;在所述控制端的控制信号为低电平的情况下,所述第二开关管q2和所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开。这样,控制端在能够在正常工作状态下,控制是否进行供电,提高了供电电路的可控性,也能避免在不需要供电的情况下依然供电的情况,避免能耗的浪费。

13.在一种可能的实现方式中,所述辅助电路输入端的高压输入端vin 和低压输入端vin-连接系统电源,所述系统电源用于向外置电路供电。这样,辅助电路的输入端能够连接系统电源,系统电源能够向外界供电,保证电路连接的完整性。

14.在一种可能的实现方式中,所述辅助电路输出端的高压输出端vout 和低压输出

端vout-连接外置电路,所述外置电路用于消费电量。这样,辅助电路的输出端能够外置电路,系统电源能够向这个外置电路进行供电,保证供电电路连接的完整性。

15.第二方面,本技术提供了一种电子设备,所述电子设备包括辅助电路,所述辅助电路包括第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第一开关管q1、第二开关管q2、第一防反模块和第二防反模块,其中:所述第一电阻r1的第一端连接所述辅助电路的高压输入端vin ,所述第一电阻r1的第二端分别连接所述第二电阻r2的第一端、所述第三电阻r3的第一端和所述第一开关管q1的源极;所述第二电阻r2的第二端分别连接所述第四电阻r4的第一端、所述第二开关管q2的栅极和所述第一防反模块的第一端;所述第四电阻r4的第二端分别连接所述辅助电路的低压输入端vin-、所述第二开关管q2的源极和所述辅助电路的低压输出端vout-;所述第三电阻r3的第二端连接所述第一开关管q1的栅极和所述第二开关管q2的漏极;所述第一开关管q1的漏极连接所述第二防反模块的第一端;所述第一防反模块的第二端和所述第二防反模块的第二端连接所述辅助电路的高压输出端vout ;其中,所述第一开关管q1为p型mos管或p型晶体管,所述第二开关管q2为n型mos管或n型晶体管,所述第一防反模块为从自身第一端到第二端单向导通的模块,所述第二防反模块为从自身第一端到第二端单向导通的模块。

16.在本技术实施例中,摒弃了电路保护的专用芯片,使用简洁的电路逻辑实现过压、过流、短路和反接的保护,保证辅助电路的保护效果。此外,芯片的成本要远高于本技术实施例中辅助电路中的器件成本,因此,上述电路降低了产品实现的成本,增加电路方案布局的灵活性。

17.在一种可能的实现方式中,在正常工作状态下,所述第二开关管q2导通,所述第一开关管q1导通,所述辅助电路的高压输入端vin 到高压输出端vout 的通路导通;在过流状态下,所述辅助电路的高压输出端vout 将所述第二开关管q2的栅极电压拉低,所述第二开关管q2截止,所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述过流状态为所述辅助电路的电流超过阈值电流的状态;在过压状态下,所述第一防反模块和所述第二防反模块从自身的第二端到第一端截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述过压状态为所述辅助电路的高压输出端vout 的电压超过阈值电压的状态。

18.在本技术实施例中,上述的辅助电路能够保证在正常电压电流范围内正常工作的同时,防止由于过流、过压等情况造成系统电源或者外置发生损坏的问题,从而可以保护供电过程中的电路的各个元器件。

19.在一种可能的实现方式中,在所述过流状态为短路状态的情况下,所述辅助电路的高压输出端vout 将所述第二开关管q2的栅极电压拉低为低压,所述第二开关管q2截止,所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述短路状态为所述辅助电路的高压输出端vout 和低压输出端vout-短接的状态;在反接状态下,所述第一防反模块和所述第二防反模块从自身的第二端到第一端截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述反接状态为外置电路的高压端与所述辅助电路的低压输出端vout-连接,且所述外置电路的低压端与所述辅助电路的高压输出端vout 连接的状态。

20.在本技术实施例中,上述的辅助电路能够保证在正常电压电流范围内正常工作的

同时,防止由于短路、反接等情况造成系统电源或者外置发生损坏的问题,从而可以保护供电过程中的电路的各个元器件。

21.在一种可能的实现方式中,所述第一防反模块为第一二极管d1,所述第一二极管d1从自身第一端到第二端单向导通。这样,二极管能够作为最简单的单向导通器件控制电路的导通方向,防止电流倒灌,对系统电源损坏,对供电电路起到保护作用。

22.在一种可能的实现方式中,所述第二防反模块为第二二极管d2的情况下,所述第二二极管d2从自身的第一端到第二端单向导通;或,所述第二防反模块为第三开关管q3的情况下,所述第三开关管q3的栅极分别连接所述第三电阻r3的第二端、所述第二开关管q2的漏极和所述第一开关管q1的栅极;所述第三开关管q3的漏极连接所述第一开关管q1的漏极;所述第三开关管q3的源极连接所述第一防反模块的第二端和所述高压输出端vout ,所述第三开关管q3为p型mos管或p型晶体管,所述第三开关管q3的漏极为所述第二防反模块的第一端,所述第三开关管q3的源极为所述第二防反模块的第二端。这样,辅助电路能够将通过二极管或者p型开关管来确定其电流的导通方向,放置电流的倒灌,保护供电电路。

23.在一种可能的实现方式中,所述辅助电路包括所述控制端,所述控制端分别连接所述第二电阻r2的第二端、所述第四电阻r4的第一端、所述第二开关管q2的栅极和所述第一防反模块的第一端;在所述控制端的控制信号为高电平的情况下,所述第二开关管q2和所述第一开关管q1导通,所述辅助电路的高压输入端vin 到高压输出端vout 的通路导通;在所述控制端的控制信号为低电平的情况下,所述第二开关管q2和所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开。这样,控制端在能够在正常工作状态下,控制是否进行供电,提高了供电电路的可控性,也能避免在不需要供电的情况下依然供电的情况,避免能耗的浪费。

24.在一种可能的实现方式中,所述辅助电路输入端的高压输入端vin 和低压输入端vin-连接系统电源,所述系统电源用于向外置电路供电。这样,辅助电路的输入端能够连接系统电源,系统电源能够向外界供电,保证电路连接的完整性。

25.在一种可能的实现方式中,所述辅助电路输出端的高压输出端vout 和低压输出端vout-连接外置电路,所述外置电路用于消费电量。这样,辅助电路的输出端能够外置电路,系统电源能够向这个外置电路进行供电,保证供电电路连接的完整性。

26.第三方面,本技术提供了一种供电控制方法,所述方法应用于辅助电路,所述辅助电路包括第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第一开关管q1、第二开关管q2、第一防反模块和第二防反模块;所述第一电阻r1的第一端连接所述辅助电路的高压输入端vin ,所述第一电阻r1的第二端分别连接所述第二电阻r2的第一端、所述第三电阻r3的第一端和所述第一开关管q1的源极;所述第二电阻r2的第二端分别连接所述第四电阻r4的第一端、所述第二开关管q2的栅极和所述第一防反模块的第一端;所述第四电阻r4的第二端分别连接所述辅助电路的低压输入端vin-、所述第二开关管q2的源极和所述辅助电路的低压输出端vout-;所述第三电阻r3的第二端连接所述第一开关管q1的栅极和所述第二开关管q2的漏极;所述第一开关管q1的漏极连接所述第二防反模块的第一端;所述第一防反模块的第二端和所述第二防反模块的第二端连接所述辅助电路的高压输出端vout ;其中,所述第一开关管q1为p型mos管或p型晶体管,所述第二开关管q2为n型mos管或n型晶体管,所述第一防反模块为从自身第一端到第二端单向导通的模块,所述第二防反模块为从

自身第一端到第二端单向导通的模块,所述方法包括:在正常工作状态下,所述第二开关管q2导通,所述第一开关管q1导通,所述辅助电路的高压输入端vin 到高压输出端vout 的通路导通;在过流状态下,所述辅助电路的高压输出端vout 将所述第二开关管q2的栅极电压拉低,所述第二开关管q2截止,所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述过流状态为所述辅助电路的电流超过阈值电流的状态;在过压状态下,所述第一防反模块和所述第二防反模块从自身的第二端到第一端截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述过压状态为所述辅助电路的高压输出端vout 的电压超过阈值电压的状态。

27.在本技术实施例中,摒弃了电路保护的专用芯片,使用简洁的电路逻辑实现过压、过流、短路和反接的保护,保证辅助电路的保护效果。此外,芯片的成本要远高于本技术实施例中辅助电路中的器件成本,因此,上述电路降低了产品实现的成本,增加电路方案布局的灵活性。

28.在一种可能的实现方式中,在所述过流状态为短路状态的情况下,所述辅助电路的高压输出端vout 将所述第二开关管q2的栅极电压拉低为低压,所述第二开关管q2截止,所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述短路状态为所述辅助电路的高压输出端vout 和低压输出端vout-短接的状态;在反接状态下,所述第一防反模块和所述第二防反模块从自身的第二端到第一端截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开,所述反接状态为外置电路的高压端与所述辅助电路的低压输出端vout-连接,且所述外置电路的低压端与所述辅助电路的高压输出端vout 连接的状态。

29.在本技术实施例中,上述的辅助电路能够保证在正常电压电流范围内正常工作的同时,防止由于短路、反接等情况造成系统电源或者外置发生损坏的问题,从而可以保护供电过程中的电路的各个元器件。

30.在一种可能的实现方式中,所述第一防反模块为第一二极管d1,所述第一二极管d1从自身第一端到第二端单向导通。这样,二极管能够作为最简单的单向导通器件控制电路的导通方向,防止电流倒灌,对系统电源损坏,对供电电路起到保护作用。

31.在一种可能的实现方式中,所述第二防反模块为第二二极管d2的情况下,所述第二二极管d2从自身的第一端到第二端单向导通;或,所述第二防反模块为第三开关管q3的情况下,所述第三开关管q3的栅极分别连接所述第三电阻r3的第二端、所述第二开关管q2的漏极和所述第一开关管q1的栅极;所述第三开关管q3的源极连接所述第一开关管q1的漏极;所述第三开关管q3的漏极连接所述第一防反模块的第二端和所述高压输出端vout ,所述第三开关管q3为p型mos管或p型晶体管,所述第三开关管q3的源极为所述第二防反模块的第一端,所述第三开关管q3的漏极为所述第二防反模块的第二端。这样,辅助电路能够将通过二极管或者p型开关管来确定其电流的导通方向,放置电流的倒灌,保护供电电路。

32.在一种可能的实现方式中,所述辅助电路包括所述控制端,所述控制端分别连接所述第二电阻r2的第二端、所述第四电阻r4的第一端、所述第二开关管q2的栅极和所述第一防反模块的第一端;在所述控制端的控制信号为高电平的情况下,所述第二开关管q2和

所述第一开关管q1导通,所述辅助电路的高压输入端vin 到高压输出端vout 的通路导通;在所述控制端的控制信号为低电平的情况下,所述第二开关管q2和所述第一开关管q1截止,所述辅助电路的高压输入端vin 到高压输出端vout 的通路断开。这样,控制端在能够在正常工作状态下,控制是否进行供电,提高了供电电路的可控性,也能避免在不需要供电的情况下依然供电的情况,避免能耗的浪费。

33.在一种可能的实现方式中,所述辅助电路输入端的高压输入端vin 和低压输入端vin-连接系统电源,所述系统电源用于向外置电路供电。这样,辅助电路的输入端能够连接系统电源,系统电源能够向外界供电,保证电路连接的完整性。

34.在一种可能的实现方式中,所述辅助电路输出端的高压输出端vout 和低压输出端vout-连接外置电路,所述外置电路用于消费电量。这样,辅助电路的输出端能够外置电路,系统电源能够向这个外置电路进行供电,保证供电电路连接的完整性。

附图说明

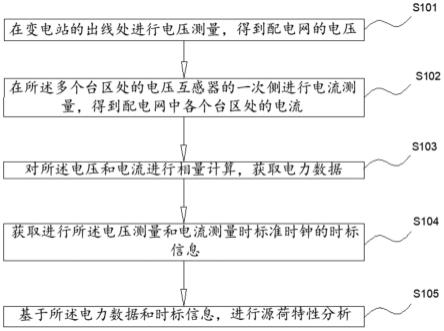

35.图1是本技术实施例提供的一种供电辅助电路的电路结构示意图;图2是本技术实施例提供的另一种供电辅助电路的电路结构示意图;图3是本技术实施例提供的又一种供电辅助电路的电路结构示意图;图4是本技术实施例提供的又一种供电辅助电路的电路结构示意图;图5是本技术实施例提供一种辅助电路应用场景的结构示意图。

具体实施方式

36.在本技术的实施例中,采用了“第一”、“第二”等字样对功能和作用基本相同的相同项或相似项进行区分。例如,第一芯片和第二芯片仅仅是为了区分不同的芯片,并不对其先后顺序进行限定。本领域技术人员可以理解“第一”、“第二”等字样并不对数量和执行次序进行限定,并且“第一”、“第二”等字样也并不限定一定不同。

37.需要说明的是,本技术实施例中,“示例性的”或者“例如”等词用于表示例子、例证或说明。本技术中被描述为“示例性的”或者“例如”的任何实施例或设计方案不应被解释为比其它实施例或设计方案更优选或更具优势。确切而言,使用“示例性的”或者“例如”等词旨在以具体方式呈现相关概念。

38.本技术实施例中,“至少一个”是指一个或者多个,“多个”是指两个或两个以上。“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b的情况,其中a,b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。“以下至少一项(个)”或其类似表达,是指的这些项中的任意组合,包括单项(个)或复数项(个)的任意组合。例如,a,b,或c中的至少一项(个),可以表示:a,b,c,a-b,a

‑‑

c,b-c,或a-b-c,其中a,b,c可以是单个,也可以是多个。

39.为了便于清楚描述本技术实施例的技术方案,以下,对本技术实施例中所涉及的部分术语和技术进行简单介绍:(1)弹簧针(pogo pin)pogo pin是一种应用于手机、携带式电子设备、通讯、汽车、医疗、航空航天等电子产品中的精密连接器,广泛应用于半导体设备中,起连接作用。例如,pogo pin应用于手机

的电池、屏幕、摄像头等部件。pogo pin是一种由针轴、弹簧、针管三个基本部件通过精密仪器铆压预压之后形成的弹簧式探针,其内部有一个精密的弹簧结构。pogo pin的表面镀层一般都镀金,可以更好的提高它的防腐蚀功能、机械性能、电气性能、稳定性、耐久性等。

40.(2)过压保护和过流保护过压保护(overvoltage protection,ovp)是指被保护线路电压超过预定的最大值时,使电源断开或使受控设备电压降低的一种保护方式。

41.过流保护(over current protection,ocp)是当电流超过预定最大值时,使保护装置动作的一种保护方式。当流过被保护原件中的电流超过预先设定的某一个数值,过流保护能够避免损坏器件。

42.此外,短路保护是指对供电系统中不等电位的导体在电气上短接产生的短路故障进行的保护。

43.对于在供电电路中,为了能够对pogo pin对外输出电源形成过压保护或者过流保护,通常使用专用的过压/过流保护的器件。

44.示例性的,在供电电路中使用过压/过流保护的相关专用芯片,来实现过高的电压或电流的保护,形成过压保护或者过流保护。其中,专用芯片设有过电压、过电流保护的外置开关,用于适配用户所需的工作电压和电流。

45.上述的实施方式中,专有芯片的成本高,电路的灵活性也比较差,线路的复杂性也高。

46.请参阅图1,图1是本发明实施例提供的一种供电辅助电路的电路结构示意图。如图1所示,该电路结构可以包括第一电阻r1、第二电阻r2、第三电阻r3和第四电阻r4,第一开关管q1和第二开关管q2、第一防反模块和第二防反模块。此时,第一防反模块为第一二极管d1,第二防反模块为第二二极管d2。第一防反模块为从自身第一端到第二端单向导通的模块,第二防反模块为从自身第一端到第二端单向导通的模块。

47.第一电阻r1的第一端连接作为辅助电路的高压输入端vin 。第一电阻r1的第二端分别连接第二电阻r2的第一端,第三电阻r3的第一端和第一开关管q1的源极s。第二电阻r2的第二端分别连接第四电阻r4的第一端、第二开关管q2的栅极g和第一二极管d1的第一端。第四电阻r4的第二端分别连接低压输入端vin-、第二开关管q2的源极和低压输出端vout-。第三电阻r3的第二端连接第一开关管q1的栅极和第二开关管q2的漏极d。第一开关管q1的漏极连接第二二极管d2的第一端。第一二极管d1和第二二极管d2的作为(连接)辅助电路的高压输出端vout 。

48.上述辅助电路的输入端包括高压输入端vin 和低压输入端vin-。输入端可以连接供电装置(系统电源)(例如,vin 连接电池的高压端,vin-连接电池的低压端)。辅助电路的输出端包括高压输出端vout 和低压输出端vout-。输出端可以连接外置电路(即消费电路)(例如,vout 连接外置高压端,vout-连接外置低压端)。低压输入端vin-和低压输出端vout-均可以接线gnd,也可以不接地,连接对应的低压端即可,本技术不限定。

49.其中,第一开关管q1可以为p mos管或者p型晶体管,第二开关管q2可以为n mos管或者n型晶体管。

50.上述的电路中,由于r2和r3的第一端均与r1的第二端连接,r2第一端的电压值与r3第一端的电压值相同。假设第二电阻r2的阻值小于第三电阻r3的阻值,电阻不同导致r2

的分压小于r3的分压,导致r2第二端的电压值会大于r3第二端的电压值。对于q2来说,r2的第二端连接q2的栅极,r3的第二端连接q2的漏极。r4的第一端连接q2的栅极,r4的第二端连接q2的源极,由于r4也具有分压作用,r4的第一端电压值大于第二端的电压值,即q2栅极电压值vg_q2大于源极电压值vs_q2。在vg_q2-vs_q2的结果大于或等于第一阈值电压vgs_th1的情况下,q2可以从漏极到源极导通。反之,在vg_q2-vs_q2的结果小于第一阈值电压vgs_th1的情况下,q2截止,从漏极到源极不能导通。

51.在q2导通的状态下,r3第一端的电压值大于第二端的电压值,r3的第一端连接q1的源极,r3的第二端连接q1的栅极,因此,q1源极的电压值vs_q1大于栅极的电压值vg_q1。在vs_q1-vg_q1大于或等于第二阈值电压vgs_th2的情况下,q1导通,即q1从源极到栅极导通;在vs_q1-vg_q1小于第二阈值电压vgs_th2的情况下,q1截止,即q1从源极到栅极不能导通。

52.在q2截止的状态下,q1源极的电压值vs_q1和栅极的电压值vg_q1均为零,因此q1也截止。

53.两个二极管d1和d2的正向导通的方向均是从高压输入端vin 到高压输出端vout 的方向,反向电流则会截止。

54.此外d1和d2由于导通方向不一致,能够保证不会出现电流倒灌的情况,从而使得电流的流向只能是从系统电源到外置电路,而不是其它的电流流向,保证电路的可靠性和稳定性。

55.不同的电压或者电流、或者电路的连接方式不同时,电路处于不同的工作状态:1.正常工作状态:在vout 和vout-接入外置电路的情况下,上述辅助电路中的q1和q2属于导通状态,此时,高压输入端vin 经过第一电阻r1和第二二极管d2向高压输出端vout 连接,而低压输入端vin-与低压输出端vout-连接,即辅助电路的高压输入端vin 到高压输出端vout 的通路导通,形成闭合的电路,从而可以为接入到vout-和vin-两端的外置电路进行供电。

56.2.过压状态:在高压输出端vout 的接入的电压大于高压输入端vin 的情况下,电路处于过压状态。此时,由于d1和d2两二极管单向导通,因此,电路无法反相导通,即辅助电路的高压输入端vin 到高压输出端vout 的通路断开,避免电流倒灌的问题。从而可以防止反向电流流入电源系统,保护系统电源。其中,过压状态为辅助电路的高压输出端vout 的电压超过阈值电压的状态。

57.3.过流状态:在过流的状态下,vout 和vout-两端经过负载的电流过高,会导致系统工作异常。上述辅助电路中,在过流的状态下,流经第一电阻r1的电流会增大,第一电阻r1两端的分压变大,第二电阻r2第一端的电压变小,第二电阻r2的第二端的电压也会变小,第二开关管q2栅极的电压值被拉低,导致vg_q2-vs_q2的值不再大于或等于第一阈值电压,导致q2变为截止状态。即q1也截止,辅助电路的高压输入端vin 到高压输出端vout 的通路断开,停止供电。从而可以防止电流过高损坏外置电路等器件。其中,过流状态为辅助电路的电流超过阈值电流的状态,干流电路上的电流超过阈值电流,即可以理解为流经r1的电流过大。

58.其中,第一电阻r1可以是正温度系数的热敏电阻(positive temperature coefficient thermistor,ptc thermistor),当电流增大的情况下,电阻的温度变高,对应

的阻值变大,使得第一电阻r1两端的分压更大,第一电阻r1的第二端的电压变小,第二电阻r2的第二端的电压变小的幅度更大,因此,第二开关管q2截止,第一开关管q1也截止,从而辅助电路的高压输入端vin 到高压输出端vout 的通路断开,达到过流保护的目的。

59.4.短路状态:在vout 和vout-两端的外置电路处于短路状态时,相当于vout 和vout-两端通过导线直接连接,此时,若d1导通,会使得第二开关管的源极的电压与栅极的电压相等。例如,若d1的第二端接地,可以直接拉低q2栅极的电压为0。使得q2处于截止状态,即q1也截止,辅助电路的高压输入端vin 到高压输出端vout 的通路断开,停止供电。从而可以防止电流过高损坏系统电源和外置电路等器件。短接状态可以为一种特殊的过流状态,短路状态为辅助电路的高压输出端vout 和低压输出端vout-短接的状态。

60.5.反接状态:由于辅助电路包括d1和d2,因此电流单向导通,外置电路中一般也会设有防反模块,保证电路单向导通。当辅助电路与外置电路的导通方向一致的情况下,且为导通方向的情况下,才能够开始供电。反接的情况下,d1和d2截止,辅助电路的高压输入端vin 到高压输出端vout 的通路断开。当然,即便外置电路中,没有防反模块,也可以保证d1和d2两二极管只能单向导通,从而可以防止反相电流损坏元器件。其中,反接状态为外置电路的高压端与辅助电路的低压输出端vout-连接,且外置电路的低压端与辅助电路的高压输出端vout 连接的状态。

61.通过上述的5个状态下辅助电路的工作情况可以看出,电路能够保证在正常电压电流范围内正常工作的同时,防止由于过流、过压、反接或短路等情况造成系统电源或者外置电路发生损坏的问题,从而可以保护供电过程中的电路的各个元器件。

62.示例性地,vin 为5.2v,r1的电阻为1欧姆,经过r1的正常工作电流的大小为200ma,经过r1之后,r1第二端的电压为5v(经过r1降压0.2v)。vout-和vin-两端接地,电压值为0。第二开关管q2的第一阈值电压vgs_th1为2.8v。假设第二电阻r2和第四电阻r4的阻值为1:2,使得通常情况下,r2第二端的电压为10/3v。即在正常工作状态下,第二开关管q2的栅极电压为3.3v的情况下,q2导通,q1导通,系统电源对外供电。在过流状态下,q2的栅极电压变小为2.67v,q2截止,q1截止,系统电源对外不供电。

63.示例性地,正常的工作电流也可以是1a,此时,在r1为1ω的情况下,此时r1降压1v。

64.需要说明的是,本技术实施例提供的开关管可以为绝缘栅双极型晶体管(insulated gate bipolar transistor,igbt)、金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet管)、三极管等,也可以其它可控器件,本技术不作限制。

65.本技术实施例中的辅助电路可以用于向外提供电源的供电电路中。一种场景中,电子设备的pogo pin接口向外供电。例如,平板电脑的pogo pin输出端外接键盘(其中平板的电脑的电池为系统电源,键盘为外置装置)。又例如,蓝牙耳机的充电盒与耳机之间充电的充电电路,其中,充电盒的pogo pin接口可以作为辅助电路的vout 和vout-两端。另一种场景中,电子设备的主电路板可以向其它电路板提供电源,其中主电路板包括系统电源,其它电路板为外置装置。需要说明的是,上述仅仅是本技术辅助电路其中的两个应用场景,还能够使用到其它的供电(充电)的场景中,本技术不限定。

66.结合图1,图2是本发明实施例提供的另一种供电辅助电路的电路结构示意图。如

图2所示,该电路结构除了包括图1中的所有元器件之外,辅助电路还可以包括控制端,控制端可以连接第二电阻r2的第二端、第四电阻r4的第一端、第二开关管q2的栅极和第一二极管d1的第一端。其余元器件以及连接方式可以参考图1中的相关描述,不赘述。此时,第一防反模块为第一二极管d1,第二防反模块为第二二极管d2。

67.在图2的辅助电路中,输入端还包括控制端。控制端可以提供控制信号,控制信号能够控制供电电路的导通和断开,从而可以控制对外置电路关断供电。如图2所示,在控制信号为高电平信号的情况下,q2的栅极电压值变高,使得vg_q2-vs_q2的结果大于第一阈值电压vgs_th1,q2导通,q1导通,使得系统电源向外置电路供电。反之,在控制信号为低电平信号的情况下,q2的栅极电压值变低,使得vg_q2-vs_q2的结果不大于第一阈值电压vgs_th1,q2截止,q1截止,使得系统电源向外置电路不供电。其中,电子设备可以通过控制模块连接控制端,例如,控制模块为cpu,从而能够控制电路是否进行供电。

68.上述的实施方式中,由于控制端能够控制是否向外置电路供电,从而电子设备能够控制是否供电。在不存在控制端的情况下,只要有设备接入且辅助电路vin 和vin-两端的电压满足于辅助电路导通的情况下,均要向其供电。然而,通过上述的控制信号,能够保证即便接入的情况下,在控制模块判断不需要供电,便提供低电平可以停止供电,需要供电便提供高电平进行供电,能够增加供电的可控性,保证供电的有效性,也避免能耗的浪费。

69.此外,第二开关管q2的栅极可以留有控制端,在控制端缺少的情况下,可以省去,能够保证电路的灵活性。

70.结合图1,图3是本技术实施例公开的又一种供电辅助电路的电路结构示意图。如图3所示,辅助电路中不包括第二二极管d2,第二二极管d替换为第三开关管q3。此时,第一防反模块为第一二极管d1,第二防反模块为第三开关管q3。其中,第三开关管q3可以为p型晶体管或者pmos管。第三开关管q3的漏极为第二防反模块的第一端,第三开关管q3的源极为第二防反模块的第二端。

71.其中,第三开关管q3的栅极连接第三电阻r3的第二端、第二开关管q2的漏极和第一开关管q1的栅极。第三开关管q3的漏极连接第一开关管q1的漏极。第三开关管q3的源极连接第一二极管d1的第二端和高压输出端vout 。

72.上述的图3的辅助电路中,当q2处于导通的情况下,q1导通,使得q3的栅极电压vg_q3大于源极vs_q3。在vgs=vg_q3-vs_q3的值小于或等于第三阈值电压vgs_th3的情况下,q3(从体二极管)导通,从而开启供电电路进行供电。在vg_q3-vs_q3的值大于第三阈值电压vgs_th3的情况下,q3截止,电路断开,不供电。

73.由于q3为p mos管或者p型晶体管(q1和q3是背靠背的连接方式),且p型开关管vgs为负压导通,即栅极电压为零时,源极电压为正。若果反接的情况下,q3的栅极为正,源极为负,q3是截止的,即辅助电路中电源输出端没有输出。因此,能够防止第一二极管d1和第三开关管q3方向不一致时,出现互相倒灌的情况,这样能够通过保证供电电路的稳定性和可靠性。

74.结合图1、图2和图3,图4是本技术实施例公开的又一种供电辅助电路的结构示意图。如图4所示,该电路结构可以包括第一电阻r1、第二电阻r2、第三电阻r3和第四电阻r4,第一开关管q1、第二开关管q2、第三开关管q3和第一二极管d1。此时,第一防反模块为第一二极管d1,第二防反模块为第三开关管q3。

75.其中,第一电阻r1、第二电阻r2、第三电阻r3和第四电阻r4,第一开关管q1、第二开关管q2和第一二极管d1的连接方式可以参考图1的相关描述,第三开关管q3的连接方式可以参考图3的相关描述,控制端的连接方式和作用可以参考图2的相关描述。

76.辅助电路中的输入端可以包括高压输入端vin ,控制端和低压输入端vin-。辅助电路中的输出端可以包括高压输出端vout ,控制端和低压输出端vout-。控制端可以参考上述图2的相关描述,其它端口可参考图1的相关描述,不赘述。

77.上述的4中实施方式的电路中,摒弃了电路保护的专用芯片,使用简洁的电路逻辑实现过压、过流、短路和反接的保护,保证辅助电路的保护效果。此外,芯片的成本要远高于本技术实施例中辅助电路中的器件成本,因此,上述电路降低了产品实现的成本,增加电路方案布局的灵活性。

78.上述图1~图4的电路结构中,若开关管q1、q2和q3为mos管的条件下,mos管可以包括体二极管。mos管包括体二极管的情况下,体二极管的导通方向与mos管的导通方向相反。

79.上述图1到图4的实施方式中,第一防反模块可以为第一二极管d1,也可以是其它元器件组成的防反模块,第二防反模块为第三开关管q3,也可以是其它元器件组成的防反模块,本技术不限定。

80.上述图1~图4中,标号1表示器件的第一端,标号2表示器件的第二端。s表示开关管的源极,g表示开关管的栅极,d表示开关管的漏极。

81.上述图1~图4的电路搭建过程中,可以基于开关管q1和q2的具体参数,调整电阻r1、r2和r3,调整的结果是灵活的,当然,其他的电阻和器件调整参数也是灵活的,本技术不作限定。

82.图5是本技术实施例公开的一种辅助电路应用场景的结构示意图。如图5所示,在的pogo pin的使用场景中,在上述辅助电路的输出端连接pogo pin连接器。其中,辅助电路的高压输出端vout 连接pogo pin高压输出端,辅助电路的低压输出端vout-连接pogo pin低压输出端。pogo pin连接器作为一个连接装置,可以与外置电路耦接,即pogo pin高压输出端连接外置电路的高压端,pogo pin低压输出端连接外置电路的低压端。辅助电路的输入端可以连接系统电源,其中,高压输入端vin 连接系统电源的高压端,低压输入端vin-连接系统电源的低压端。可选地,在辅助电路包括控制端的条件下,控制端可以连接控制模块(未示出)。此时,上述的供电电路便能形成完成的回路,在工作在正常状态下,系统电源能够为外置电路供电。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。