1.本公开涉及存储技术领域,尤其涉及一种浮栅存储器及其制备方法。

背景技术:

2.随着现代信息社会对海量数据的存储和分析需求的不断增长,促使了下一代处理器和存储系统的发展。由于传统冯

·

诺依曼架构计算系统面临计算速度慢、制造成本高、处理器与存储器之间数据传输的高功耗等问题,为应对物联网(internet of things,iot)、人工智能(artificial intelligence,ai)、云计算(cloud computing)等各种大数据问题,迫使人们需要创建新的系统架构来应对这些挑战。

3.在存算一体架构中,处理器和内存合并在一起,利用其并行计算能力,打破了处理器-存储器数据传输限制,解决了传输速度慢和高功耗的问题。在这样的系统中,每个存储单元都充当动态记录和处理信息的多级存储单元。与二进制单元相比,这种多级存储单元需要具有多种存储状态以提供更高的数据存储密度和处理精度。因此,寻找新的材料体系结构作为这种多级存储单元迫在眉睫。

技术实现要素:

4.基于此,本公开一方面提供了一种浮栅存储器,包括:栅层,栅层上依次叠设有绝缘层、浮栅层、阻挡层及沟道层;沟道层包括n型沟道层和p型沟道层,n型沟道层和p型沟道层构成p-n结;其中,通过向栅层施加偏压,以控制沟道层和浮栅层共同实现存储电子和释放电子。

5.根据本公开的实施例,n型沟道层和p型沟道层的位置关系包括以下其中之一:n型沟道层形成于阻挡层上的第一区域,p型沟道层形成于阻挡层上的第二区域且与n型沟道层远离阻挡层的表面接触;或者p型沟道层形成于阻挡层上的第一区域,n型沟道层形成于阻挡层上的第二区域且与p型沟道层远离阻挡层的表面接触;或者n型沟道层形成于阻挡层上的第一区域,p型沟道层形成于阻挡层上的第二区域,n型沟道层与p型沟道层在横向方向上平行邻接接触设置;其中,第一区域和第二区域为不同区域。

6.根据本公开的实施例,n型沟道层和p型沟道层的位置关系包括以下其中之一:n型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,p型沟道层形成于阻挡层上的第二区域且与两侧的n型沟道层远离阻挡层的表面接触,以形成npn垂直型双极结型晶体管(bipolar junction transistor,bjt)型沟道;或者p型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,n型沟道层形成于阻挡层上的第二区域且与两侧的p型沟道层远离阻挡层的表面接触,以形成pnp垂直型bjt型沟道;或者n型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,p型沟道层形成于阻挡层上的第二区域且与两侧的n型沟道层在横向方向上平行邻接接触,以形成npn水平型bjt型沟道;或者p型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,n型沟道层形成于阻挡层上的第二区域且与两侧的p型沟道层在横向方向上平行邻接接触,以形成pnp水平型bjt型沟道,其中,第一区域和第二区域

为不同区域。

7.根据本公开的实施例,n型沟道层和p型沟道层的位置关系包括以下其中之一:n型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,p型沟道层形成于阻挡层上的第二区域且与两侧的n型沟道层远离阻挡层的表面接触,且该p型沟道层上覆盖一层阻挡层,以形成npn垂直型金属-氧化层半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)型沟道;或者p型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,n型沟道层形成于阻挡层上的第二区域且与两侧的p型沟道层远离阻挡层的表面接触,且该n型沟道层上覆盖一层阻挡层,以形成pnp垂直型mosfet型沟道;或者n型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,p型沟道层形成于阻挡层上的第二区域且与两侧的n型沟道层在横向方向上平行邻接接触,且该p型沟道层上覆盖一层阻挡层,以形成npn水平型mosfet型沟道;或者p型沟道层形成于阻挡层上左右两侧具有一定间隔的第一区域,n型沟道层形成于阻挡层上的第二区域且与两侧的p型沟道层在横向方向上平行邻接接触,且该n型沟道层上覆盖一层阻挡层,以形成pnp水平型mosfet型沟道。

8.根据本公开的实施例,浮栅层包括允许存储电子和释放电子的允许状态,以及禁止存储电子和释放电子的禁止状态;在向栅层施加储存偏压的情况下,沟道层的电子隧穿进入处于允许状态的浮栅层,实现处于允许状态的浮栅层存储电子;在向栅层施加释放偏压的情况下,处于允许状态的浮栅层存储的电子隧穿回到沟道层,实现处于允许状态的浮栅层释放电子。

9.根据本公开的实施例,在向栅层施加正偏压的情况下,实现浮栅存储器的写入操作;在向栅层施加负偏压的情况下,实现浮栅存储器的擦除操作。

10.根据本公开的实施例,在浮栅层接地的情况下,浮栅层处于禁止状态。

11.根据本公开的实施例,绝缘层的材料为sio2、sin

x

、al2o3、hfo2、aln的其中之一,绝缘层的厚度为300nm~1μm。

12.根据本公开的实施例,浮栅层的材料均为单层二维材料或多层二维材料,阻挡层的材料均为纳米级的二维材料,n型沟道层的材料为n型二维半导体材料,p型沟道层的材料为p型二维半导体材料。

13.根据本公开的实施例,浮栅层的材料为黑磷或多层石墨烯,浮栅层的厚度为0.2~10nm;阻挡层的材料为六方晶格氮化硼、hfo2、zro2、al2o3的其中之一,阻挡层的厚度为5~20nm;n型沟道层的材料为mos2、mote2、ws2的其中之一,p型沟道层的材料为wse2、gase、geas、α-mns的其中之一,n型沟道层和p型沟道层的厚度为0.2~10nm。

14.根据本公开的实施例,栅层的开启电压与阻挡层的厚度正相关,其中,开启电压为沟道层的开关比大于103时对栅层施加的最小电压。

15.本公开第二方面还提供一种浮栅存储器的制备方法,用于制备上述所述浮栅存储器,包括:提供一栅层;在栅层上依次制备绝缘层、浮栅层、阻挡层及沟道层;沟道层包括n型沟道层和p型沟道层,n型沟道层和p型沟道层构成p-n结;其中,通过向栅层施加偏压,以控制沟道层和浮栅层共同实现存储电子和释放电子。

16.根据本公开实施例提供的浮栅存储器,通过将n型二维半导体材料构成的n型沟道层和p型二维半导体材料构成的p型沟道层形成于阻挡层的上,使得n型沟道层和p型沟道层形成的p-n结对特定方向的电场敏感,在电场的调控下能形成较大开关比,能够形成多个可

区分的电导态,满足多级存储的特性,进而通过施加不同个数的脉冲序列,能够选择性地对沟道层总的电阻进行改写,结合浮栅层允许存储电子和释放电子的允许状态和禁止存储电子和释放电子的禁止状态,实现浮栅存储器的多级存储功能。

17.进一步地,p-n沟道层的结构设置为多种实现方式,更好地实现浮栅存储器的多级存储功能。

18.进一步地,通过栅层结合具备允许状态和禁止状态的浮栅层,实现浮栅存储器的快速及低功耗擦写操作。

附图说明

19.通过以下参照附图对本公开实施例的描述,本公开的上述以及其他目的、特征和优点将更为清楚,在附图中:

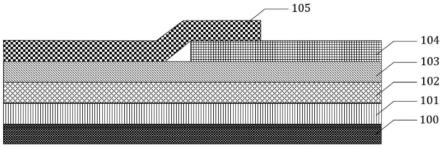

20.图1示意性示出了本公开实施例提供的浮栅存储器的结构图。

21.图2示意性示出了本公开实施例提供的bjt型沟道层浮栅存储器的结构图。

22.图3示意性示出了本公开实施例提供的mosfet型沟道层浮栅存储器的结构图。

23.图4示意性示出了本公开实施例提供的浮栅存储器制备方法的流程图。

24.图5a示意性示出了本公开实施例提供的浮栅存储器制备方法中在栅层上形成有绝缘层的结构图。

25.图5b示意性示出了本公开实施例提供的浮栅存储器制备方法中在绝缘层上形成浮栅层的结构图。

26.图5c示意性示出了本公开实施例提供的浮栅存储器制备方法中在浮栅层上形成有阻挡层的结构图。

27.图5d示意性示出了本公开实施例提供的浮栅存储器制备方法中在阻挡层上形成有n型沟道层的结构图。

28.图5e示意性示出了本公开实施例提供的浮栅存储器制备方法中在阻挡层上形成有p型沟道层的结构图。

29.【附图标记】

30.100-栅层;101-绝缘层;102-浮栅层;103-阻挡层;104-n型沟道层;105-p型沟道层。

具体实施方式

31.为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。显然,所描述的实施例是本公开一部分实施例,而不是全部的实施例。基于本公开中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

32.在此使用的术语仅仅是为了描述具体实施例,而并非意在限制本公开。在此使用的术语“包括”、“包含”等表明了所述特征、步骤、操作和/或部件的存在,但是并不排除存在或添加一个或多个其他特征、步骤、操作或部件。

33.在本公开中,除非另有明确的规定和限定,术语“安装”、“相连”“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连

接,也可以是电连接或可以互相通讯;可以是直接连接,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本公开中的具体含义。

34.在本公开的描述中,需要理解的是,术语“纵向”、“长度”、“周向”、“前”、“后”、“左”、“右”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本公开和简化描述,而不是指示或暗示所指的子系统或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本公开的限制。

35.贯穿附图,相同的元素由相同或相近的附图标记来表示。可能导致本公开的理解造成混淆时,将省略常规结构或构造。并且图中各部件的形状、尺寸、位置关系不反映真实大小、比例和实际位置关系。另外,在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限制。

36.类似地,为了精简本公开并帮助理解各个公开方面中的一个或多个,在上面对本公开示例性实施例的描述中,本公开的各个特征有时被一起分到单个实施例、图或者对其描述中。参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本公开的至少一个实施例或示例中。本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或者多个实施例或示例中以合适的方式结合。

37.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。因此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本公开的描述中,“多个”的含义是至少两个,例如两个、三个等,除非另有明确具体的限定。

38.本公开实施例提供一种基于二维材料p-n二极管的浮栅存储器,以实现浮栅存储器的快速及低功耗擦写和浮栅存储器的多级存储。下面结合具体实施例进行详细介绍。

39.图1示意性示出了本公开实施例提供的浮栅存储器的结构图。

40.如图1所示,该浮栅存储器例如可以包括:

41.栅层100,栅层100同时可以起到衬底的作用。

42.绝缘层101,覆盖在栅层100上。

43.浮栅层102,形成在绝缘层101上。

44.阻挡层103,形成在浮栅层102上。

45.沟道层,形成于阻挡层103上,包括n型沟道层104和p型沟道层105。n型沟道层104和p型沟道层105形成p-n结。

46.根据本公开的实施例,通过向栅层施加偏压,以控制沟道层和浮栅层共同实现存储电子和释放电子。

47.在本公开实施例中n型沟道层104和p型沟道层105的位置关系为:

48.n型沟道层104形成于阻挡层103上的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与n型沟道层104远离阻挡层103的表面接触。

49.或者,p型沟道层105形成于阻挡层103上的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与p型沟道层105远离阻挡层103的表面接触。

50.或者,n型沟道层形成于阻挡层上的第一区域,p型沟道层形成于阻挡层上的第二区域,n型沟道层与p型沟道层在横向方向上平行邻接接触设置。

51.或者,p型沟道层形成于阻挡层上的第一区域,n型沟道层形成于阻挡层上的第二区域,n型沟道层与p型沟道层在横向方向上平行邻接接触设置。

52.应当理解,图1仅仅示出了n型沟道层104,形成于阻挡层103上的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与n型沟道层104远离阻挡层103的表面接触的情况,p型沟道层105形成于阻挡层103上的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与p型沟道层105远离阻挡层103的表面接触以及n型沟道层与p型沟道层在横向方向上平行邻接接触设置的情况未示出,图1所示的位置关系不用于限制本公开的保护范围。

53.其中,第一区域和第二区域为不同区域。n型沟道层104的材料为n型二维半导体材料,p型沟道层105的材料为p型二维半导体材料。p型沟道层105与n型沟道层104远离阻挡层103的表面接触可以理解为p型沟道层105为三段式结构,第一段形成于阻挡层103上的第二区域,第三段形成于n型沟道层104上,第二段倾斜将第一端和第三段连接。n型沟道层与p型沟道层在横向方向上平行邻接接触设置可以理解为n型沟道层与p型沟道层为同一种二维材料,通过在左右两侧的第一区域和第二区域进行不同掺杂使第一区域和第二区域的同种二维材料呈现n型和p型。n型沟道层与p型沟道层在横向方向上平行邻接接触设置还可以理解为n型沟道层与p型沟道层为同一种二维材料,通过设置左右两侧的第一区域和第二区域二维材料的厚度使第一区域和第二区域的同种二维材料呈现n型和p型。

54.在本公开实施例中,n型沟道层104和p型沟道层105的位置关系还可以为:

55.n型沟道层104形成于阻挡层103上左右两侧具有一定间隔的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与两侧的n型沟道层104远离阻挡层103的表面接触,以形成npn垂直型bjt沟道。

56.或者,p型沟道层105形成于阻挡层103上左右两侧具有一定间隔的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与两侧的p型沟道层105远离阻挡层103的表面接触,以形成pnp垂直型bjt沟道。

57.或者,n型沟道层104形成于阻挡层103上左右两侧具有一定间隔的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与两侧的n型沟道层104在横向方向上平行邻接接触,以形成npn水平型bjt沟道。

58.或者,p型沟道层105形成于阻挡层103上左右两侧具有一定间隔的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与两侧的p型沟道层105在横向方向上平行邻接接触,以形成pnp水平型bjt沟道。

59.应当理解,图2仅仅示出了n型沟道层104形成于阻挡层103上左右两侧具有一定间隔的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与两侧的n型沟道层104远离阻挡层103的表面接触的情况,p型沟道层105形成于阻挡层103上左右两侧具有一定间隔的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与p型沟道层105远离阻挡层103的表面接触以及n型沟道层104与两侧的p型沟道层105在横向方向上平行接触设置的情况未示出,图2所示的位置关系不用于限制本公开的保护范围。

60.在本公开实施例中,n型沟道层104和p型沟道层105的位置关系还可以为:

61.n型沟道层104形成于阻挡层103上左右两侧具有一定间隔的第一区域,p型沟道层

105形成于阻挡层103上的第二区域且与两侧的n型沟道层104远离阻挡层103的表面接触,且该p型沟道层105上覆盖一层阻挡层103,以形成npn垂直型mosfet沟道。

62.或者,p型沟道层105形成于阻挡层103上左右两侧具有一定间隔的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与两侧的p型沟道层105远离阻挡层103的表面接触,且该n型沟道层104上覆盖一层阻挡层103,以形成pnp垂直型mosfet沟道。

63.或者,n型沟道层104形成于阻挡层103上左右两侧具有一定间隔的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与两侧的n型沟道层104在横向方向上平行邻接接触,且该p型沟道层105上覆盖一层阻挡层103,以形成npn水平型mosfet沟道。

64.或者,p型沟道层105形成于阻挡层103上左右两侧具有一定间隔的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与两侧的p型沟道层105在横向方向上平行邻接接触,且该n型沟道层104上覆盖一层阻挡层103,以形成pnp水平型mosfet沟道。

65.应当理解,图3仅仅示出了n型沟道层104形成于阻挡层103上左右两侧具有一定间隔的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与两侧的n型沟道层104远离阻挡层103的表面接触的情况,p型沟道层105形成于阻挡层103上左右两侧具有一定间隔的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与p型沟道层105远离阻挡层103的表面接触以及n型沟道层104与两侧的p型沟道层105在横向方向上平行接触设置的情况未示出,图3所示的位置关系不用于限制本公开的保护范围。

66.根据本公开的实施例,每个浮栅层102包括允许存储电子和释放电子的允许状态,以及禁止存储电子和释放电子的禁止状态。换言之,允许状态代表该浮栅层102允许存储和释放电子,禁止状态代表该浮栅层102禁止存储和释放电子。其中,在浮栅层102接地的情况下,浮栅层102处于禁止状态。

67.进一步地,在向栅层100施加储存偏压的情况下,沟道层104的电子隧穿进入处于允许状态的浮栅层102,实现处于允许状态的浮栅层102存储电子,处于禁止状态的浮栅层102不存储电子。在向栅层100施加释放偏压的情况下,处于允许状态的浮栅层102存储的电子隧穿回到沟道层104,实现处于允许状态的浮栅层102释放电子,处于禁止状态的浮栅层102不释放电子。释放偏压与储存偏压的极性相反。

68.根据本公开的实施例,在向栅层施加正偏压的情况下,实现浮栅存储器的写入操作,在向栅层施加负偏压的情况下,实现浮栅存储器的擦除操作。

69.示例性地,写入操作为通过在栅层100上施加正偏压,沟道层104的大量电子隧穿阻挡层103注入浮栅层102中,实现状态“1”的微秒级的高速写入,撤去偏压后,浮栅层102中存储的电子导致浮栅存储器器件的阈值漂移,输出高电流,实现状态“1”的存储;擦除操作为通过在栅层100上施加负偏压,大量电子隧穿阻挡层103回到沟道层104,实现状态“1”的擦除。

70.根据本公开的实施例,由于p型沟道层和n型沟道层所用材料分别为p型二维半导体材料和n型二维半导体材料,其形成的p-n结对特定方向(例如垂直方向)的电场敏感,在电场的调控下能形成较大开关比,能够形成多个可区分的电导态,满足多级存储的特性。即通过施加不同个数的脉冲序列,以改变浮栅层102存储的电子量,p-n结对浮栅层102存储的电子所引起的电场敏感,表现出不同的电导态。因此能够通过对栅层施加不同序列的脉冲从而选择性地对沟道层总电阻进行改写,使浮栅存储器可以实现多级存储。

71.由于新型的二维材料,如石墨烯、过渡金属硫化物和黑磷等,有着优良的电学和光学性能,既可以改善现有的存储技术,也可以使下一代低成本、灵活和可穿戴存储设备成为可能。因此,本公开实施例对各层结构的材料和尺寸进行了合理设计,具体如下。

72.在本公开一实施例中,栅层100的材料为导电材料。可选地,栅层100的材料可以为金属电极、重掺杂的硅、砷化镓、氮化镓、碳化硅、氧化镓的其中之一,例如,栅层100为p型掺杂的硅或n型掺杂的硅,但不限于此。

73.在本公开一实施例中,绝缘层101为绝缘介质,用于防止栅层100与浮栅层102接触,设置绝缘层101可以防止栅层100的电子隧穿进入浮栅层102,对浮栅存储器造成破坏。绝缘层101的材料可以为sio2、sin

x

、al2o3、hfo2、aln的其中之一,例如,绝缘层101为sio2,但不限于此。绝缘层的厚度可以为300nm~1μm,例如,绝缘层101的厚度可以为300nm、400nm、600nm、800nm、1μm,但不限于此。

74.在本公开一实施例中,浮栅层102的材料可以为二维材料,可以为单层二维材料,也可以由多层二维材料形成。可选地,浮栅层的材料可以为黑磷(bp)或多层石墨烯(mlg)。例如,浮栅层102为多层石墨烯(mlg),但不限于此。浮栅层的厚度可以为0.2~10nm,例如,浮栅层102的厚度可以为0.3nm、1nm、2nm、5nm、8nm、10nm,但不限于此。

75.在本公开一实施例中,阻挡层103的材料可以为二维材料,一般选择纳米级的二维材料。可选地,阻挡层103的材料可以为六方晶格氮化硼(h-bn)、hfo2、zro2、al2o3的其中之一,例如,阻挡层103可以为六方晶格氮化硼(h-bn),但不限于此。阻挡层的厚度可以为5~20nm,例如,阻挡层103的厚度可以为5nm、7nm、10nm、15nm、20nm,但不限于此。

76.在本公开一实施例中,n型沟道层的材料可以为mos2、mote2、ws2的其中之一,例如,n型沟道层104为mos2,但不限于此。p型沟道层的材料可以为wse2、gase、geas、α-mns的其中之一,例如,p型沟道层105为wse2,但不限于此。n型沟道层104的厚度为0.2~10nm,例如,n型沟道层104厚度可以为0.3nm、1nm、4nm、8nm,但不限于此。p型沟道层105的厚度为0.2~10nm,例如,p型沟道层105厚度可以为0.2nm、1nm、4nm、8nm,但不限于此。

77.根据本公开的实施例,浮栅存储器的浮栅层102、阻挡层103、n型沟道层104和p型沟道层105均为二维材料,形成异质结,异质结的界面平整,缺陷少,减少缺陷处电子的聚集,可减少电子的泄露,易于电子的快速写入和擦除。

78.根据本公开的实施例,栅层100的开启电压与阻挡层103的厚度正相关。其中,开启电压定义为n型沟道层104、p型沟道层105的开关比大于103时栅极100施加的最小电压。阻挡层103的厚度越薄,栅级100开启电压越小,因此,浮栅存储器的阻挡层103所用材料可为纳米级的二维材料,栅层100开启电压低,施加很小的电压,就可以实现隧穿,降低了功耗。

79.应当理解,本公开实施例提供的各层结构的材料类型及尺寸参数并不是任意选择,而是在本公开实施例提供的浮栅存储器结构的基础上,通过合理设计,进一步提升浮栅存储器的快速及低功耗擦写和浮栅存储器的多级存储特性的实现效果。

80.基于同一发明构思,本公开实施例还提供一种浮栅存储器的制备方法。

81.为了便于描述,下面以n型沟道层104形成于阻挡层103上的第一区域,p型沟道层105形成于阻挡层103上的第二区域且与n型沟道层104远离阻挡层103的表面接触为例进行描述。

82.图4示意性示出了本公开实施例提供的浮栅存储器制备方法的流程图。图5a-5e示

意性示出了本公开实施例提供的浮栅存储器制备方法各操作对应的结构图。

83.参阅图4,结合图5a-5e,该浮栅存储器的制备方法例如可以包括操作s201~操作s205。

84.在操作s201,提供一栅层,在栅层上制备绝缘层。

85.在本公开一实施例中,可以采用热氧化法在栅层100上制备绝缘层101。制备得到的结构如图5a示。

86.在操作s202,在绝缘层上制备浮栅层。

87.在本公开一实施例中,可以采用化学气相沉积(vapor deposition,cvd)生长或者机械剥离的方法把浮栅层覆盖到绝缘层101表面,得到整块的浮栅层,再通过电子束曝光(electron beam lithography,ebl)及反应离子刻蚀(reactive ion etching,rie)将整块的浮栅层刻蚀,得到特定形状的浮栅层102。制备得到的结构如图5b示。

88.在操作s203,在浮栅层上制备阻挡层。

89.在本公开一实施例中,可以采用机械剥离的方法将阻挡层103覆盖到浮栅层102上。制备得到的结构如图5c示。

90.在操作s204,在阻挡层上的第一区域制备n型沟道层。

91.在本公开一实施例中,可以采用机械剥离的方法将n型沟道层104覆盖到阻挡层103上的第一区域。制备得到的结构如图5d示。

92.在操作s205,在阻挡层上的第二区域制备p型沟道层,并使p型沟道层与n型沟道层远离阻挡层的表面接触。

93.在本公开一实施例中,可以采用机械剥离的方法将p型沟道层105覆盖到阻挡层103上的第二区域,并使p型沟道层与n型沟道层远离阻挡层的表面接触,得到浮栅存储器。制备得到的结构如图5e示。

94.其中,n型沟道层的材料为n型二维半导体材料,p型沟道层的材料为p型二维半导体材料,第一区域和第二区域为不同区域,浮栅层包括允许存储电子和释放电子的允许状态,以及禁止存储电子和释放电子的禁止状态。在向栅层施加储存偏压的情况下,沟道层的电子隧穿进入处于允许状态的浮栅层,实现处于允许状态的浮栅层存储电子;在向栅层施加释放偏压的情况下,处于允许状态的浮栅层存储的电子隧穿回到沟道层,实现所述处于允许状态的浮栅层释放电子。

95.应当理解,位置关系为p型沟道层105形成于阻挡层103上的第一区域,n型沟道层104形成于阻挡层103上的第二区域且与p型沟道层105远离阻挡层103的表面接触的浮栅层存储制备方法与图4所示的制备方法类似,不同之处在于制备沟道层的过程中n型沟道层104和p型沟道层105的制备顺序不同,此处不再赘述,具体请参见图4所示的制备方法。

96.应当理解,n型沟道层与p型沟道层在横向方向上平行邻接接触设置的浮栅层存储制备方法与图4所示的制备方法的操作s201~操作s203相同,不同之处在于:在制作沟道层的过程中,n型沟道层与p型沟道层为同一种二维材料,通过在左右两侧的第一区域和第二区域进行不同掺杂和/或过设置左右两侧的第一区域和第二区域二维材料的厚度使第一区域和第二区域的二维材料呈现n型和p型。此处不再赘述,具体请参见图4所示的制备方法。

97.应当理解,bjt型沟道层浮栅存储器制备方法与图4所示的制备方法的操作s201~操作s203相同,不同之处在于:在制作沟道层的过程中,需要在阻挡层103上左右两侧定义

具有一定间隔的两个第一区域,在这两个第一区域形成同种类型的半导体沟道层,再在第二区域形成与第一区域类型相反的半导体沟道层,第二区域的沟道层与两侧的第一区域的沟道层远离阻挡层103的表面接触或第二区域的沟道层与两侧的第一区域的沟道层平行邻接接触,此处不再赘述,具体请参见图4所示的制备方法。

98.应当理解,mosfet型沟道层浮栅存储器制备方法与图4所示的制备方法的操作s201~操作s203相同,不同之处在于:在制作沟道层的过程中,需要在阻挡层103上左右两侧定义具有一定间隔的两个第一区域,在这两个第一区域形成同种类型的半导体沟道层,再在第二区域形成与第一区域类型相反的半导体沟道层,第二区域的沟道层与两侧的第一区域的沟道层远离阻挡层103的表面接触或第二区域的沟道层与两侧的第一区域的沟道层平行邻接接触,并在该第二区域的沟道层上覆盖一层阻挡层103,此处不再赘述,具体请参见图4所示的制备方法。

99.下面列举具体的示例对制备方法进行进一步说明。

100.示例一

101.二维材料p-n二极管浮栅存储器的制备过程为:采用n型掺杂的硅作为栅层100,在n型掺杂的硅上利用热氧化法形成300nm的sio2作为绝缘层101。采用cvd生长在sio2上形成厚度为7.6nm的多层石墨烯(mlg)作为浮栅层,采用电子束曝光及反应离子刻蚀将多层石墨烯(mlg)刻蚀成特定形状,形成浮栅层102。在浮栅层102上形成厚度为10nm的al2o3作为阻挡层103。在al2o3上形成厚度为5nm的mos2作为n型沟道层104,在al2o3上形成厚度为6nm的wse2作为p型沟道层105,并且p型沟道层与n型沟道层边缘接触,得到wse

2-mos2/al2o3/mlg二维材料p-n二极管浮栅存储器。

102.示例二

103.该二维材料p-n二极管浮栅存储器与示例一的不同之处在于:n型沟道层104的材料为mote2,p型沟道层105的材料为gase,阻挡层103的材料为h-bn,得到gase-mote2/h-bn/mlg二维材料p-n二极管浮栅存储器。

104.示例三

105.该二维材料p-n二极管浮栅存储器与示例一的不同之处在于:浮栅层102的材料为黑磷(bp),阻挡层103的材料为h-bn,n型沟道层104的材料为ws2,得到wse

2-ws2/h-bn/bp二维材料p-n二极管浮栅存储器。

106.示例四

107.该二维材料p-n二极管浮栅存储器与示例一的不同之处在于:浮栅层102的材料为mlg,阻挡层103的材料为al2o3,p型沟道层105的材料为α-mns,得到α-mns-mos2/al2o3/mlg二维材料p-n二极管浮栅存储器。

108.示例五

109.该二维材料浮栅存储器与示例一的不同之处在于:沟道层为bjt型沟道层结构,其中两个第一区域的n型沟道层材料为mos2,中间的第二区域的p型沟道层为wse2,得到mos

2-wse

2-mos2/al2o3/mlg二维材料bjt型浮栅存储器。

110.示例六

111.该二维材料浮栅存储器与示例一的不同之处在于:沟道层为mosfet型沟道层结构,其中两个第一区域的n型沟道层材料为mos2,中间的第二区域的p型沟道层为wse2,p型沟

道层上覆盖厚度为10nm的al2o3,得到mos

2-wse

2-mos2/al2o3/mlg二维材料mosfet型浮栅存储器。

112.需要说明的是,本公开的实施例中浮栅存储器制备方法部分与本公开的实施例中浮栅存储器结构部分是相对应的,其具体实施细节及带来的技术效果也是相同的,在此不再赘述。

113.以上所述的具体实施例,对本公开的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本公开的具体实施例而已,并不用于限制本公开,凡在本公开的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。