gpu的调试装置、gpu及调试系统

技术领域

1.本发明涉及硬件测试技术领域,具体涉及一种gpu的调试装置、gpu及调试系统。

背景技术:

2.图形处理器(英语:graphics processing unit,缩写:gpu),又称显示核心、视觉处理器、显示芯片,是一种专门在个人电脑、工作站、游戏机和一些移动设备(如平板电脑、智能手机等)上做图像和图形相关运算工作的微处理器。

3.gpu的调试能够确定gpu的性能结果,从而根据得到的性能结果对gpu进行修复或淘汰,避免影响整个设备的处理性能。然而,在现有技术中,无法很好对gpu进行调试,导致得到的性能结果的可信度较低。

技术实现要素:

4.针对现有技术中所存在的不足,本发明提供一种gpu的调试装置、gpu及调试系统。

5.第一方面,在一个实施例中,本发明提供一种gpu的调试装置,用于对gpu进行调试,gpu包括命令处理器以及分别与命令处理器连接的核组和配套模块;调试装置包括:与核组连接的调试模块,以及分别与调试模块和命令处理器连接的调试控制器;调试控制器用于接收调试主机发送的初始调试指令,对初始调试指令进行解析,得到解析指令;若解析指令包括第一目标调试指令以及第二目标调试指令,则将第一目标调试指令发送至调试模块,以及将第二目标调试指令发送至命令处理器;第一目标调试指令用于指示调试模块控制核组进行调试,以使核组发送对应的调试结果数据;第二目标调试指令用于指示命令处理器控制配套模块发送对应的调试配置数据,以使调试主机得到调试结果数据和调试配置数据,根据调试结果数据和调试配置数据,确定gpu的性能结果。

6.在一个实施例中,调试模块包括分别与调试控制器和核组连接的调试状态模块、与调试状态模块连接的调试内存模块;调试状态模块用于解析第一目标调试指令,得到第一调试命令以及调试程序,将调试程序发送至调试内存模块进行存储,将第一调试命令发送至核组;第一调试命令用于指示核组获取调试内存模块中的调试程序,根据调试程序进行调试。

7.在一个实施例中,核组设有多个,调试模块设有多个,调试模块与核组一一对应,每个调试模块分别与对应的核组以及调试控制器连接。

8.在一个实施例中,调试装置还包括:分别与核组和配套模块连接的调试总线,分别与调试控制器和调试总线连接的数据存储模块,数据存储模块配置有数据收发接口,数据存储模块通过数据收发接口与调试

主机进行数据传输;调试总线用于将核组输出的调试结果数据和配套模块输出的调试配置数据发送至数据存储模块;数据存储模块用于在调试控制器的控制下,通过数据收发接口接收调试主机发送的初始调试指令,并将初始调试指令发送至调试控制器,以及通过数据收发接口将调试总线发送的调试结果数据和调试配置数据发送至调试主机。

9.在一个实施例中,核组包括第一控制核以及分别与第一控制核连接的多个核单元,每个核单元包括与第一控制核连接的第二控制核以及分别与第二控制核连接的多个处理核,调试模块与第一控制核连接,调试总线分别与每个核单元中的每个处理核连接;调试模块具体用于解析第一目标调试指令,得到第一调试命令,将第一调试命令发送至第一控制核;第一调试命令用于指示第一控制核分别向每个核单元中的第二控制核发送第二调试命令;第二调试命令用于指示对应的核单元中的第二控制核分别向该核单元中的每个处理核发送第三调试命令;第三调试命令用于指示该核单元中对应的处理核进行调试,将对应的调试结果数据发送至调试总线。

10.在一个实施例中,调试装置还包括:多个第一数据选择器,第一数据选择器与核单元一一对应,每个第一数据选择器分别与对应的核单元中的第二控制核以及每个处理核连接;分别与每个第一数据选择器连接的第二数据选择器,第二数据选择器与调试总线连接;每个第一数据选择器用于接收对应的核单元中的第二控制核发送的数据选择命令以及接收对应的核单元中每个处理核发送的初始调试结果数据,根据数据选择命令,从每个处理核发送的初始调试结果数据得到调试结果数据,将调试结果数据发送至第二数据选择器;数据选择命令根据第二调试命令得到;第二数据选择器用于将每个第一数据选择器输出的调试结果数据进行整合,将整合后的调试结果数据发送至调试总线。

11.在一个实施例中,命令处理器通过系统总线分别与核组和配套模块连接,数据存储模块与系统总线连接;数据存储模块还用于在调试控制器的控制下,通过数据收发接口将系统总线发送的命令处理器、核组以及配套模块之间交互的实时运行数据发送至调试主机。

12.在一个实施例中,数据存储模块还分别配置有显示接口和逻辑分析接口;数据存储模块还用于在调试控制器的控制下,通过显示接口将调试结果数据、调试配置数据或实时运行数据中的显示数据发送至显示设备进行显示;数据存储模块还用于在调试控制器的控制下,通过逻辑分析接口将调试结果数据、调试配置数据或实时运行数据中的逻辑分析数据发送至逻辑分析设备进行逻辑分析。

13.第二方面,在一个实施例中,本发明提供一种可支持调试的gpu,包括命令处理器以及分别与命令处理器连接的核组和配套模块,还包括:

上述任一种实施例中的gpu的调试装置,gpu的调试装置中的调试模块与核组连接,gpu的调试装置中的调试控制器与命令处理器连接。

14.第三方面,在一个实施例中,本发明提供一种gpu调试系统,包括上述任一种实施例中的可支持调试的gpu;还包括:与可支持调试的gpu中的调试控制器连接的调试主机。

15.通过上述gpu的调试装置、gpu及调试系统,与调试主机连接的调试控制器,能够解析调试主机发送的初始调试指令,得到解析指令,其中解析指令可以包括第一目标调试指令和第二目标调试指令,由于调试控制器分别与调试模块和命令处理器连接,因此可分别将第一目标调试指令和第二目标调试指令发送至调试模块和命令处理器,与核组连接的调试模块,能够根据第一目标调试指令对核组进行调试,从而使核组向调试主机返回对应的调试结果数据,命令处理器能够根据第二目标调试指令控制配套模块向调试主机返回对应的调试配置数据,从而调试主机能够同时获取到gpu工作时针对核组的调试结果数据以及针对配套模块的调试配置数据,进而进行全面分析,最终确定得到可信度较高的gpu的性能结果。

附图说明

16.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

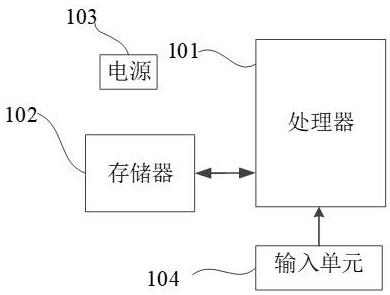

17.图1为本发明一个实施例中gpu的调试装置的结构示意图;图2为本发明一个实施例中包含调试内存模块的gpu的调试装置的结构示意图;图3为本发明一个实施例中核组和调试模块都设有多个的gpu的调试装置的结构示意图;图4为本发明一个实施例中包含调试总线、数据存储模块以及数据收发接口的gpu的调试装置的结构示意图;图5为本发明一个实施例中包含核组具体结构的gpu的调试装置的结构示意图;图6为本发明一个实施例中第一数据选择器和第二数据选择器的gpu的调试装置的结构示意图;图7为本发明一个实施例中数据存储模块与系统总线连接的gpu的调试装置的结构示意图;图8为本发明一个实施例中包含显示接口和逻辑分析接口的gpu的调试装置的结构示意图;图9为本发明一个实施例中组合各实施例的gpu的调试装置的结构示意图;图10为本发明一个实施例中调试主机的内部结构示意图。

具体实施方式

18.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于

本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

19.在本发明的描述中,需要理解的是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。在本技术中,“示例性”一词用来表示“用作例子、例证或说明”。本技术中被描述为“示例性”的任何实施例不一定被解释为比其它实施例更优选或更具优势。为了使本领域任何技术人员能够实现和使用本发明,给出了以下描述。在以下描述中,为了解释的目的而列出了细节。应当明白的是,本领域普通技术人员可以认识到,在不使用这些特定细节的情况下也可以实现本发明。在其它实例中,不会对公知的结构和过程进行详细阐述,以避免不必要的细节使本发明的描述变得晦涩。因此,本发明并非旨在限于所示的实施例,而是与符合本技术所公开的原理和特征的最广范围相一致。

20.第一方面,如图1所示,在一个实施例中,本发明提供一种gpu的调试装置,用于对gpu进行调试,gpu包括命令处理器(command processor,cp)以及分别与命令处理器连接的核组(core group,cg)和配套模块;其中,配套模块包括光栅化处理模块(raster operations,rops)、纹理模块(texture memory)、显示控制模块(display controller)等;其中,gpu进行工作时,核组会与命令处理器进行交互,使命令处理器对配套模块进行参数配置,使配套模块能够与核组一同配合,最终完成工作任务;其中,本实施例中的gpu的调试装置可以gpu的内部集成装置,即为gpu的一部分,当然,在其他实施例中,该gpu的调试装置也可以是独立于gpu之外的外部独立装置;当该gpu的调试装置为gpu的内部集成装置时,可直接将该gpu与对应的调试主机连接,从而完成对应的调试操作;调试装置包括:与核组连接的调试模块(debug module),以及分别与调试模块和命令处理器连接的调试控制器(debug controller);其中,当该gpu的调试装置为独立于gpu之外的外部独立装置时,对应的gpu需要具备相应的对外接口,包括对内连接核组且对外用于连接调试模块的接口,对内连接命令处理器且对外用于连接调试控制器的接口;其中,调试模块专门负责核组的调试工作,其受调试控制器的指示;调试模块与调试控制器和核组进行通信时,采用gpu的内部数据格式;调试控制器用于接收调试主机发送的初始调试指令,对初始调试指令进行解析,得到解析指令;其中,调试控制器与调试主机连接,当需要对gpu进行调试时,调试主机可根据实际的调试需求,生成对应的初始调试指令,然后将初始调试指令发送至调试控制器;初始调试指令用于指示调试控制器如何进行后续调试工作,比如初始调试指令用于指示调试控制器只需将核组对应的调试结果数据进行返回,或者指示调试控制器需同时将核组对应的调试结果数据以及配套模块对应的调试配置数据进行返回;因此,当调试控制器接收到初始

调试指令后,需要对该初始调试指令进行解析,确定调试主机的调试需求,并得到对应的解析指令,解析指令用于控制调试模块和/或命令处理器;若解析指令包括第一目标调试指令以及第二目标调试指令,则将第一目标调试指令发送至调试模块,以及将第二目标调试指令发送至命令处理器;其中,若调试主机的调试需求是需要同时将核组对应的调试结果数据以及配套模块对应的调试配置数据进行返回,则调试控制器对初始调试指令进行解析后,可以确定到同时将核组对应的调试结果数据以及配套模块对应的调试配置数据进行返回的调试需求,因此可根据该需求生成对应的第一目标调试指令以及第二目标调试指令,并将第一目标调试指令发送至调试模块,以及将第二目标调试指令发送至命令处理器;第一目标调试指令用于指示调试模块控制核组进行调试,以使核组发送对应的调试结果数据;其中,第一目标调试指令中可以包含核组调试所需要的调试程序,然后调试模块接收到该第一目标调试指令后,可对其进行解析,得到对应的调试程序,在本实施例中,调试模块可将对应的调试程序发送至gpu的系统内存中进行存储,同步向核组发送对应的调试命令,该调试命令用于指示核组进入调试模式;其中,当核组接收到调试命令后,若gpu当前已经被安装于对应的设备中并正在执行相应的任务,则会停止当前任务(即该方式可以理解为破坏性扫描的调试方式),并立即进入调试模式,若gpu当前并未安装于对应的设备中,则接收到调试命令后直接进入调试模式;然后访问系统内存,获取存储在系统内存中的调试程序,进而执行该程序以实现调试,最后将调试后的调试结果数据返回至调试主机;其中,调试结果数据主要是指核组中对应核的寄存器数据;当然在其他实施例中,还可以是指核组执行程序后生成并存储在系统内容中的日志数据,但日志数据无法准确的对gpu进行性能分析,对于日志数据,调试模块可以再次访问系统内存,然后获取存储其中的日志数据,进而再通过调试控制器返回至调试主机;其中,对于核的寄存器数据,由于是核组自己生成并缓存,因此核组可对外发送,具体的,在本实施例中,核组可将对应的寄存器数据返回至调试模块,然后由调试模块通过调试控制器再返回至调试主机,由于调试控制器和调试模块不仅需要进行指令或命令的下发,还需要返回对应的寄存器数据,因此需要更合理的设计调试控制器、调试模块以及对应的核组之间的通信结构,以保证传输的可靠性,但仍然容易导致数据传输出现问题;第二目标调试指令用于指示命令处理器控制配套模块发送对应的调试配置数据,以使调试主机得到调试结果数据和调试配置数据,根据调试结果数据和调试配置数据,确定gpu的性能结果;其中,上述已经提到,gpu进行工作时,核组会与命令处理器进行交互,使命令处理器对配套模块进行参数配置,使配套模块能够与核组一同配合,最终完成工作任务;同理的,在核组执行调试程序以进行调试时,同样会与命令处理器进行交互,使命令处理器对配套模块进行对应的参数配置,从而使配套模块与核组一同配合,完成调试任务,在该过程中,当配套模块出现问题时,同样会影响到核组的运行,即只根据核组输出的调试结果数据,也无法准确分析gpu的性能结果,因此命令处理器接收到第二目标调试指令后,会控制配套模块将对应的调试配置数据返回至调试主机,以使调试主机能够同时根据调试结果数

据和调试配置数据进行综合分析;其中,同上述调试结果数据相似,调试配置数据主要是指配套模块中的配置寄存器实际的寄存器数据,配套模块可将该寄存器数据返回至命令处理器,然后由命令处理器通过调试控制器再返回至调试主机,由于调试控制器不仅需要进行指令或命令的下发,还需要返回对应的寄存器数据,因此需要更合理的设计调试控制器和命令处理器之间的通信结构,以保证传输的可靠性;其中,调试主机在接收到调试装置发送的调试结果数据和调试配置数据后,即可进行更加全面的综合分析,具体的,调试主机可执行一种调试数据的分析方法,从而实现自动化,提高确定gpu的性能结果的效率;其中,调试主机在确定到gpu的性能结果较差时,可再次根据该性能结果的具体信息(比如具体是由哪些调试数据引起的),生成新的初始调试指令,新的初始调试指令与之前的初始调试指令中的调试需求不同,即之前的初始调试指令可以是默认的调试需求,而新的初始调试指令则是根据得到的性能结果而调整后的调试需求(即针对性调试),从而提高整体调试的效果。

21.通过上述gpu的调试装置,与调试主机连接的调试控制器,能够解析调试主机发送的初始调试指令,得到解析指令,其中解析指令可以包括第一目标调试指令和第二目标调试指令,由于调试控制器分别与调试模块和命令处理器连接,因此可分别将第一目标调试指令和第二目标调试指令发送至调试模块和命令处理器,与核组连接的调试模块,能够根据第一目标调试指令对核组进行调试,从而使核组向调试主机返回对应的调试结果数据,命令处理器能够根据第二目标调试指令控制配套模块向调试主机返回对应的调试配置数据,从而调试主机能够同时获取到gpu工作时针对核组的调试结果数据以及针对配套模块的调试配置数据,进而进行全面分析,最终确定得到可信度较高的gpu的性能结果。

22.如图2所示,在一个实施例中,调试模块包括分别与调试控制器和核组连接的调试状态模块、与调试状态模块连接的调试内存模块;调试状态模块用于解析第一目标调试指令,得到第一调试命令以及调试程序,将调试程序发送至调试内存模块进行存储,将第一调试命令发送至核组;其中,与上述实施例的区别在于,本实施例在对第一目标调试指令进行解析并得到对应的调试程序后,不再访问gpu的系统内存,并将该调试程序存储至系统内存中,而是直接存储在调试模块内的调试内存模块中,由于调试程序只是为了实现调试的目的,因此其数据量很小,即调试内存模块的存储空间也不需要多大;第一调试命令用于指示核组获取调试内存模块中的调试程序,根据调试程序进行调试;其中,当核组接收到第一调试命令后,同上述实施例一致,若gpu当前已经被安装于对应的设备中并正在执行相应的任务,则会停止当前任务,并立即进入调试模式,若gpu当前并未安装于对应的设备中,则接收到调试命令后直接进入调试模式;区别在于,本实施例中的核组不再访问系统内存,而是直接访问调试模块内的调试内存模块,进而更加快速可靠的获取到对应的调试程序。

23.通过在调试模块内加设对应的调试内存模块,使得解析到的调试程序可以直接存储在调试模块中,使得核组能够更加快速可靠的获取到对应的调试程序,提高了调试的效

率。

24.如图3所示,在一个实施例中,核组设有多个,调试模块设有多个,调试模块与核组一一对应,每个调试模块分别与对应的核组以及调试控制器连接;其中,在gpu中,核组通常有多个,在本实施例中,可分别针对每个核组配置一个调试模块,即每个调试模块只负责一个核组的调试工作,从而保证每个核组的调试工作都能够可靠的进行;其中,当gpu的调试装置为gpu以外的外部独立装置时,可设置较多的调试模块,以适应不同数量的核组的gpu,提高了gpu的调试装置的适用性,扩大了调试场景。

25.如图4所示,在一个实施例中,调试装置还包括:分别与核组和配套模块连接的调试总线,分别与调试控制器和调试总线连接的数据存储模块,数据存储模块配置有数据收发接口,数据存储模块通过数据收发接口与调试主机进行数据传输;其中,数据收发接口包括usb接口、pcie接口、jtag接口等;其中,上述实施例已经提到,核组可通过调试模块以及调试控制器来向调试主机返回对应的调试结果数据,配套模块可通过命令处理器以及调试控制器来向调试主机返回对应的调试配置数据,但该方式对调试控制器、调试模块、核组以及调试命令器之间的通信结构有较高要求,并且也仍然容易出现传输问题;因此,在本实施例中,设置对应的调试总线和数据存储模块,使得核组和配套模块能够直接通过调试总线和数据存储模块返回至调试主机,而无需再通过调试模块、调试控制器以及命令处理器进行传输,也无需对通信结构有较高要求,也不会出现传输问题,提高了数据传输的可靠性;调试总线用于将核组输出的调试结果数据和配套模块输出的调试配置数据发送至数据存储模块;数据存储模块用于在调试控制器的控制下,通过数据收发接口接收调试主机发送的初始调试指令,并将初始调试指令发送至调试控制器,以及通过数据收发接口将调试总线发送的调试结果数据和调试配置数据发送至调试主机;其中,数据存储模块作为与调试主机的传输枢纽,其受调试控制器的指示,比如调试主机需要向调试控制器发送初始调试指令时,调试主机可先与对应的数据收发接口进行连接,然后调试控制器可控制数据存储模块对数据收发接口中的初始调试指令进行接收,然后再发送至调试控制器;同理的,当需要将调试结果数据和调试配置数据返回至调试主机时,调试控制器可控制数据存储模块通过调试总线访问核组以及配套模块,从而读取对应的调试结果数据和调试配置数据,然后再通过数据收发接口返回至调试主机。

26.如图5所示,在一个实施例中,核组包括第一控制核以及分别与第一控制核连接的多个核单元(core unit),每个核单元包括与第一控制核连接的第二控制核以及分别与第二控制核连接的多个处理核,调试模块与第一控制核连接,调试总线分别与每个核单元中的每个处理核连接;调试模块具体用于解析第一目标调试指令,得到第一调试命令,将第一调试命令发送至第一控制核;其中,第一控制核作为核组的最上级单位,可以控制下级单位完成相应的操作,因此调试模块在得到第一调试命令后,将第一调试命令发送至核组的最上级单位,即第一控

制核,由第一控制核进行后续控制,需要说明的是,第一控制核进行后续控制是根据调试模块发送的第一调试命令实现的;第一调试命令用于指示第一控制核分别向每个核单元中的第二控制核发送第二调试命令;其中,由于第一控制核主要起到控制功能,因此第一控制核在接收到第一调试命令后,需要基于第一调试命令继续下发命令,即分别向每个核单元中的第二控制核发送第二调试命令;其中,需要注意的是,在本实施例中,第一控制核可以基于第一调试命令分别向每个核单元中的第二控制核发送第二调试命令,在其他实施例中,也可以基于第一调试命令向部分核单元中的第二控制核发送第二调试命令,具体取决于第一调试命令,第一调试命令又取决于第一目标调试指令,第一目标调试指令又取决于初始调试指令,因此需要对哪些核单元进行调试,都是由调试主机决定,以实现调试的灵活性;第二调试命令用于指示对应的核单元中的第二控制核分别向该核单元中的每个处理核发送第三调试命令;其中,第二控制核同第一控制核相似,主要起到控制功能,因此第二控制核在接收到第二调试命令后,需要基于第二调试命令继续下发命令,即分别向该核单元中的每个处理核发送第三调试命令;其中,同上述第一调试命令相似,在本实施例中,第二控制核可以基于第二调试命令分别向该核单元中的每个处理核发送第三调试命令,也可以基于第二调试命令向该核单元中的部分处理核发送第三调试命令,需要对哪些处理核进行调试,都是由调试主机决定,以实现调试的灵活性;第三调试命令用于指示该核单元中对应的处理核进行调试,将对应的调试结果数据发送至调试总线;其中,核单元中的处理核主要起到数据处理的功能,也是最底层的核,因此将处理核对应的调试结果数据(即寄存器数据)进行返回,从而当调试主机根据调试结果数据进行分析时,能够得到可信度更高的性能结果;在其他实施例中,也可以是返回第一控制核和第二控制核的调试结果数据(即寄存器数据);其中,需要说明的是,处理核的调试是基于调试模块对第一目标调试指令解析得到的调试程序,关于调试程序的具体细节可参照上述实施例。

27.如图6所示,在一个实施例中,调试装置还包括:多个第一数据选择器,第一数据选择器与核单元一一对应,每个第一数据选择器分别与对应的核单元中的第二控制核以及每个处理核连接;分别与每个第一数据选择器连接的第二数据选择器,第二数据选择器与调试总线连接;每个第二调试命令还用于指示对应的核单元中的第二控制核向对应的第一数据选择器发送数据选择命令;每个第一数据选择器用于接收对应的核单元中的第二控制核发送的数据选择命令以及接收对应的核单元中每个处理核发送的初始调试结果数据,根据数据选择命令,从每个处理核发送的初始调试结果数据得到调试结果数据,将调试结果数据发送至第二数据

选择器;数据选择命令根据第二调试命令得到;其中,在实际调试过程中,可能只针对核单元中的部分处理核进行调试,或者对每个处理核都进行了调试,但只需要某几个处理核的调试结果数据,因此在本实施例中,第二控制核基于第二调试命令可以确定需要将哪些处理核的调试结果数据进行返回,从而向第一数据选择器发送对应的数据选择命令;第一数据选择器在接收到数据选择命令后,即可将对应处理核的调试结果数据进行返回,即发送至第二数据选择指令;其中,若只针对处理核的调试结果数据,而不考虑控制核的调试结果数据,因此数据选择过程已经在第一数据选择器全部完成,对应的第二数据选择器只需要对每个第一数据选择器发送的调试结果数据进行整合即可;其中,在其他实施例中,还可以同时针对控制核的调试结果数据,即第二数据选择器还与控制核连接,如此,第二数据选择器需要对第一数据选择器发送的调试结果数据以及控制核发送的调试结果数据进行选择,具体过程可参照上述第一数据选择器。

28.如图7所示,在一个实施例中,命令处理器通过系统总线分别与核组和配套模块连接,数据存储模块与系统总线连接;数据存储模块还用于在调试控制器的控制下,通过数据收发接口将系统总线发送的命令处理器、核组以及配套模块之间交互的实时运行数据发送至调试主机;其中,系统总线负责命令处理器、配套模块以及核组之间的交互,其上传输着命令处理器、核组以及配套模块之间交互的实时运行数据,因此在本实施例中,当gpu正常运行时,也可以通过数据存储模块获取该实时运行数据,然后返回至调试主机(即简单扫描的调试方式);其中,需要注意的是,由于实时运行数据是运行过程中的所有交互数据,数据量较大,且这些数据都是串行发送,调试主机在接收到这些数据后,需要经过比较复杂的处理后才能够进行分析;而上述的破坏性扫描的调试方式,是控制gpu返回指定的数据,因此可直接进行分析。

29.如图8所示,在一个实施例中,数据存储模块还分别配置有显示接口和逻辑分析接口;其中,显示接口包括displayport 等接口,主要是用于与示波器等显示设备进行连接;其中,逻辑分析接口包括mc(外部存储器引脚)等,主要是用于与逻辑分析仪进行连接;数据存储模块还用于在调试控制器的控制下,通过显示接口将调试结果数据、调试配置数据或实时运行数据中的显示数据发送至显示设备进行显示;其中,部分数据可以不通过调试主机进行分析,比如一些具有波形的数据,则可以直接通过显示接口发送至示波器,从而根据示波器显示出的波形进行分析,在该场景下,可在不使用调试主机的情况下进行分析,具体的,该方式需要针对实时运行数据,当然在使用调试主机的情况下,也可以针对调试结果数据和调试配置数据;数据存储模块还用于在调试控制器的控制下,通过逻辑分析接口将调试结果数据、调试配置数据或实时运行数据中的逻辑分析数据发送至逻辑分析设备进行逻辑分析;其中,同上述显示接口相似,部分数据可以不通过调试主机进行分析,比如一些具

有标志位的数据,则可以直接通过逻辑分析接口发送至逻辑分析仪,从而根据逻辑分析仪的分析结果进行二次分析,具体的,该方式需要针对实时运行数据,当然在使用调试主机的情况下,也可以针对调试结果数据和调试配置数据;需要注意的是,在使用逻辑分析仪时,还需要配套使用一个分析内存,用于存储一定数据量的数据,逻辑分析仪从分析内存中获取数据并进行逻辑分析。

30.为了使本发明的结构更加清楚,现对上述实施例进行组合说明,具体的,如图9所示,本发明提供一种gpu的调试装置,用于对gpu进行调试,gpu包括命令处理器以及分别与命令处理器连接的多个核组和配套模块,命令处理器通过系统总线分别与核组和配套模块连接,核组包括第一控制核以及分别与第一控制核连接的多个核单元,每个核单元包括与第一控制核连接的第二控制核以及分别与第二控制核连接的多个处理核;调试装置包括与核组连接的调试模块,以及分别与调试模块和命令处理器连接的调试控制器;调试模块包括分别与调试控制器和核组连接的调试状态模块、与调试状态模块连接的调试内存模块;调试模块设有多个,调试模块与核组一一对应,每个调试模块分别与对应的核组以及调试控制器连接;分别与核组和配套模块连接的调试总线,分别与调试控制器和调试总线连接的数据存储模块,数据存储模块配置有数据收发接口,数据存储模块通过数据收发接口与调试主机进行数据传输;多个第一数据选择器,第一数据选择器与核单元一一对应,每个第一数据选择器分别与对应的核单元中的第二控制核以及每个处理核连接;分别与每个第一数据选择器连接的第二数据选择器,第二数据选择器通过第三数据选择器与调试总线连接;数据存储模块还分别配置有显示接口和逻辑分析接口;其中,命令处理器、系统总线、核组、配套模块以及调试装置的具体功能可参照上述实施例,在此不再赘述。

31.第二方面,在一个实施例中,本发明提供一种可支持调试的gpu,包括命令处理器以及分别与命令处理器连接的核组和配套模块,还包括:上述任一种实施例中的gpu的调试装置,gpu的调试装置中的调试模块与核组连接,gpu的调试装置中的调试控制器与命令处理器连接。

32.通过上述可支持调试的gpu,与调试主机连接的调试控制器,能够解析调试主机发送的初始调试指令,得到解析指令,其中解析指令可以包括第一目标调试指令和第二目标调试指令,由于调试控制器分别与调试模块和命令处理器连接,因此可分别将第一目标调试指令和第二目标调试指令发送至调试模块和命令处理器,与核组连接的调试模块,能够根据第一目标调试指令对核组进行调试,从而使核组向调试主机返回对应的调试结果数据,命令处理器能够根据第二目标调试指令控制配套模块向调试主机返回对应的调试配置数据,从而调试主机能够同时获取到gpu工作时针对核组的调试结果数据以及针对配套模块的调试配置数据,进而进行全面分析,最终确定得到可信度较高的gpu的性能结果。

33.第三方面,在一个实施例中,本发明提供一种gpu调试系统,包括上述任一种实施例中的可支持调试的gpu;还包括:与可支持调试的gpu中的调试控制器连接的调试主机。

34.通过上述gpu调试系统,与调试主机连接的调试控制器,能够解析调试主机发送的初始调试指令,得到解析指令,其中解析指令可以包括第一目标调试指令和第二目标调试指令,由于调试控制器分别与调试模块和命令处理器连接,因此可分别将第一目标调试指

令和第二目标调试指令发送至调试模块和命令处理器,与核组连接的调试模块,能够根据第一目标调试指令对核组进行调试,从而使核组向调试主机返回对应的调试结果数据,命令处理器能够根据第二目标调试指令控制配套模块向调试主机返回对应的调试配置数据,从而调试主机能够同时获取到gpu工作时针对核组的调试结果数据以及针对配套模块的调试配置数据,进而进行全面分析,最终确定得到可信度较高的gpu的性能结果。

35.在一个实施例中,本发明提供一种调试主机,如图10所示,其示出了本发明所涉及的调试主机的结构,具体来讲:该调试主机可以包括一个或者一个以上处理核心的处理器101、一个或一个以上计算机可读存储介质的存储器102、电源103和输入单元104等部件。本领域技术人员可以理解,图10中示出的调试主机的结构并不构成对调试主机的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。其中:处理器101是该调试主机的控制中心,利用各种接口和线路连接整个调试主机的各个部分,通过运行或执行存储在存储器102内的软件程序和/或模块,以及调用存储在存储器102内的数据,执行调试主机的各种功能和处理数据,从而对调试主机进行整体监控。可选的,处理器101可包括一个或多个处理核心;优选的,处理器101可集成应用处理器和调制解调处理器,其中,应用处理器主要处理操作系统、用户界面和计算机程序等,调制解调处理器主要处理无线通信。可以理解的是,上述调制解调处理器也可以不集成到处理器101中。

36.存储器102可用于存储软件程序以及模块,处理器101通过运行存储在存储器102的软件程序以及模块,从而执行各种功能应用以及数据处理。存储器102可主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的计算机程序(比如声音播放功能、图像播放功能等)等;存储数据区可存储根据服务器的使用所创建的数据等。此外,存储器102可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件、闪存器件、或其他易失性固态存储器件。相应地,存储器102还可以包括存储器控制器,以提供处理器101对存储器102的访问。

37.调试主机还包括给各个部件供电的电源103,优选的,电源103可以通过电源管理系统与处理器101逻辑相连,从而通过电源管理系统实现管理充电、放电、以及功耗管理等功能。电源103还可以包括一个或一个以上的直流或交流电源、再充电系统、电源故障检测电路、电源转换器或者逆变器、电源状态指示器等任意组件。

38.该调试主机还可包括输入单元104,该输入单元104可用于接收输入的数字或字符信息,以及产生与用户设置以及功能控制有关的键盘、鼠标、操作杆、光学或者轨迹球信号输入。

39.尽管未示出,调试主机还可以包括显示单元等,在此不再赘述。具体在本实施例中,调试主机中的处理器101会按照如下的指令,将一个或一个以上的计算机程序的进程对应的可执行文件加载到存储器102中,并由处理器101来运行存储在存储器102中的计算机程序,以执行如下步骤:根据调试需求,生成初始调试指令;将初始调试指令发送至gpu的调试装置,以使gpu的调试装置根据初始调试指令对gpu进行调试;

接收gpu的调试装置发送的调试结果数据和调试配置数据;根据调试结果数据和调试配置数据,确定gpu的性能结果;其中,gpu的调试装置根据初始调试指令对gpu进行调试的具体细节可参照上述实施例。

40.通过上述调试主机,与调试主机连接的调试控制器,能够解析调试主机发送的初始调试指令,得到解析指令,其中解析指令可以包括第一目标调试指令和第二目标调试指令,由于调试控制器分别与调试模块和命令处理器连接,因此可分别将第一目标调试指令和第二目标调试指令发送至调试模块和命令处理器,与核组连接的调试模块,能够根据第一目标调试指令对核组进行调试,从而使核组向调试主机返回对应的调试结果数据,命令处理器能够根据第二目标调试指令控制配套模块向调试主机返回对应的调试配置数据,从而调试主机能够同时获取到gpu工作时针对核组的调试结果数据以及针对配套模块的调试配置数据,进而进行全面分析,最终确定得到可信度较高的gpu的性能结果。

41.本领域普通技术人员可以理解,上述实施例的任一种方法中的全部或部分步骤可以通过计算机程序来完成,或通过计算机程序控制相关的硬件来完成,该计算机程序可以存储于一计算机可读存储介质中,并由处理器进行加载和执行。

42.在一个实施例中,本发明提供一种存储介质,其中存储有多条计算机程序,该计算机程序能够被处理器进行加载,以执行如下步骤:根据调试需求,生成初始调试指令;将初始调试指令发送至gpu的调试装置,以使gpu的调试装置根据初始调试指令对gpu进行调试;接收gpu的调试装置发送的调试结果数据和调试配置数据;根据调试结果数据和调试配置数据,确定gpu的性能结果;其中,gpu的调试装置根据初始调试指令对gpu进行调试的具体细节可参照上述实施例。

43.通过上述存储介质,与调试主机连接的调试控制器,能够解析调试主机发送的初始调试指令,得到解析指令,其中解析指令可以包括第一目标调试指令和第二目标调试指令,由于调试控制器分别与调试模块和命令处理器连接,因此可分别将第一目标调试指令和第二目标调试指令发送至调试模块和命令处理器,与核组连接的调试模块,能够根据第一目标调试指令对核组进行调试,从而使核组向调试主机返回对应的调试结果数据,命令处理器能够根据第二目标调试指令控制配套模块向调试主机返回对应的调试配置数据,从而调试主机能够同时获取到gpu工作时针对核组的调试结果数据以及针对配套模块的调试配置数据,进而进行全面分析,最终确定得到可信度较高的gpu的性能结果。

44.本领域普通技术人员可以理解,本发明所提供的各实施例中所使用的对存储器、存储、数据库或其它介质的任何引用,均可包括非易失性和/或易失性存储器。非易失性存储器可包括只读存储器(rom)、可编程rom(prom)、电可编程rom(eprom)、电可擦除可编程rom(eeprom)或闪存。易失性存储器可包括随机存取存储器(ram)或者外部高速缓冲存储器。作为说明而非局限,ram以多种形式可得,诸如静态ram(sram)、动态ram(dram)、同步dram(sdram)、双数据率sdram(ddrsdram)、增强型sdram(esdram)、同步链路(synchlink) dram(sldram)、存储器总线(rambus)直接ram(rdram)、直接存储器总线动态ram(drdram)、

以及存储器总线动态ram(rdram)等。

45.由于该存储介质中所存储的计算机程序,可以执行本发明所提供的任一种实施例中的gpu的调试方法中的步骤,因此,可以实现本发明所提供的任一种实施例中的gpu的调试方法所能实现的有益效果,详见前面的实施例,在此不再赘述。

46.以上各个操作的具体实施可参见前面的实施例,在此不再赘述。

47.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见上文针对其他实施例的详细描述,此处不再赘述。

48.以上对本发明所提供的一种gpu的调试装置、gpu及调试系统进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

49.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。