1.本发明涉及半导体封装技术领域,尤其涉及一种芯片封装结构及其制作方法。

背景技术:

2.常用技术中芯片与电感之间的封装结构,由于产品性能设计要求,必须采用大铜柱连接塑封体和大电感,具体为芯片倒装设置于基板上表面,塑封料覆盖基板上表面及铜柱和芯片侧表面,并暴露出铜柱和芯片上表面,芯片上方设置电感,铜柱与电感周边的引脚电连接。

3.但是,对于现有这种封装结构中,铜柱底部与基板上表面接触面上通常会刷大量锡膏,使得铜柱焊接固定到基板上,在回流焊工艺中,铜柱底部的锡膏会出现大面积的锡珠,铜柱底部部分区域易形成空洞,回流焊工艺之后的封装产品在塑封过程中受热,铜柱底部的空洞气体膨胀推动铜柱上移,引起铜柱上表面和塑封料上表面不共面的问题,且随着铜柱向上移动,铜柱与基板之间、铜柱与电感之间的焊接质量很难保证。

技术实现要素:

4.本发明的目的在于提供一种芯片封装结构及其制作方法,以提高导电连接件与基板之间、电感与基板之间的焊接质量。

5.为实现上述发明目的之一,本发明一实施方式提供一种芯片封装结构,包括基板、至少一芯片、多个导电连接件和至少一电感,所述芯片设置于所述基板上表面并与所述基板电性连接,所述电感设置于所述芯片上方,所述导电连接件通过一焊接层固定连接于所述基板,所述电感通过所述导电连接件与所述基板电性连接,其中,所述导电连接件内部设置一通孔,所述通孔连通所述导电连接件的上表面和下表面。

6.作为本发明一实施方式中的进一步改进,所述导电连接件下表面连接所述通孔的部分区域朝内凹陷形成至少一条第一沟槽,所述第一沟槽至少将所述导电连接件下表面分成两个焊接区域,所述焊接层设置于所述焊接区域与所述基板之间。

7.作为本发明一实施方式中的进一步改进,所述导电连接件下表面连接所述通孔的部分区域朝内凹陷形成两条第一沟槽,所述两条第一沟槽相交呈十字型,将所述导电连接件下表面分成四个焊接区域,所述通孔连接于所述两条第一沟槽相交处,所述焊接层设置于所述焊接区域与所述基板之间。

8.作为本发明一实施方式中的进一步改进,所述导电连接件上表面连接所述通孔的部分区域朝内凹陷形成至少一条第二沟槽,所述电感周侧还设置电连接部,所述电感通过所述电连接部电性连接于所述导电连接件,所述电连接部与所述导电连接件之间还设置一导电胶层,所述导电胶层不完全覆盖所述第二沟槽。

9.作为本发明一实施方式中的进一步改进,所述导电连接件为铜柱。

10.本发明一实施方式提供一种芯片封装结构的制作方法,包括步骤:提供一基板和至少一芯片,将所述芯片贴装于所述基板上表面,并与所述基板电

性连接;提供多个导电连接件,在所述导电连接件内部形成一通孔,所述通孔连通所述导电连接件的上表面和下表面,将所述导电连接件通过一焊接层贴装于所述基板上表面;提供至少一电感,将所述电感贴装于所述芯片上方,通过所述导电连接件与所述基板电性连接。

11.作为本发明一实施方式中的进一步改进,所述提供多个导电连接件,在所述导电连接件内部形成一通孔,所述通孔连通所述导电连接件的上表面和下表面,具体包括:提供多个铜柱,在所述铜柱内部形成一通孔,所述通孔连通所述铜柱的上表面和下表面。

12.作为本发明一实施方式中的进一步改进,所述提供多个导电连接件,在所述导电连接件内部形成一通孔,所述通孔连通所述导电连接件的上表面和下表面,具体还包括:在所述导电连接件的下表面连接所述通孔的部分区域处朝内凹陷形成至少一条第一沟槽,所述第一沟槽至少将所述导电连接件下表面分成两个焊接区域;将所述焊接层设置于所述焊接区域处。

13.作为本发明一实施方式中的进一步改进,所述在所述导电连接件的下表面连接所述通孔的部分区域处朝内凹陷形成至少一条第一沟槽,具体包括:在所述导电连接件下表面连接所述通孔的部分区域朝内凹陷形成两条第一沟槽,所述两条第一沟槽相交呈十字型,将所述导电连接件下表面分成四个焊接区域,所述通孔连接于所述两条第一沟槽相交处;将所述焊接层设置于所述焊接区域处。

14.作为本发明一实施方式中的进一步改进,所述提供多个导电连接件,在所述导电连接件内部形成一通孔,所述通孔连通所述导电连接件的上表面和下表面,具体还包括:在所述导电连接件上表面连接所述通孔的部分区域处朝内凹陷形成至少一条第二沟槽;在所述电感周侧还设置有电连接部,将所述电感通过电连接部电性连接于所述导电连接件,在所述电连接部与所述导电连接件之间部分区域还设置有一导电胶层,使得所述导电胶层不完全覆盖所述第二沟槽。

15.本发明的有益效果在于:在导电连接件内部设置一连通其上表面和下表面的通孔,能够减小在回流焊工艺中导电连接件和基板接触面之间焊接层形成的空洞面积,以及形成的空洞内气体也可通过通孔顺利从导电连接件上表面排出,防止在后期工艺制作中空洞内气体受热膨胀,出现推动导电连接件上移的问题,提高导电连接件与基板之间、电感与基板之间的焊接质量。

附图说明

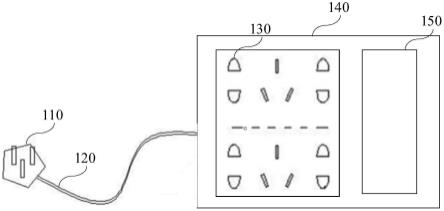

16.图1为本发明一实施方式中的导电连接件的结构示意图。

17.图2为本发明一实施方式中的一种芯片封装结构的制作方法流程示意图。

18.图3~6为本发明一实施方式中的对应芯片封装结构制作方法的工艺步骤图。

具体实施方式

19.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明具体实施方式及相应的附图对本发明技术方案进行清楚、完整地描述。显然,所描述的实施方式仅是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。

20.下面详细描述本发明的实施方式,实施方式的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施方式是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

21.为方便说明,本文使用表示空间相对位置的术语来进行描述,例如“上”、“下”、“后”、“前”等,用来描述附图中所示的一个单元或者特征相对于另一个单元或特征的关系。空间相对位置的术语可以包括设备在使用或工作中除了图中所示方位以外的不同方位。例如,如果将图中的装置翻转,则被描述为位于其他单元或特征“下方”或“上方”的单元将位于其他单元或特征“下方”或“上方”。因此,示例性术语“下方”可以囊括下方和上方这两种空间方位。

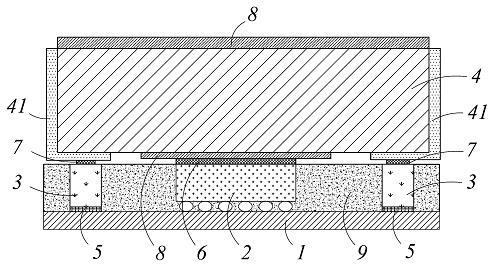

22.如图6所示,本发明一实施方式提供一种芯片封装结构,包括基板1、至少一芯片2、多个导电连接件3和至少一电感4。

23.基板1具有上表面及与上表面相背的下表面。

24.示例性的,在本实施方式中,设置一块芯片2,芯片2设置于基板1上表面,与基板1电性连接,具体的,芯片2具有设置有焊盘的功能面以及与功能面相对的非功能面,芯片2功能面朝向基板1设置,通过焊盘电性连接于基板1。 在本发明其他实施方式中,也可在基板1上表面设置两块或是多块芯片,实现对应于产品的不同要求。

25.导电连接件3设置于基板1上表面,与基板1电性连接。具体的,在导电连接件3通过一焊接层5固定连接于基板1上表面侧。优选的,焊接层5为锡膏层,当然,在本发明其他实施方式中,焊接层5也可以为其他焊接材料,可根据实际封装产品的制作需求选取。

26.具体参见图1,为本实施方式中导电连接件3的结构示意图,导电连接件3内部设置一通孔31,通孔31连通导电连接件3的上表面和下表面,用于减小导电连接件3和基板1接触面之间的焊接层5在回流焊工艺中形成的空洞面积,以及有助于在回流焊或塑封工艺中将形成的空洞内的气体能通过通孔31顺利从导电连接件3上表面排出。具体的,通孔31为一竖直平行于导电连接件3的圆柱形结构,当然,在本发明其他实施方式中,通孔31也可以是倾斜于导电连接件3设置的圆柱形结构,或是其他形状,只需使得该通孔31连通导电连接件3的上表面和下表面,保证后续工艺中导电连接件3下表面形成的空洞内气体能够顺利通过通孔31从导电连接件3上表面排出即可。

27.进一步的,导电连接件3下表面连接通孔31的部分区域朝内凹陷形成至少一条第一沟槽32,第一沟槽32至少将导电连接件3下表面分成两个焊接区域,焊接层5设置于该焊接区域与基板1之间。由于第一沟槽32将导电连接件3下表面设置的焊接层5,即锡膏,分割成了两个区域,进一步减小导电连接件3下表面设置的锡膏在后续工艺中可能形成的空洞面积。当然,导电连接件3下表面形成的第一沟槽32越多,即将导电连接件3下表面分割形成的焊接区域越多,则每个焊接区域面积就越小,每个焊接区域内形成的空洞面积就越小。

28.具体的,在本实施方式中,导电连接件3下表面连接通孔31的部分区域朝内凹陷形

成两条第一沟槽32,两条第一沟槽32相交呈十字型,将导电连接件3下表面分成四个焊接区域,通孔31连接于两条第一沟槽32相交处,四个焊接区域处分别设置有焊接层5,即能有效减小导电连接件3和基板1接触面之间的焊接层5在回流焊工艺中形成的空洞面积。对于第一沟槽32的具体尺寸和形状,本发明在此不作限制,只需不影响导电连接件3本身的导电性能即可。

29.当然,在本发明其他实施方式中,两条第一沟槽32也可不相交,或者两条第一沟槽32倾斜相交,只需保证通孔31靠近基板1一端的开口连接其中一条第一沟槽32,即能达到本发明所需的技术效果,或也可在导电连接件3下表面设置多条相交的第一沟槽32,本发明对此不作限制。

30.更进一步的,导电连接件3上表面连接通孔31的部分区域朝内凹陷形成至少一条第二沟槽33。具体的,在本实施方式中,导电连接件3上表面连接通孔31的部分区域朝内凹陷形成两条第二沟槽33,两条第二沟槽33相交呈十字型,将导电连接件3上表面分成四个区域,通孔31连接于两条第二沟槽33相交处,即该封装结构在后续工艺中导电连接件3下表面形成的空洞内气体受热膨胀后可通过通孔31排出至导电连接件3上表面,再由第二沟槽33排出至外界空气中。

31.继续参见图6,电感4设置于芯片2上方,通过导电连接件3电性连接于基板1。具体的,电感4通过一散热胶层6设置于芯片2上表面,在电感4周侧还设置电连接部41,电感4通过该电连接部41电性连接于导电连接件3,电连接部41与导电连接件3之间还设置一导电胶层7,该导电胶层7不完全覆盖导电连接件3上表面的第二沟槽33,以保证导电连接件3底部形成的空洞内气体能够顺利沿通孔31及第二沟槽33排出。这里,电连接部41可以为电感引脚,也可以是设置于电感4两相对侧边并延伸至其底面的铜结构件,本发明对此不作限制,只需保证其能将电感4与导电连接件3电性连接即可。

32.在本发明具体实施方式中,导电连接件3为铜柱,芯片封装结构中具体包括两个铜柱,分别设置于芯片2两侧。在本发明的其他实施方式中,导电连接件3也可能为其他立体导电结构件,并且,根据电感4的尺寸大小和数量也可以调整导电连接件3的数量及分布位置等,只要使导电连接件3能够对电感起到结构支撑和电传输的作用即可。

33.当然,在电感4与散热胶层6之间、以及在电感4上表面还设置有一层散热片8,加强整体封装结构的散热性能。

34.更具体的,本实施方式中芯片封装结构还包括塑封体9,塑封体9以环氧树脂为基体,添加有固化剂、偶联剂等添加剂,其覆盖基板1、芯片2和导电连接部3,填充其内部空隙,从而对封装结构起到机械支持和密封保护的作用,同时,为保证封装结构的散热性能,塑封体9还需暴露电感4、以及暴露芯片2和导电连接部3的上表面。

35.如图2所示,本发明一实施方式提供一种芯片封装结构的制作方法,包括步骤:s1:提供一基板和至少一芯片,将芯片贴装于基板上表面,并与基板电性连接。

36.s2:提供多个导电连接件,在导电连接件内部形成一通孔,通孔连通导电连接件的上表面和下表面,将所述导电连接件通过焊接层贴装于基板上表面。

37.s3:提供至少一电感,将电感贴装于芯片上方,通过导电连接件与基板电性连接。

38.对应于步骤s1,如图3所示,将芯片2的功能面倒装焊接于基板1上表面,并与基板1电性连接。

39.在步骤s2中,提供多个导电连接件3,在导电连接件3内部形成一通孔31,通孔31连通导电连接件3的上表面和下表面,具体包括:提供多个铜柱,在铜柱内部形成一通孔31,通孔31连通铜柱的上表面和下表面,在本发明具体实施方式中,提供两个铜柱,将其分别贴装于芯片2两侧。

40.进一步的,在导电连接件3,即铜柱的下表面连接通孔31的部分区域处朝内凹陷形成至少一条第一沟槽32,第一沟槽32至少将导电连接件3下表面分成两个焊接区域。具体的,提供的导电连接件3的具体结构可参见图1,在导电连接件3下表面连接通孔31的部分区域朝内凹陷形成两条第一沟槽32,两条第一沟槽32相交呈十字型,将导电连接件3下表面分成四个焊接区域,通孔31连接于两条第一沟槽32相交处。对于第一沟槽32的具体尺寸和形状,本发明在此不作限制,只需不影响导电连接件3本身的导电性能即可。

41.当然,在本发明其他实施方式中,两条第一沟槽32也可不相交,或者两条第一沟槽32倾斜相交,只需保证通孔31靠近基板1一端的开口连接其中一条第一沟槽32,即能达到本发明所需的技术效果,或也可在导电连接件3下表面设置多条相交的第一沟槽32,本发明对此不作限制。

42.更进一步的,在导电连接件3上表面连接通孔31的部分区域处朝内凹陷形成至少一条第二沟槽33。具体的,在本实施方式中,导电连接件3上表面连接通孔31的部分区域朝内凹陷形成两条第二沟槽33,两条第二沟槽33相交呈十字型,将导电连接件3上表面分成四个区域,通孔31连接于两条第二沟槽33相交处。

43.如图4所示,将焊接层5设置于导电连接件3下表面的焊接区域处,并将导电连接件3具有焊接层5的一面朝基板1方向贴装于基板1上表面,具体的,焊接层5为锡膏层。

44.在本实施方式中,在进行步骤s3之前还包括回流焊、塑封等工艺步骤,如图5,为完成塑封工艺之后的封装结构,塑封体9覆盖基板1、芯片2和导电连接件3,并暴露芯片2和导电连接件3上表面。由于导电连接件3下表面的焊接区域涂覆有锡膏层,在回流焊工艺后,该焊接区域表面会形成多个空洞,通孔31和第一沟槽32的设置能够有效减小导电连接件3下表面形成的空洞面积,并且在塑封工艺过程中,形成的空洞内的气体受热膨胀,该气体也可通过通孔31及第二沟槽33排出至外界空气,防止出现导电连接件3上移造成导电连接件3与塑封体9不共面的问题。

45.在步骤s3中,提供至少一电感4,将电感4贴装于芯片2上方,通过导电连接件3与基板1电性连接,具体包括:如图6所示,在电感4周侧还设置有电连接部41,在电感4上表面和下表面设置有散热片8,将电感4通过一散热胶层6贴装于芯片2上表面,同时,将电感4通过电连接部41电性连接于导电连接件3,在电连接部41与导电连接件3之间部分区域还设置有一导电胶层7,使得导电胶层7不完全覆盖第二沟槽33,以保证导电连接件3底部形成的空洞内气体能够顺利沿通孔31及第二沟槽33排出。

46.综上所述,本发明在导电连接件内部设置一连通其上表面和下表面的通孔,能够减小在回流焊工艺中导电连接件和基板接触面之间焊接层形成的空洞面积,以及形成的空洞内气体也可通过通孔顺利从导电连接件上表面排出,防止在后期工艺制作中空洞内气体受热膨胀,出现推动导电连接件上移的问题,提高导电连接件与基板之间、电感与基板之间的焊接质量。

47.应当理解,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施方式中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

48.上文所列出的一系列的详细说明仅仅是针对本发明的可行性实施方式的具体说明,它们并非用以限制本发明的保护范围,凡未脱离本发明技艺精神所作的等效实施方式或变更均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。