1.本发明涉及半导体集成电路布局,特别涉及一种包括相同栅极线间距(gate line pitch)但不同栅极线宽度(gate line width)的不同标准单元所构成的集成电路布局。

背景技术:

2.随着效能提升及多种应用需求,集成电路(ic)的设计日趋复杂,动辄包含数十万甚至上百万个逻辑栅。为了设计上的方便,业界会将集成电路(ic)中常常使用到的特定功能先利用逻辑栅设计好,并且将它们制作成标准单元(standard cell),例如反及栅(nand)、反或栅(nor)、d型正反器(d-flip-flop)、锁存器(latch)、输入输出单元(i/o)、放大器(op amp)、模拟数字转换器(adc)、数字模拟转换器(dac)等,并经过制作工艺验证确定可量产制造后,将标准单元库(standard cell library)授权给芯片设计者使用,利用例如电路模拟(logic simulator)、逻辑电路合成(logic synthesizer)、自动布局与绕线(automatic placer&router)等计算机辅助设计(computer-aided design,cad)工具将这些标准单元排列组合出需要的电路功能,由此可在短时间内就正确建构出复杂庞大的集成电路系统。

3.为了提供较大的设计弹性,标准单元库(standard cell library)通常会包含不同速度或功率的不同级(或不同栅极尺寸)的标准单元供芯片设计者混合使用。然而,若这些标准单元的尺寸设计不良,组合后容易产生闲置的布局区域造成空间浪费,也会导致混合使用时的布局与绕线复杂度提高而降低了自动化布局效率。此外,在设计定案(tape out)后的布局修正阶段,也会对布局修正例如光学邻近修正(optical proximity correction,opc)造成负担且容易产生错误图案。

技术实现要素:

4.本发明的目的在于提供一种集成电路布局及其设计方法,其中集成电路布局包括相同栅极线间距(gate line pitch)但不同栅极线宽度(gate line width)的不同标准单元。

5.为达上述目的,本发明提供了一种集成电路布局,包括第一标准单元和第二标准单元。第一标准单元包括多个第一栅极线沿着一第一方向排列在该第一标准单元的两第一单元边界之间,其中该第一栅极线包括一第一栅极线宽度并且相距一预设栅极线间距(default gate line pitch)。第二标准单元沿着一第二方向邻接在该第一标准单元的一侧并且包括多个第二栅极线沿着该第一方向排列在该第二标准单元的两第二单元边界之间,其中该第二栅极线包括一第二栅极线宽度并且相距该预设栅极线间距,该第一栅极线宽度不同于该第二栅极线宽度,该两第一单元边界之间的一第一单元宽度以及该两第二单元边界之间的一第二单元宽度分别为该预设栅极线间距的整数倍,以及至少部分该第二栅极线与至少部分该第一栅极线沿着该第二方向对齐,该第一方向与该第二方向互相垂直。

附图说明

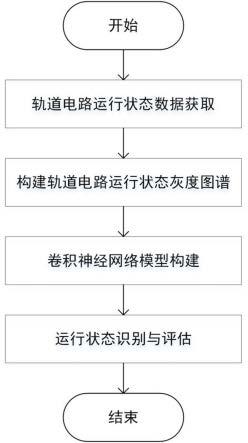

6.图1为本发明一实施例的集成电路的布局设计方法的步骤流程图;

7.图2至图4为本发明一些实施例的标准单元的布局平面图;

8.图5至图8为本发明一些实施例的集成电路布局的平面图。

9.主要元件符号说明

10.10 设计方法

11.12 步骤

12.14 步骤

13.16 步骤

14.18 步骤

15.102 栅极线

16.104 单元边界

17.106 单元边界

18.108 主动(有源)区图案

19.202 栅极线

20.204 单元边界

21.206 单元边界

22.208 主动区图案

23.302 栅极线

24.304 单元边界

25.306 单元边界

26.308 主动区图案

27.400 虚设栅极线

28.500 集成电路布局

29.600 集成电路布局

30.700 集成电路布局

31.800 集成电路布局

32.102a 中心线

33.108a 主动区图案宽度

34.108b 主动区图案间距

35.202a 中心线

36.208a 主动区图案宽度

37.208b 主动区图案间距

38.302a 中心线

39.308a 主动区图案宽度

40.308b 主动区图案间距

41.400a 虚设栅极线半部

42.400b 虚设栅极线半部

43.cell-a1 标准单元

44.cell-a2 标准单元

45.cell-b1 标准单元

46.cell-b2 标准单元

47.cell-c1 标准单元

48.cell-c2 标准单元

49.la 栅极线宽度

50.lb 栅极线宽度

51.lc 栅极线宽度

52.p 预设栅极线间距

53.sa1 栅极线间隔

54.sa2 虚设栅极线间隔

55.sa3 虚设栅极线间隔

56.sb1 栅极线间隔

57.sb2 虚设栅极线间隔

58.sb3 虚设栅极线间隔

59.sc1 栅极线间隔

60.sc2 虚设栅极线间隔

61.sc3 虚设栅极线间隔

62.wa虚设栅极线半部宽度

63.wb 虚设栅极线半部宽度

64.wa1 单元宽度

65.wa2 单元宽度

66.wb1 单元宽度

67.wb2 单元宽度

68.wc1 单元宽度

69.wc2 单元宽度

具体实施方式

70.为使熟悉本发明所属技术领域的一般技术者能更进一步了解本发明,下文特列举本发明的数个优选实施例,并配合所附的附图,详细说明本发明的构成内容及所欲达成的功效。在不悖离本发明的范围内,可做结构、逻辑和电性上的修改,而应用在其他实施例上。本发明的各附图只是示意图,其详细的比例可在不悖离本发明的情况下依照设计的需求进行调整。

71.图1所绘示为根据本发明一实施例的集成电路的布局设计方法10的步骤流程图。本领域技术人员应可了解设计方法10可通过任何种类的计算机系统来执行,例如个人计算机、携带式计算机、工作站、计算机终端、网络计算机,或者任何一种数据处理系统或设备。如图1所示,本发明提供的集成电路布局的设计方法10包括首先进行步骤12,设定一预设栅极线间距(default gate line pitch)p、一预设栅极线宽度(default gate line width)l,以及一变量(例如第一变量d1)。接着进行步骤14,根据该预设栅极线间距及该预设栅极

线宽度产生一组(多个)第一栅极线位于两第一单元边界之间,以及根据该预设栅极线间距及该预设栅极线宽度加上该变量(例如第一变量d1)产生一组(多个)第二栅极线位于两第二单元边界之间。接着进行步骤16,在该两第一单元边界以及该两第二单元边界上设置虚设栅极线(dummy gate lines),从而获得第一标准单元和第二标准单元。

72.根据本发明一实施例,可于步骤12中设定一另一变量(例如第二变量d2),并于步骤14时根据该预设栅极线间距及该预设栅极线宽度加上该另一变量(例如第二变量d2)产生一组(多个)第三栅极线位于两第三单元边界之间,然后进行步骤16于该两第三单元边界上设置该虚设栅极线(dummy gate lines),获得第三标准单元。应理解,可依照设计需求设定更多组变量来产生更多个标准单元,为了简化说明,本文不进一步详述。

73.请参考图2、图3和图4,所绘示为通过图1的设计方法10所获得的一些示例性标准单元(standard cell)的布局平面图。需特别说明的是,各图上部和下部示出的标准单元包括相同的栅极线间距(例如预设栅极线间距p)和栅极线宽度,主要差异在于电路连线设计不同以提供不同功能,而各图之间的标准单元则包括相同的电路设计、相同的栅极线间距(例如预设栅极线间距p)但不同的栅极线宽度,例如栅极线宽度分别等于预设栅极线宽度l、预设栅极线宽度l加上第一变量d1、预设栅极线宽度l加上第二变量d2,以提供相同功能但不同速度或功率。需特别说明的是,图2、图3和图4所绘示的标准单元的电路设计仅为举例,且示出的栅极线、主动区图案的数量以便于绘图及说明为目的,并不用于限制本发明。本发明的概念可应用于任何包括多条栅极线的标准单元。

74.详细来说,如图2所示,标准单元cell-a1和标准单元cell-a2分别包括一对沿着第二方向d2延伸且互相平行的单元边界104、另一对沿着第一方向d1延伸且互相平行的单元边界106,其中第一方向d1和第二方向d2互相垂直、多个主动区图案108沿着第一方向d1延伸并沿着第二方向d2排列、多个栅极线102沿着第二方向d2延伸并且沿着第一方向d1排列在单元边界104之间,以及两个虚设栅极线400分别与单元边界104重叠,其中虚设栅极线400的边缘与邻近的栅极线102的边缘之间分别包括虚设栅极线间隔sa2和虚设栅极线间隔sa3。根据本发明一实施例,如图2所示,主动区图案108的端部与栅极线102或虚设栅极线400重叠,并未显露出来。标准单元cell-a1和标准单元cell-a2的栅极线102具有栅极线宽度la且彼此相距预设栅极线间距p,其中一预设栅极线间距p等于一栅极线宽度la加上相邻栅极线102边缘之间的一栅极线间隔(gate line space)sa1之和。标准单元cell-a1和标准单元cell-a2的主动区图案108均包括主动区图案宽度108a并且相距主动区图案间距108b。值得注意的是,标准单元cell-a1和标准单元cell-a2的单元边界104之间的单元宽度wa1和wa2分别是预设栅极线间距p的整数倍,且其各自的栅极线102是以均分单元宽度wa1和wa2的方式排列在单元边界104之间。换言之,沿着标准单元cell-a1和标准单元cell-a2的各栅极线102的中心线102a可将标准单元cell-a1和标准单元cell-a2区分成宽度相同的部分。也值得注意的是,单元边界104大致上通过虚设栅极线400的中心线而将虚设栅极线400区分成宽度相同的两个虚设栅极线半部400a和虚设栅极线半部400b,分别包括虚设栅极线半部宽度wa和虚设栅极线半部宽度wb,且wa和wb相等。由以上说明可知,虚设栅极线间隔sa2和虚设栅极线间隔sa3也会相等,且两单元边界104与邻近的栅极线102等距。

75.如图3所示,标准单元cell-b1和标准单元cell-b2分别包括一对沿着第二方向d2延伸且互相平行的单元边界204、另一对沿着第一方向d1延伸且互相平行的单元边界206、

多个主动区图案208沿着第一方向d1延伸并沿着第二方向d2排列、多个栅极线202沿着第二方向d2延伸并且沿着第一方向d1排列在单元边界204之间。根据本发明一实施例,图3的标准单元cell-b1和标准单元cell-b2与图2的标准单元cell-a1和标准单元cell-a2包括相同的两个虚设栅极线400,其中虚设栅极线40与单元边界204重叠,且虚设栅极线400的边缘与邻近之栅极线202的边缘之间分别包括虚设栅极线间隔sb2和虚设栅极线间隔sb3。类似的,主动区图案208的端部与栅极线202或虚设栅极线400重叠,并未显露出来。标准单元cell-b1和标准单元cell-b2的栅极线202具有栅极线宽度lb且彼此相距预设栅极线间距p,其中栅极线宽度lb不同于栅极线宽度la,但预设栅极线间距p同样等于栅极线宽度lb加上相邻栅极线202边缘之间的栅极线间隔sb1之和。标准单元cell-b1和标准单元cell-b2的主动区图案208均包括主动区图案宽度208a并且相距主动区图案间距208b。根据本发明一实施例,主动区图案宽度208a和主动区图案宽度108a相等,主动区图案间距208b和主动区图案间距108b相等。值得注意的是,标准单元cell-b1和标准单元cell-b2的单元边界204之间的单元宽度wb1和wb2也分别是预设栅极线间距p的整数倍,且其各自的栅极线202是以均分单元宽度wb1和wb2的方式排列在单元边界204之间。换言之,沿着标准单元cell-b1和标准单元cell-b2的各栅极线202的中心线202a可将标准单元cell-b1和标准单元cell-b2区分成宽度相同的部分。单元边界204大致上通过虚设栅极线400的中心线而将虚设栅极线400区分成宽度相同的两个虚设栅极线半部400a和虚设栅极线半部400b,分别包括虚设栅极线半部宽度wa和虚设栅极线半部宽度wb,且wa和wb相等。由以上说明可知,虚设栅极线间隔sb2和虚设栅极线间隔sb3也会相等,且两单元边界204与邻近的栅极线202等距。

76.如图4所示,标准单元cell-c1和标准单元cell-c2分别包括一对沿着第二方向d2延伸且互相平行的单元边界304、另一对沿着第一方向d1延伸且互相平行的单元边界306、多个主动区图案308沿着第一方向d1延伸并沿着第二方向d2排列、多个栅极线302沿着第二方向d2延伸并且沿着第一方向d1排列在单元边界304之间。根据本发明一实施例,图4的标准单元cell-c1和标准单元cell-c2与图2的标准单元cell-a1和标准单元cell-a2和图3的标准单元cell-b1和标准单元cell-b2包括相同的两个虚设栅极线400,其中虚设栅极线400分别与单元边界304重叠,且虚设栅极线400的边缘与邻近的栅极线302的边缘之间分别包括虚设栅极线间隔sc2和虚设栅极线间隔sc3。类似的,主动区图案308的端部与栅极线302或虚设栅极线400重叠,并未显露出来。标准单元cell-c1和标准单元cell-c2的栅极线302具有栅极线宽度lc且彼此相距预设栅极线间距p,其中栅极线宽度lc不同于栅极线宽度la和栅极线宽度lb,但预设栅极线间距p同样等于栅极线宽度lc加上相邻栅极线302边缘之间的栅极线间隔sc1之和。标准单元cell-c1和标准单元cell-c2的主动区图案308均包括主动区图案宽度308a并且相距主动区图案间距308b。根据本发明一实施例,主动区图案宽度308a和主动区图案宽度208a及主动区图案宽度108a相等,主动区图案间距308b和主动区图案间距208b及主动区图案间距108b相等。值得注意的是,标准单元cell-c1和标准单元cell-c2的单元边界304之间的单元宽度wc1和wc2也分别是预设栅极线间距p的整数倍,且其各自的栅极线302是以均分单元宽度wc1和wc2的方式排列在单元边界304之间。换言之,沿着标准单元cell-c1和标准单元cell-c2的各栅极线302的中心线302a可将标准单元cell-c1和标准单元cell-c2区分成宽度相同的部分。单元边界304大致上通过虚设栅极线400的中心线而将虚设栅极线400区分成宽度相同的两个虚设栅极线半部400a和虚设栅极

线半部400b,分别包括虚设栅极线半部宽度wa和虚设栅极线半部宽度wb,且wa和wb相等。由以上说明可知,虚设栅极线间隔sc2和虚设栅极线间隔sc3也会相等,且两单元边界304与邻近的栅极线302等距。

77.根据本发明一实施例,栅极线宽度lc可等于预设栅极线宽度l,栅极线宽度la等于预设栅极线宽度l加上第一变量d1,栅极线宽度lb等于预设栅极线宽度l加上第二变量d2。

78.虚设栅极线400的宽度(即wa与wb之和)可等于预设栅极线宽度l、栅极线宽度lc、栅极线宽度lb和栅极线宽度lc的其中一者。举例来说,虚设栅极线400的宽度可等于预设栅极线宽度l加上第一变量d1,即等于栅极线宽度la。

79.根据本发明一实施例,进行设计方法10的步骤12时,设定的预设栅极线宽度l可为集成电路设计规范(design rule)的最小栅极线宽度(minimum gate line width),预设栅极线间距p为预设栅极线宽度l为最小栅极线宽度时制作工艺解析度可达的最小栅极线间距。例如,根据本发明一实施例,可设定步骤12的预设栅极线宽度l为16nm,预设栅极线间距p为96nm,第一变量d1为4nm,第二变量d2为8nm,则步骤14和步骤16获得的标准单元cell-a1、标准单元cell-a2、标准单元cell-b1、标准单元cell-b2、标准单元cell-c1、标准单元cell-c2可具有如〈表格一〉所示的特征尺寸。

80.表格一

[0081][0082][0083]

以上具体的尺寸以帮助理解本发明为目的,并不用于限制本发明。在其他实施例中,可根据实际设计需求调整预设栅极线宽度l、预设栅极线间距p、第一变量d1,以及第二变量d2的数值。

[0084]

值得注意的是,本发明的标准单元虽具有不同栅极线宽度,但都是以栅极线(栅极线的中心线)将标准单元区分成宽度相同的部分的方式将栅极线排列在单元边界之间,因此任两个标准单元的栅极线间隔会相差栅极线宽度的变量。此外,由于本发明的标准单元包括相同的虚设栅极线,因此任两个标准单元的虚设栅极线间隔会相差栅极线宽度的变量的0.5倍。根据本发明一实施例,预设栅极线宽度l、预设栅极线间距p、第一变量d1,以及第二变量d2的数值均为偶数,以能够获得全栅上(all on-grid)的布局图案。

[0085]

举例来说,参考表格一,标准单元cell-c1的栅极线宽度lc和标准单元cell-a1的

栅极线宽度la相差的第一变量d1为4nm,虚设栅极线间隔sc2为78nm,虚设栅极线间隔sa2为76nm,两者相差2nm。

[0086]

再举例来说,标准单元cell-c1的栅极线宽度lc和标准单元cell-b1的栅极线宽度lb相差的第二变量d2为8nm,虚设栅极线间隔sc2为78nm,虚设栅极线间隔sb2为74nm,两者相差4nm。

[0087]

请回到图1。获得第一标准单元与第二标准单元之后,接着进行步骤18,邻接该第一标准单元与该第二标准单元,获得一集成电路布局。根据本发明一实施例,步骤18可选择邻接第一标准单元、第二标准单元、第三标准单元的其中至少两者来获得集成电路布局。

[0088]

如前所述,本发明提供的标准单元的设计包括至少以下特征。第一,不同的标准单元包括相同的预设栅极线间距。第二,不同的标准单元的单元宽度均是预设栅极线间距的整数倍。第三,各标准单元栅极线以均分单元宽度的方式等距排列在标准单元的单元边界之间。第四,不同的标准单元包括相同的虚设栅极线,且单元边界通过虚设栅极线的中心线。

[0089]

通过上述标准单元的设计,本发明提供的集成电路布局可包括至少以下特征。首先,沿着第一方向d1相邻的标准单元的单元边界互相重叠时,虚设栅极线可完全重叠。此外,沿着第二方向d1相邻的标准单元的栅极线、虚设栅极线、单元边界沿着第二方向d1互相对齐。再者,当标准单元包括相同的主动区图案宽度和相同的主动区图案间距时,沿着第一方向d1相邻的标准单元的主动区图案可沿着第一方向d1互相对齐。为了便于理解,下文将分别根据图5、图6、图7和图8的实施例来说明本发明的集成电路布局的特征。

[0090]

请参考图5,所绘示为根据本发明一实施例的集成电路布局500的平面图。集成电路布局500包括沿着第一方向d1和第二方向d2混合排列的标准单元cell-c1和标准单元cell-b1,其中沿着第一方向d1相邻的标准单元cell-c1和标准单元cell-b1的单元边界304和单元边界204互相重叠,并且共用一虚设栅极线400。沿着第二方向d2相邻的标准单元cell-c1和标准单元cell-b1的单元边界306和单元边界206互相重叠。标准单元cell-c1包括多个栅极线302沿着第一方向d1排列在标准单元cell-c1的两单元边界304之间,相距一预设栅极线间距p,并且包括栅极线宽度lc(参考图4)。标准单元cell-b1包括多个栅极线202沿着第一方向d1排列在标准单元cell-b1的两单元边界204之间,相距预设栅极线间距p,并且包括栅极线宽度lb(参考图3)。栅极线宽度lc不同于栅极线宽度lb,相差一变量(例如第二变量d2)。标准单元cell-c1的单元边界304之间包括单元宽度wc1,标准单元cell-b1的单元边界204之间包括单元宽度wb1,其中单元宽度wc1可等于单元宽度wb1,并且是预设栅极线间距p的整数倍,因此沿着第二方向d2来看,栅极线302和栅极线202对齐,单元边界204和单元边界304对齐,虚设栅极线400和虚设栅极线400对齐。

[0091]

请参考图6,所绘示为根据本发明一实施例的集成电路布局600的平面图。集成电路布局600包括沿着第一方向d1和第二方向d2混合排列的标准单元cell-c1和标准单元cell-b2,其中沿着第一方向d1相邻的标准单元cell-c1和标准单元cell-b2的单元边界304和单元边界204互相重叠,并且共用一虚设栅极线400。沿着第二方向d2相邻的标准单元cell-c1和标准单元cell-b2的单元边界306和单元边界206互相重叠。标准单元cell-c1包括多个栅极线302沿着第一方向d1排列在标准单元cell-c1的两单元边界304之间,相距一预设栅极线间距p,并且包括栅极线宽度lc(参考图4)。标准单元cell-b2包括多个栅极线

202沿着第一方向d1排列在标准单元cell-b2的两单元边界204之间,相距预设栅极线间距p,并且包括栅极线宽度lb(参考图3)。栅极线宽度lc不同于栅极线宽度lb,相差一变量(例如第二变量d2)。标准单元cell-c1的单元边界304之间包括单元宽度wc1,标准单元cell-b2的单元边界204之间包括单元宽度wb2,其中单元宽度wc1不等于单元宽度wb2,并且分别是预设栅极线间距p的整数倍。由于单元宽度wc1不等于单元宽度wb2,因此集成电路布局600的单元边界204和304可沿着第二方向d2交错,栅极线202与部分栅极线302可沿着第二方向d2对齐,单元边界204与一栅极线302或一单元边界304可沿着第二方向d2对齐,部分虚设栅极线400与栅极线202及/或栅极线302可沿着第二方向d2对齐。

[0092]

请参考图7,所绘示为根据本发明一实施例的集成电路布局700的平面图。图7与图5主要差异在于,图7的集成电路布局700包括三种具有相同单元宽度、相同栅极线间距(例如预设栅极线间距p),但不同栅极线宽度的标准单元。例如图7所示,集成电路布局700可包括标准单元cell-c1、标准单元cell-b1,以及标准单元cell-a1。沿着第二方向d2来看,单元边界304、单元边界204、单元边界104会互相对齐,栅极线302、栅极线202、栅极线102会互相对齐,虚设栅极线400也会互相对齐。

[0093]

请参考图8,所绘示为根据本发明一实施例的集成电路布局800的平面图。图8与图7主要差异在于,图8的集成电路布局800包括三种具有相同栅极线间距(例如预设栅极线间距p),但不同栅极线宽度的标准单元,且其中的至少两种标准单元包括不同单元宽度。例如图8所示,集成电路布局800可包括标准单元cell-c1、标准单元cell-b2,以及标准单元cell-a1,其中标准单元cell-b2的单元宽度wb2不同于标准单元cell-c1的单元宽度wc1以及标准单元cell-a1的单元宽度wa1。因此,集成电路布局800的单元边界304、204、104可沿着第二方向d2交错,部分栅极线302与部分栅极线202可沿着第二方向d2对齐,部分栅极线102与部分栅极线202可沿着第二方向d2对齐,单元边界204与一栅极线302或一单元边界304可沿着第二方向d2对齐,部分虚设栅极线400与栅极线202、栅极线302,及/或栅极线302可沿着第二方向d2对齐。

[0094]

后续,可对集成电路布局进行布局修正,例如光学邻近修正(opc),然后将修正后的集成电路布局自计算机系统输出至一套光掩模中,用于在一半导体晶片上制作集成电路结构。举例来说,栅极线102、202、302用来在半导体基底上形成栅极结构,例如多晶硅栅极(polysilicon gate)或金属栅极(metal gate)结构。主动区图案108、208、308用来在半导体基底上形成主动区,例如鳍式(fin-type)主动区。虚设栅极线400用来在半导体基底上形成虚设栅极,例如与多晶硅栅极同时制作的多晶硅虚设栅极,或与金属栅极同时制作的金属虚设栅极。应理解,本发明的提供的标准单元及集成电路布局还可包括其他图案,例如接触插塞、虚设主动趋图案、离子植入图案等,为了简化说明并未绘示于图中。

[0095]

综合以上,本发明提供的各种标准单元包括相同栅极线间距(gate line pitch)但不同栅极线宽度(gate line width),其中各标准单元的单元宽度为栅极线间距的整数倍,且栅极线以均分单元宽度的方式沿着列(row)方向(即第一方向d1)等距排列在标准单元的单元边界之间,当沿着列(row)方向(即第一方向d1)和行(column)方向(即第二方向d2)混合排列这些标准单元来构建集成电路布局时,可使这些标准单元的栅极线和虚设栅极线沿着(column)方向也可对齐排列。另外,本发明使单元边界通过虚设栅极线的中心线,使沿着列(row)方向排列的标准单元不需任何尺寸或图案的调整,可在维持标准单元原设

计尺寸的情况下共用虚设栅极线,避免相邻标准单元之间产生闲置布局区域,提高空间利用率。整体而言,本发明的集成电路布局可具有较整齐且可预测的布局结果,不仅可减轻自动化布局的负担,也可缩短设计定案(tape out)后的布局修正例如光学邻近修正(opc)所耗费的时间。此外,投片制造时,本发明较整齐的图案也有利于制作工艺控制以于晶片上获得理想的布局图案。

[0096]

以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。