1.本公开涉及神经网络领域,尤其涉及一种指令处理装置、加速单元和服务器。

背景技术:

2.神经网络(nns)是近十年来再度兴起的最受人瞩目的技术之一,在语音、图像、大数据、生物医药科技等领域取得了许多突破性进展并产生了大量的落地应用。但同时,业界也越来越关注如何提高神经网络模型的执行效率,主要包括两方面措施:软件方面,通过神经网络模型的算法优化来实现性能提升;硬件方面,通过设计各种用于神经网络模型执行的硬件加速单元来实现性能提升。但无论何种硬件加速单元,如何设计好指令集架构至关重要。

技术实现要素:

3.本公开的目的是提供一种指令处理装置和加速单元,在该指令处理装置中使用一种新构思的指令集架构以专用于神经网络模型的加速单元。

4.本公开实施例提供一种指令处理装置,包括:多个指令缓存器、寄存器文件、选择器、解析器、操作单元,所述寄存器文件包括多个条目,

5.所述选择器用于从接收到的命令中解析出命令类型和缓冲器标识,如果所述命令类型为配置,将接收到的数据和所述缓冲器标识提供给所述解析器,如果所述命令类型为执行,则将所述缓冲器标识提供给所述操作单元;

6.所述解析器用于从所述数据中解析出指令序列,将所述指令序列存储到与所述缓存器标识匹配的指令缓存器中,以及将所述指令序列的每条指令的操作数存储在所述寄存器文件的多个条目中;

7.所述操作单元用于驱动与所述缓存器标识匹配的指令缓存器逐一执行其中的每条指令,以产生控制信号,每条指令的控制信号以及所述寄存器文件中该指令的操作数被发送给多个执行单元,每个执行单元基于接收到的控制信号和操作数执行相应操作。

8.可选地,所述解析器根据所述指令序列中每条指令的原始操作数确定该指令在每个执行单元上执行时的操作数。

9.可选地,所述多个指令处理装置还包括:标量计算单元,用于计算特定指令的操作数,并用新的操作数更新所述寄存器文件该特定指令的操作数。

10.可选地,所述指令处理装置支持多个预定义指令,所述指令序列由所述多个预定义指令中的一个或几个组成。

11.可选地,所述多个预定义指令包括数据加载指令,每个执行单元根据所述数据加载指令的控制信号获取第一向量和第二向量并存储到第一队列和第一缓冲器中。

12.可选地,所述多个预定义指令包括乘法累加指令,每个执行单元根据所述乘法累加指令的控制信号从所述第一队列和第二缓冲器中输出两个数值,以执行相乘后累加运算。

13.可选地,所述寄存器文件的相应条目中还存储有标量流水线状态,所述标量流水线状态用于指定所述第一队列的属性,所述第一队列的属性为以下中的一种:先进先出队列、旋转队列和滑窗队列。

14.可选地,所述多个预定义指令包括数据存储指令,每个执行单元根据所述数据存储指令的控制信号将所述执行单元产生的中间计算结果存储到外部存储器中。

15.可选地,所述多个预定义指令包括特殊功能指令,每个执行单元根据所述特殊功能指令的控制信号启动相应的特殊功能单元。

16.可选地,所述指令序列来自于指定神经网络应用,所述操作单元对不同的神经网络应用使用不同的指令流水线。

17.可选地,所述指定神经网络应用为以下应用中的一种:矩阵乘法、卷积和深度卷积。

18.可选地,所述操作单元在处理矩阵乘法的指令序列时,使用译码级和取数级两级指令流水线;在处理卷积或深度卷积时,使用译码级、取数级、标量处理级和写回级四级指令流水线。

19.第二方面,提供一种集群,包括上述任一项所述的指令处理装置以及与所述指令处理装置耦接的多个执行单元,所述集群接收命令以及与所述命令一并发送的数据。

20.第三方面,提供一种用于神经网络模型执行的加速单元,包括:

21.直接内存访问模块;

22.片上内存,包括多个存储单元;

23.多个集群组,包括多个集群,每个集群包括如权利要求1至12任一项所述的指令处理装置以及与所述指令处理装置耦接的执行单元;

24.命令处理器,用于将指定神经网络应用表征的操作分解成多次执行的子操作,将所述子操作转换为在所述集群上执行的指令序列,并指定每个指令序列的操作数据,通过所述直接内存访问模块分多次加载所述子操作的操作数据,将每个集群组内包含的多个集群分别对应的指令序列和操作数据存储到相应存储单元中;

25.多个分发单元,与所述多个存储单元分别耦接,同时分别与所述多个多个集群组耦接,每个分发单元从与其耦接的存储单元中读取指令序列和操作数据,并将指令序列和操作数分别发送给与其耦接的多个指令处理装置。

26.第四方面,提供一种服务器,包括:

27.上述的加速单元;

28.处理单元,用于向所述加速单元发送指示,以驱动所述加速单元执行所述指定神经网络应用;

29.存储器,用于存储所述指定神经网络应用的权重数据和激活数据。

30.本公开实施例提供的指令处理装置,本质上是一种用于处理神经网络应用的指令集架构,可用于构建各种神经网络模型的加速单元,以提升神经网络模型的硬件加速能力。

附图说明

31.通过参考以下附图对本公开实施例的描述,本公开的上述以及其它目的、特征和优点将更为清楚,在附图中:

32.图1是数据中心的层级结构图;

33.图2是数据中心的立体结构图;

34.图3是数据中心的一个通用结构的云服务器的结构示意图;

35.图4是图3中的云服务器的更具体的结构示意图;

36.图5a是一个示例性的pe集群的设计图;

37.图5b是另一个示例性的pe集群的设计图;

38.图5c是图5a和图5b中的集群控制单元的示意结构图;

39.图6a示出矩阵乘法的示意图;

40.图6b和图6c是卷积和深度卷积的示意图;

41.图7a至图7c是三段伪代码;

42.图8是示例性的二维矩阵乘法的示意图;

43.图9a-图9i用于示出将图8所示的矩阵乘法部署到pe阵列的9种选择。

具体实施方式

44.以下基于实施例对本公开进行描述,但是本公开并不仅仅限于这些实施例。在下文对本公开的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本公开。为了避免混淆本公开的实质,公知的方法、过程、流程没有详细叙述。另外附图不一定是按比例绘制的。

45.在本文中使用以下术语。

46.加速单元:针对通用处理器在一些专门用途的领域(例如,处理图像、处理神经网络的各种运算,等等)效率不高的情况,为了提高在这些专门用途领域中的数据处理速度而设计的处理单元,它往往与通用处理器cpu配套使用,接受通用处理器的控制,执行一些特定用途或特定领域的处理,提高在特定用途或特定领域中的计算机处理效率。也可称为ai处理单元,并可包括图形处理单元(gpu)、中央处理器(cpu)、专用集成电路(asic)、现场可编程门阵列(fpga)、专用集成电路 (asic)、以及专用ai加速硬件(例如加速单元)。

47.片上内存:在主核或副核内单独使用,不能被共享的存储器。

48.命令处理器:在加速单元和驱动该加速单元工作的中央处理单元之间的命令接口。命令处理器接收中央处理单元让加速单元执行的指令,将这些指令分给加速单元中的各个部件去执行。另外,它还负责加速单元中各个部件的同步。

49.生命周期:操作数在指令序列中并不是在全部过程中都会涉及到,在指令序列中其第一次出现和最后一次用到的指令之间的部分,就是该操作数的生命周期。也就是说,过了该生命周期后,它就不再使用,没有必要留在片上内存中。

50.神经网络:一般指人工神经网络(artificial neural network,简写为ann),它是一种模仿动物神经网络行为特征,进行分布式并行信息处理的算法网络。一个经典的神经网络,也是最简单的神经网络结构,包含三个层次:输入层、输出层和中间层(又称隐藏层)。输入层、输出层和中间层又各自包括多个节点。

51.神经网络模型:在神经网络中,将节点数学化,产生节点的数学模型,神经网络中的大量的节点的数学模型构成了神经网络模型。

52.深度学习模型:深度学习的概念源于神经网络的研究,将含有多个中间层的神经

网络称为深度学习网络。因此,从这个意义上将,深度学习模型也是一种神经网络模型。深度学习模型和神经网络模型都必须经由训练产生。将样本数据输入到设计好的网络结构中,经由多个中间层提取特征信息,并基于输出层的输出结果不断地修正各个节点的权重数据,使输出层的输出结果愈来愈趋向于预设结果,直至确定最终的权重数据。训练好的深度学习模型可以真正地应用于实际场景中,同时还可以收集深度学习模型在实际场景中的使用情况,反过来优化深度学习模型。

53.节点:深度学习模型中独立运算的最小单位,其接收输入,经本身的权重参数或其它模型中参数(例如超参)运算后,产生输出。深度学习模型可以包括卷积、池化等各种具体操作,进而包括卷积节点、池化节点等各种操作节点。深度学习模型中有多个层,每个层有多个节点,每个节点的输出是下一层的节点的输入。进一步地,节点包括具体操作的程序及相关数据。例如,卷积操作节点中包括卷积操作用到的程序代码和卷积中用到的一些数据。

54.算子:是指在深度学习模型中构建的用于实现特定功能的一系列操作的集合。深度学习模型的每一层都可包含多个这样的算子。可以在tensorflow框架中被称为 operation,在caffe框架中被称为layer。算子看作在节点基础上的进一步实现,一个算子可对应一个或多个节点,因此,算子和节点有时对应的程序和数据相同。

55.指令集(指令集架构):芯片内部支持的进行运算的指令的集合,例如主要支持深度学习算子的运算,如:convolution,pooling,roi等。

56.数据中心

57.图1示出作为本公开实施例所应用的一种场景的数据中心的分层结构图。

58.数据中心是全球协作的特定设备网络,用来在互联网网络基础设施上传递、加速、展示、计算、存储数据信息。在今后的发展中,数据中心也将会成为企业竞争的资产。随着数据中心应用的广泛化,人工智能等越来越多地应用到数据中心。而神经网络作为人工智能的重要技术,已经大量应用到数据中心大数据分析运算中。

59.在传统的大型数据中心,网络结构通常是图1所示的三层结构,即分级的互连网络模型(hierarchical inter-networking model)。这个模型包含了以下三层:

60.接入层(access layer)103:有时也称为边缘层,包括接入交换机130和接入交换机所连接的各服务器140。各服务器140是数据中心的处理和存储实体,数据中心中大量数据的处理和存储都是由这些服务器140完成的。接入交换机130是用来让这些服务器接入到数据中心中的交换机。一台接入交换机130接入多台服务器 140。接入交换机130通常位于机架顶部,所以它们也被称为机顶(top of rack) 交换机,它们物理连接服务器。

61.汇聚层(aggregation layer)102:有时候也称为分发层,包括汇聚交换机120。每台汇聚交换机120连接多台接入交换机,同时提供其他的服务,例如防火墙,入侵检测,网络分析等。

62.核心层(core layer)101:包括核心交换机110。核心交换机110为进出数据中心的包提供高速的转发,为多个汇聚层提供连接性。整个数据中心的网络分为l3 层路由网络和l2层路由网络,核心交换机110为通常为整个数据中心的网络提供一个弹性的l3层路由网络。

63.通常情况下,汇聚交换机120是l2和l3层路由网络的分界点,汇聚交换机120 以下的是l2网络,以上是l3网络。每组汇聚交换机管理一个传送点(pod,point ofdelivery),

每个pod内都是独立的vlan网络。服务器在pod内迁移不必修改ip 地址和默认网关,因为一个pod对应一个l2广播域。

64.交换机120和接入交换机130之间通常使用生成树协议(stp,spanning treeprotocol)。stp使得对于一个vlan网络只有一个汇聚层交换机120可用,其他的汇聚层交换机120在出现故障时才被使用(上图中的虚线)。也就是说,在汇聚层,做不到水平扩展,因为就算加入多个汇聚交换机120,仍然只有一个在工作。

65.图2示出了图1的分层的数据中心中各部件的物理连接。如图2所示,一个核心交换机110连接多个汇聚交换机120,一个汇聚交换机120连接多个接入交换机 130,一个接入交换机130接入多个服务器140。

66.云服务器

67.云服务器140才是数据中心真实的设备。由于云服务器140高速运转以执行诸如矩阵计算、图像处理、机器学习、压缩、搜索排序等各种任务,因此,为了能够高效完成上述各种任务,云服务器140通常包括中央处理器(cpu)和各种加速单元,如图3所示。加速单元例如专用于神经网络的加速单元、数据传输单元(dtu)、图形处理单元(gpu)、专用集成电路(asic)、现场可编程门阵列(fpga)中的一个。以下图3所示为例对各个加速单元分别进行介绍。

68.数据传输单元(dtu)260:它是专门用于将串口数据转换为ip数据或将ip数据转换为串口数据通过无线通信网络进行传送的无线终端设备。dtu的主要功能是把远端设备的数据通过无线的方式传送回后台中心。在前端,dtu和客户的设备通过接口相连。dtu上电运行后先注册到移动的gprs网络,然后去和设置在dtu中的后台中心建立套接字连接。后台中心作为套接字连接的服务端,dtu是套接字连接的客户端。因此dtu和后台软件配合一起使用,在建立连接后,前端的设备和后台的中心就可以通过dtu进行无线数据传输。

69.图形处理单元(gpu)240:是专门做图像和图形相关运算工作的处理器。使用 gpu,克服了cpu中计算单元的空间过少的缺点,采用大量用于专门做图形计算的计算单元,使显卡减少了对cpu的依赖,承担了cpu原来承担的一些计算密集的图像处理工作。

70.专用集成电路(asic):是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。由于这种集成电路是按照用户要求定制的,其结构往往与特定用户要求相适应。

71.现场可编程门阵列(fpga):是在pal、gal等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数量有限的缺点。

72.用于神经网络模型的加速单元230:它是采用数据驱动并行计算的架构,用于处理各神经网络节点的大量运算(例如卷积、池化等)的处理单元。由于各神经网络节点的大量运算(例如卷积、池化等)中的数据和中间结果在整个计算过程中紧密联系,会被经常用到,用现有的cpu构架,由于cpu核内的内存容量很小,因此要大量频繁访问核外存储器,造成处理的低效。采用加速单元,其内部具有适于神经网络计算用到的存储容量的片上内存,避免频繁访问核外部的存储器,就能大大提高处理效率,提高计算性能。

73.加速单元230虽然对于特定的应用或领域来说,执行效率大大高于普通处理器的优点,但也要接受处理单元220的控制。以专用于深度学习模型的加速单元为例,存储器210

中存储有各种深度学习模型,包括这些模型的神经元和神经元的权重数据等。这些深度学习模型当需要时被图3中的一个处理单元220部署到一个加速单元230。具体地,处理单元220可以通过指令的形式向加速单元230告知加速单元 230深度学习模型在存储器210的存储位置。加速单元230然后可以根据这些位置进行寻址,将待执行指令存储在其片上内存中。处理单元220也可以通过指令的形式向加速单元230发送加速单元230的待执行指令,加速单元230接收指令并存储到片上内存中。加速单元230还可以通过上述方式获取输入数据。一旦加速单元230 获取到待执行指令和输入数据,就进行推理计算。节点的权重数据可以包含在深度学习模型的指令序列中,由加速单元230一并从存储器210中取出。当然节点的权重数据也可以独立存储,由加速单元230在需要时从存储器210中取出。处理单元 220是具有调度和控制能力的硬件单元,一般为中央处理器(cpu)、微控制器、微处理器等硬件单元。

74.本公开实施例的加速单元

75.下面结合图4介绍处理单元220和本公开实施例提供的加速单元2301各自的内部结构以及处理单元220是如何控制加速单元2301工作的。

76.如图4所示,处理单元220包含多个处理器核222和被多个处理器核222共享的高速缓存221。每个处理器核222包括取指令单元203、指令译码单元224、指令发射单元225、指令执行单元226。

77.取指令单元223用于将要执行的指令从存储器210中搬运到指令寄存器(可以是图4示出的寄存器堆229中的一个用于存放指令的寄存器)中,并接收下一个取指地址或根据取指算法计算获得下一个取指地址,取指算法例如包括:根据指令长度递增地址或递减地址。

78.取出指令后,处理单元220进入指令译码阶段,指令译码单元224按照预定的指令格式,对取回的指令进行解码,以获得取回的指令所需的操作数获取信息,从而为指令执行单元225的操作做准备。操作数获取信息例如指向立即数、寄存器或其他能够提供源操作数的软件/硬件。

79.指令发射单元225位于指令译码单元224与指令执行单元226之间,用于指令的调度和控制,以将各个指令高效地分配至不同的指令执行单元226,使得多个指令的并行操作成为可能。

80.指令发射单元225将指令发射到指令执行单元226后,指令执行单元226开始执行指令。但如果该指令执行单元226判断该指令应该是加速单元执行的,则将其转发到相应的加速单元执行。例如,如果该指令是一条神经网络推理(inference) 的指令,指令执行单元226不再执行该指令,而是将该指令通过总线发送到加速单元230,由加速单元230执行。

81.加速单元2301包括总线通道231、直接内存访问模块235、片上内存236、分发单元237、命令处理器238和pe阵列。

82.总线通道231是指令从总线进出加速单元230的通道。按照不同的机制,总线通道231可以包括pcie通道232、i2c通道233、jtag通道234。pcie即pci-express,是一种高速串行计算机扩展总线标准,是由英特尔在2001年提出的,旨在替代旧的 pci,pci-x和agp总线标准。pcie属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质

量等功能。它的主要优势就是数据传输速率高,而且还有相当大的发展潜力。目前,pcie的总线大多是pcie gen3,但本公开实施例也可以采用pcie gen4,即遵循pci-express4.0标准的总线通道。i2c通道233是由philips公司开发的一种简单、双向二线制同步串行总线通道。它只需要两根线即可在连接于总线上的器件之间传送信息。jtag是联合测试工作组(jointtest action group)的简称,是在名为标准测试访问端口和边界扫描结构的ieee 的标准1149.1的常用名称。此标准用于验证设计与测试生产出的印刷电路板功能。 1990年jtag正式由ieee的1149.1-1990号文档标准化,在1994年,加入了补充文档对边界扫描描述语言(bsdl)进行了说明。从那时开始,这个标准被全球的电子企业广泛采用。边界扫描几乎成为了jtag的同义词。jtag通道234即是遵循该标准的总线通道。

83.直接内存访问(dma,direct memory access)模块235是一些计算机总线架构提供的功能,它能使数据从附加设备(例如外部的存储器)直接写入到加速单元2301 的片上内存236中。这种方式相比于通过处理单元220获取数据,大大提高了加速单元2301的数据访问效率。正是因为有这样的机制,加速单元230可以直接访问存储器210,读取深度学习模型的权重和激活数据,大大提高了数据访问效率。虽然图上示出直接内存访问模块235位于处理器238和总线通道231之间,但是加速单元2301的设计不局限于此。此外,在某些硬件设计中,每个pe单元都可以包含一个直接内存访问模块235,从而直接从附加设备上读取数据并写入到片上内存236 中。

84.神经网络模型中,像矩阵运算、卷积和深度卷积这样的神经网络应用涉及大量的输入数据,通常无法一次性将所有输入数据到导入到加速单元2301上。因此本公开实施例的加速单元2301的做法是,如果判断该应用无法一次性地完成,由命令处理器238对要执行的神经网络应用分解成多个执行的子操作,将子操作转换为在多个pe集群组的每个pe集群上执行的指令序列(多个待执行指令),通过直接内存访问模块235分多次加载每个子操作需要的操作数据,并指定每个指令序列的操作数据,最终将每个pe集群组内包含的多个pe集群分别对应的指令序列和操作数据存储到相应存储单元中。可选地,子操作的操作数据被平均地分配给每个指令序列。

85.应注意,每个子操作产生的结果都是中间结果,因此最终还需要将多个子操作的中间结果整合为最终结果,由于中间结果是在pe集群中产生,而pe集群上的存储空间有限,由此不可能无限度地存储中间结果,因此指令序列中需包含将中间结果从pe集群倒回到相应的存储单元或将中间结果经由相应的存储单元导出到存储器210,而在所有或者部分在子操作完成之后的整合步骤时,可有多种整合方式,例如可将与同一个分发单元耦接的多个pe集群(在图4中属于同一行的pe集群) 的中间结果整合,然后多个pe集群组的中间结果整合。

86.如图上所示,命令处理器238与内存236耦接,内存236被划分为多个存储单元。多个存储单元分别与多个分发单元一一对应地耦接,每个分发单元分别与由多个pe集群组成的一个pe集群组耦接。每个分发单元从与其耦接的存储单元获取可在pe集群上执行的指令序列和操作数据,并分发给提供给与其耦接的pe集群。应注意,这里设计每个pe集群组包含的pe集群数量都相同,每个pe集群的功能和硬件结构都相同,因此部署在pe集群上执行的指令序列可以是相同的,并且可仅在第一次执行子操作将各个pe集群的指令序列和操作数据发送给各个pe集群,而在后续的多个子操作中只将新的操作数据发送给pe集群。

87.图上作为示例,存储单元为n,分发单元为n个,pe集群为n行m列。每个分发单元通过第一总线与一行的pe集群耦接,如果一行的pe集群要获得相同数据,则分发单元通过第一总线将该数据广播给一行的pe单元,否则,分发单元只负责通过第一总线将指令序列和操作数据分别发送给与其耦接的各个pe集群。如图上所示,每个pe集群进一步包括k个功能相同的pe单元,由此,构成了维度为n*m*k的三维pe阵列,其中m、n和k都是大于1的整数。当然基于同样的发明构思,还可设计二维或者三维以上的pe阵列。

88.图5a是一个示例性的pe集群的设计图。如图上所示,pe集群500包括集群控制单元602以及多个相同功能的、与集群控制单元602耦接的多个pe单元。集群控制单元602接收指令序列,指令序列包括数据加载指令。集群控制单元602控制各个pe单元执行相同的指令序列,并且可通过集群控制单元602产生的控制信号控制指令序列中的数据加载指令执行时,从不同的数据地址加载不同的操作数据,从而不同pe单元基于不同的操作数据得到不同的中间结果。

89.pe控制器501包含在每个pe单元中。每个pe单元还包括数据加载单元502、权重队列503、输入缓冲器504、索引比较单元505、选择器511、乘法累加器506、缓冲器508、输出队列513、选择器514-516、特殊控制单元509和特殊功能单元510。

90.数据加载单元502负责从分发单元601接收输入数据,并根据输入数据的数据类型将输入数据存储到权重队列503或输入缓冲器504。输入数据的数据类型包括权重数据和激活数据,权重数据被存储到权重队列503中,激活数据被存储到输入缓冲器 504中。同时,数据加载单元502通过检查激活数据的各个数值(即检查矩阵的各个项)是否等于0来生成激活数据的位掩码,因此激活数据的位掩码用于指示激活数据的各个数值是否为0,例如当为0时,位掩码设置为0。

91.在一些实施例中,处理单元220在编译和部署稀疏神经网络模型时,将其中的权重数据以“非零值 权重索引”的形式组织和存储,因此当权重数据通过分发单元601 进入pe集群时,加载到权重队列503的权重数据为权重索引以及与权重索引对应的非零值(图上的权重队列503中,采用不同图案标记权重索引和权重索引所对应的非零值。另一些实施例中,在进入到权重队列503之前,由分发单元601、命令处理器238 完成将权重数据转换为“非零值 权重索引”的形式组织和存储。这两种实施方式尤其适用于稀疏神经网络模型。

92.参考图上所示,为了实现权重数据的流式存储,权重队列503采用类似队列的体系结构设计。构成权重队列503的存储单元可以是移位寄存器,并且它可形成一个环形路径(loopback path),以支持在卷积操作时对权重数据的复用。环形路径是指队列首尾连接,当写和/或读操作进行的队列的尾部时,再一次写入和/或读取将回到队列的队首。

93.输入缓冲器504存储激活数据以及根据激活数据产生的位掩码。虽然未示出,但是这里的激活数据应包含激活索引以及与激活索引对应的激活数值,再加上位掩码根据则图上输入缓冲器504中存储激活索引、与激活索引对应的激活数值以及与激活索引对应的位掩码。

94.索引比较单元505负责产生有效负载,有效负载是指基于非零的权重和激活数据的矩阵运算。索引比较单元505包括加法器和比较器。加法器用于将权重索引和基地址(从权重队列503接收权重索引,基地址从集群控制单元602中获得)相加,得到输入索引。比较器接收加法器的输入索引,将输入索引与输出缓冲器504输出的索引值比较,如果相同并且

位掩码指示对应的数值不为0,则生成控制信号提供给选择器 511的控制端,使得输入缓冲器504输出与该输入索引对应的数值并提供给乘法累加器506。乘法累加器506用于执行乘法累加运算。乘法累加器506根据pe控制器501 的控制信号来停止累加乘法累加运算,并将累加结果输出到缓冲器中。

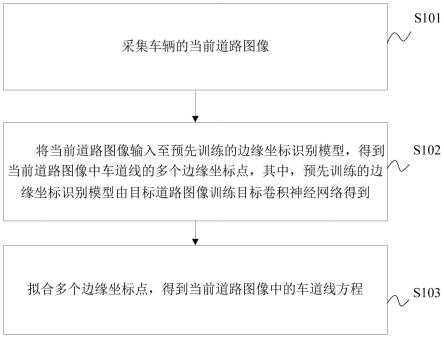

95.如图上所示,作为可选实施例,乘法累加器506包括乘法器5066、加法器5061、选择器5067、多个累积缓冲器5064、多个选择器5064、选择器5065、选择器5067。乘法器5066的输出端与加法器5061的输入端耦接。加法器5061的输出端与选择器 5067的输入端耦接,选择器5067的多个输出端与多个累积缓冲器5064分别耦接,多个累积缓冲器5063与多个选择器5064的输入端耦接,每个选择器5064的两个输出端分别与选择器5065的输入端、选择器5067的输入端耦接。选择器5065的输出端与加法器5061的输入端耦接。选择器5067的输出端与外部的缓冲器508耦接。

96.在累积缓冲器506中,乘法器5066产生的乘积被加法器5061累加。累加结果被输入到选择器5062,以根据来自pe控制器501的控制信号决定将累加结果保存四个缓冲器5063中的其中之一。多个累积缓冲器5063在图上为四个同质的累积缓冲器。存储在累积缓冲器5063中的累加结果被传输给不同的子模块,视操作而定。如图上所示,通过选择器5064和5065,累加结果可被传输给加法器5061以继续累加操作,累加结果还经过缓冲器508和选择器515和516被存储到输出队列513中。输出队列513可存储多次操作的累加结果,这些中间结果可经由分发单元601转移到内存236中,并可以进而转移到外部的存储器210上。累加结果还可作为中间结果长时间地保存在输出队列513中,并在适当时候提供给四个缓冲器5063,用于将多次累加结果再次累加。累加结果还可以经过选择器516被提供给特殊功能单元510。输出队列513中的累加结果还可以经由选择器514提供给特殊功能单元510。

97.特殊功能单元(sfu)510用于执行神经网络模型要求的所有特殊功能(例如激活函数或缩小)。特殊功能单元(sfu)510可通过消息队列/fifo接口与多个并行的 pe单元耦接。特殊功能单元510有自己的指令路径,并且与所有并行pe异步操作。因此,特殊功能单元510仅利用少量硬件操作算子来匹配多个pe单元的吞吐量,同时最小化面积和功耗。根据具体应用场景,特殊功能单元510可以在两种模式下运行:链式模式和解耦模式。链式模式通常应用于元素级(elment-wise)的特殊函数,例如神经网络模型的激活函数。通常,累积缓冲器506中的数据被写入到输出队列513,然后特殊功能单元510读取输出队列513以执行特殊函数,并将最终结果写回输出队列513。但是,在链式模式下,累积缓冲器506直接转移到特殊功能单元510中而不是输出队列513。这样,特殊功能单元510只需要每个pe单元对应的本地的输出缓冲区地址,对输出缓冲区513的内存访问减少了2/3。解耦模式通常应用于处理一些特殊的函数,比如规约(reduction),其需要并行的pe单元上的数据(输入数据在所有 pe单元之间交错)。执行这些特殊函数时,特殊功能单元510中的队列中的数据采用标记/令牌来标识数据属于哪个pe。通过标记/令牌,特殊功能单元510可以有效地判断当前特殊功能是否已完成。不同于链式模式,解耦模式需要全局的输出缓存区地址,以灵活访问任意pe单元的输出数据。

98.图5b是另一个示例性的pe集群的设计图。该设计引入了关于负载均衡的考量。如图上所示,和负载均衡相关的硬件模块包括:索引比较单元505、负载队列518和 519、均衡器517以及选择器520。

99.如图上所示,索引比较单元505负责产生有效负载,有效负载是指基于非零的权重和激活数据的矩阵运算。索引比较单元505包括加法器和比较器。加法器用于将权重索引和基地址(从权重队列503接收权重索引,基地址从集群控制单元602中获得) 相加得到与当前权重值对应的输入索引。比较器使用该输入索引检索输入缓冲器内的位掩码,如果与输入检索对应的位掩码等于1,则发现一个有效负载,并将输入索引存储到负载队列518中。注意,索引比较单元505并行处理两个权重索引,并根据激活稀疏性产生0/1/2的有效负载。

100.根据以上索引比较模块505的设计,pe单元采用了两级负载队列的设计。第一级的负载队列518使用双宽度设计以匹配索引比较单元505的推送负载(并行0/1/2的有效负载)。第二级的负载队列519采用标准的单宽度设计以便于于在某一个时刻弹出一个输入索引(对应于每个有效负载)。因此,第一级和第二级的负载队列松散地同步以处理宽度不匹配的问题。

101.在本实施例中,负载均衡的实现是这样的:左边的pe单元的负载队列518中的输入索引数量(即有效负载数量)远少于右边的pe单元的负载队列518中的输入索引数量为负载不均衡。由此,当右边的pe单元中的负载均衡器517检测到上述负载不均衡时,在运行状态下执行负载均衡。当执行负载均衡时,本地的负载队列518中弹出的输入索引会被推送给左边的pe单元中的负载队列518而不是推送给本地的负载队列 519。此外,为了实现负载均衡,各个pe单元中的输入缓冲器504和权重队列503需要扩增一倍,扩增的部分用来存储右边的pe单元的激活和权重数据,这样左边的pe单元从右边的pe单元中获取到输入索引以后,才能够直接在自己的输入缓冲器504和权重队列503中取出激活和权重数据进行运算。当然,负载均衡的实现不局限与本实施例,还有其他实施方式,例如,将本实施例中的左右pe单元交换也是成立的,再例如要求每个pe单元定期向分发单元601报告自身的负载状况,而分发单元601基于接收到的各个pe单元的负载状况,控制将数据和待执行指令发送给负载较低的pe单元。

102.如图上所示,从负载队列519中弹出的输入索引用于获取相应的非零值的激活数据。弹出的输入索引被提供给选择器511的控制端,选择器511将与输入索引匹配的激活数值输出给乘法器5066,乘法器5066同时从权重队列503接收与输入索引匹配的权重数值,然后,乘法器5066执行乘法运算。然后由乘法器5066产生的乘积被提供给加法器5061以进行累加操作。加法器5061还接收右边的pe单元的部分和作为输入。由加法器5061输出的累加结果被提供给选择器5062以决定使用哪个缓冲器进行存储。如图上所示,每个pe单元拥有四个异构的累积缓冲器以维持不同输入的部分结果。取决于将要执行的不同操作,累积缓冲器506中的数据被传送给不同的子模块,包括:提供给加法器506做累加操作;由选择器516提供给左边的pe单元的选择器520的输入端;作为输出结果存储到输出队列513中;作为输入数据提供给例如激活函数和缩小 (reduction)的特殊功能单元。

103.应该理解,图5b所示的pe集群结构是针对图5a的改进设计。因此一些在图5a中已经描述的结构和功能在图5b中未详细描述。图5c是图5a和图5b中的集群控制单元的示意结构图。集群控制单元602设置在pe集群中,用于产生多个控制信号以提供给与它耦接的多个pe单元。如图上所示,集群控制单元602包括选择单元603、多个指令缓冲器1至x,标量计算单元604、寄存器文件605、解析器606和操作单元607。选择单元603包括一个输入端和两个输出端,两个输出端分别与解析器606、操作单元607 分别耦接。解析器606分别与多个指令

缓冲器1-x耦接。操作单元607分别与多个指令缓冲器1-x耦接。多个指令缓冲器1-x均与pe单元1-x耦接(为了简便,图上仅画出了指令缓冲器1-x与pe单元1的连线)。

104.指令缓冲器1-x用于存储指定神经网络应用(target application)的指令序列。注意,每个指令缓冲器可以存储多条指令并根据它自己的程序计数器(programcounter)执行这些指令。每个指令缓冲器使用隐式回环的程序计数器(implicitloopback pc)来自动发射重复的指令。这些指令缓冲器可以各自独立地为不同的硬件模块工作,每个指令缓存器享有一个独立的指令流水线,该指令流水线不受其他指令序列执行过程的影响(decoupled execution pipeline)。值得注意的是,为了方便和高效控制指令流水线,这些指令缓冲器可以彼此触发执行。指令缓冲器中的每条指令的操作数被存储在寄存器文件605的不同条目中(图上寄存器文件605包括1-n的条目)。标量计算单元604用于负责执行指令的操作数进行标量计算并根据计算结果更新寄存器文件的相应条目。此外,由于pe单元执行的是向量乘法,因此,标量计算单元604还可以接收多个pe单元的部分中间计算结果,并进行标量计算(例如标量累加),标量计算结果可存储在寄存器文件的相应条目中。如此,也能够加快标量计算速度。

105.当集群控制单元602工作时,集群控制单元602中的选择单元603从分发单元601 接收命令和数据,从命令中得到命令类型和缓冲器标识,确定命令类型是配置还是执行,如果是配置,则将接收到的数据和缓冲器标识提供给解析器606,如果是执行,则将缓冲器标识提供给操作单元607。

106.解析器606用于从数据中解析出指令序列,将指令序列存储到与缓存器标识匹配的指令缓存器中,以及将指令序列的每条指令的操作数存储在寄存器文件的相应条目中。可选地,解析器还根据指令序列中每条指令原始的操作数确定该指令在每个 pe单元上执行时的操作数,并将其度确定的操作数存储到寄存器文件的相应条目中。例如,在每条指令原始的操作数是数据地址,则要将该指令分配到多个pe单元执行时,则根据原始的数据地址确定在每个pe单元执行时的数据地址。

107.操作单元607接收缓存器标识,驱动与缓存器标识匹配的指令缓存器逐一执行其中的每条指令,以产生控制信号,每条指令的控制信号以及寄存器文件中该指令的操作数被发送给多个执行单元,每个执行单元基于接收到的控制信号和操作数执行相应操作。

108.实际上,指定神经网络应用的处理可分为两个阶段:配置阶段和执行阶段。配置阶段,指令缓冲器1-x被初始化为指定神经网络应用的指令序列,寄存器文件中的各个条目被初始化为指定神经网络应用的指令序列的各个指令的操作数。执行阶段,分发单元601将指定神经网络应用的操作数据发送给每个pe集群,同时,分发单元601 发送一条命令,该命令包含要选择执行的指令缓冲器的标识(id),操作单元607 通过该标识,驱动被预先加载到对应的指令缓冲器中的指令序列中的各个指令逐一执行。这些指令在执行过程中为每个pe单元产生控制信号,每个pe单元根据接收到的控制信号从指定神经网络应用的操作数据中加载自身的操作数据,然后pe单元就可以在自身的操作数据的基础上根据接收到的控制信号执行相应操作。

109.此外,分发单元601在往pe集群分发指令/数据时使用堆叠设计(packed design)。所述堆叠设计是指:数据与命令堆叠到一起。在配置阶段,命令指明哪个指令缓冲器被选出来存储与它在一起的指令序列。在执行阶段,命令指明哪个指令缓存器被选出来处理与它

在一起的操作数据。

110.而且,当处理指定神经网络应用时,其对应的指令流水线和pe单元的硬件流水线分开,不会相互干扰。取决于不同的神经网络应用,本公开实施例的加速单元使用两种类型的指令流水线。

111.第一种指令流水线包括两级:译码(id)级、取数(fo)级,在译码级,根据当前指令的操作码产生控制信号。在取数级,需要的操作数(例如,缓冲区地址,累积缓冲器的标识(id),等等)在从寄存器文件中取出。然后,各个pe单元被指示处理与当前指令耦合的数据。此种情况下,指令流水线仅提供必要的信息给各个 pe单元,且不需要其他操作。应注意,这种类型的指令流水线是为那些不需要更新指令的操作数的神经网络应用设计的,这样的神经网络应用例如为矩阵乘法(spmv 和spmm)。

112.第二种指令流水线包括四级:译码(id)级、取数(fo)级、标量计算单元处理(su)级和写回(wb)级。前两级(id和fo)和第一种的指令流水线中的前两级相同,但不同于第一种的指令流水线,第二种的指令流水线是为那些在pe单元结束执行后,需要更新指令的操作数的神经网络应用而设计的,这些的神经网络应用包括卷积(spconv)和深度卷积(depth-wise conv)。在标量计算单元处理级,标量计算单元604被用于执行标量计算以更新当前指令的相应操作数。然后,被更新的操作数在写回级被写回到寄存器文件的相应条目中。

113.在本公开中,基于有限状态机(fsm)和数据相关指令来实现指令设计。具体地, pe单元的行为取决于三个关键因素:与数据堆叠在一起的命令;在指令缓冲器内存储的指令以及标量流水线的状态。三个因素的具体设计如下所述。

114.首先,在配置阶段,分发单元601将指定神经网络应用的指令序列以及一个包含指令缓冲器的标识(id)的命令传送给pe集群,此时命令中的指令缓冲器的标识指示与该命令一起传输的指令序列要存储的指令缓冲器;在执行阶段,分发单元将操作数据(可以是指定神经网络应用的一部分或者全部的操作数据)以及一条包含了指令缓存器的标识(id)的命令发送给pe集群,此时命令中的指令缓冲器的标识指明与该命令一起传输的操作数据由哪个缓冲器中的指令序列处理。一个示例性的命令设计如下表格所示。

115.表格1

[0116][0117]

命令一块采用8个比特,以最小化分发单元与pe集群之间的数据传输的额外开销。命令分为两种:配置命令和执行命令,分别对应于配置阶段和执行阶段。参考表格1 所示,操作码(config或exe)占用第一个比特。在配置命令中,第二个到第三个比特保留,第四到第八个比特用于编码指令缓冲器的标识。在执行命令中,第二个比特是决定pe单元是否移出累积结果的标识。第二个比特是指示pe单元的当前数据段是否是输入数据的最后一个数据段的标识,如果是,则累积结果被写回到输出缓存器中。类似于配置命令,执行命令的第四到第八个比特用于编码指令缓冲器的标识。

[0118]

表格2示出了在指令缓冲器中的指令设计。这四种指令覆盖了神经网络应用 (spmv、spmm、spconv和depth-wise conv)所涉及的所有操作。

[0119]

表格2

[0120][0121]

如表格2所示,第一个到第二个比特用于编码操作码。对于乘法累加指令(mac),第三个比特和第四个比特分别指示是否负载均衡和特殊功能单元是否激活。第五个到第八个比特用于编码输入缓冲器的基地址,第九个到第十个比特用于编码累积缓冲器的标识,最后两个比特保留。对于数据加载指令和数据存储指令(ld/st),第五到第八个比特用于编码要导入/存储到的输入/输出缓冲器的基地址。对于spu(特殊功能函数)的指令,第三个到第四个比特指示要执行的特殊功能函数的类型。注意,在本设计中,直接写到输出缓冲器也被编码为一个类型的特殊功能函数(non-sf),第五个到第八个比特和第九个到第十二个比特编码特殊功能函数的输入数据和输出数据的缓冲器地址。

[0122]

标量流水线的状态主要用于控制权重队列的行为。标量流水线的状态包括三种,这三种状态应用于不同的神经网络应用。对于spmv和spmm,权重队列作为一个移动队列并且相应的标量流水线的状态被定为一个先入先出队列(sq)。尽管如此,由于spconv需要权重队列支持回环路径的旋转操作,对应的状态被定为旋转队列 (rotation queue)。

[0123]

深度卷积(depth-wise conv),权重队列实际上存储的是激活数据。为最小化分发单元与pe集群之间的数据传输,我们充分利用滑动窗口来产生交叠区域,通过仅弹出与交叠区域的数据代替了从权重队列中弹出所有激活数据。通过这种方法,权重队列在滑窗模式下工作,从而将相应的标量流水线状态称为滑窗(sliding window) 队列。结果是,通常,sq状态下是先入先出的弹出数据,rq状态下是循环地弹出数据(回环路径实现权重复用),在sw状态,数据加载到pe单元和从pe单元上导出。

[0124]

下面介绍spmv的指令序列。其他应用的指令序列可以由spmv的指令序列中作一些修改生成。基于spmv的指令序列,可以了解如何使用这些指令集合执行其他应用。 spmv的指令序列被划分为五个主要的阶段。

[0125]

第一阶段是在执行阶段之前配置指令缓冲器(即为上面的config)。

[0126]

第二阶段是在执行过程中写入激活数据和生成位掩码(对应指令为ld)。

[0127]

第三阶段是写部分累加结果(对应指令为ld)。

[0128]

第四阶段是执行(对应指令为mac,包括balance,spu的指示信息)。

[0129]

第五阶段是读出(对应指令为st)。

[0130]

下文重点讨论在pe集群上执行的指令。在第一阶段,只有与配置相关的指令被执行,以初始化指令缓冲区、标量计算单元和寄存器文件。第二阶段和第三阶段,执行ld指令

以将数据加载到pe集群中。第四阶段,根据来自分发单元内的命令和执行阶段之前的各种配置,具有不同配置(shifting、load balancing、spu等)的mac 指令被执行。第五阶段,执行st指令以从pe集群中导出数据。

[0131]

根据spmv的指令序列,我们可以生成其他神经网络应用的指令序列。对于spmm,第四阶段的指令缓冲区应包括多个mac指令。这些mac指令是根据指令缓冲器自己的 pc进行发射和执行。对于spconv,在预先配置的mac指令之后,根据标量流水线的状态指示权重队列旋转。深度卷积(depth-wise conv)采用与spmv类似的指令序列,唯一区别在于,权重和激活数据的角色在深度卷积中互换了。

[0132]

将神经网络应用映射到本公开实施例的加速单元上执行

[0133]

加速单元可支持多种神经网络应用,常用的神经网络应用有:矩阵乘法(matrixmultiplication)、卷积和深度卷积(depth convolution)。而这些神经网络应用的最基础的运算是相乘和累加,因此公开实施例设计的pe单元主要完成相乘和累加运算。下面基于神经网络应用进行详细说明。

[0134]

图6a示出矩阵乘法的示意图。如图6a所示,激活数据为m*k的二维矩阵,m 表示行,k表示列,权重数据为k*n的矩阵,表示行,n表示列,则输出数据为m*n 的矩阵,m表示行,n表示列。举例说明,a是2*3的矩阵,b是3*2的矩阵,c为a 和b的矩阵乘积,为2*2的矩阵,其运算过程如下。

[0135][0136][0137][0138]

如图6b和6c所示,在卷积和深度卷积中,更多维度被包含进来。参考图6b所示,激活数据、权重数据和输出数据都是四维矩阵(本文将一维和二维矩阵称为低维矩阵,将三维及以上的矩阵称为高维矩阵)。激活数据的参数为[b,w,h,c

in

],权重数据的参数为[c

out

,l,l,c

in

],输出数据的参数为[b,w,h,c

out

]。为了方便理解,我们将本示例理解为对图像数据的卷积操作。b表示图像数量,w和h表示图像尺寸中的宽度和高度,c

in

表示通道数,例如rgb的图像的c

in

等于3。卷积操作可理解为采用l*l*c

in

的卷积核在每个图像(图上c

in,

w和h限定的立方体)上进行扫描以得到输出图像的过程,其对应的计算过程是:先将l*l的矩阵与二维图像中的对应的特征元素求内积,将内积值求和,然后将c

in

个对应坐标的内积和相加作为二维特征图上对应坐标上的值。换言之,l*l*c

in

的卷积核与一个[w,h,c

in

]定义的图像进行计算得到一个w*h的二维特征图。c

out

个l*l*c

in

的卷积核与一个[w,h,c

in

]定义的图像进行计算得到一个c

out

*w*h输出特征图。由于作为激活数据的图像有b个,因此最终得到b个cout*w*h的输出特征图。图5c的深度卷积的的计算过程包括:先将l*l 的卷积核与输入二维图像中的对应的特征元素求内积,将内积值求和作为输出二维特征图上对应坐标上的值,c是输入和卷积核的通道数,保持不变,作为输出图像的通道数,最终得到b个c*w*h的特征图。

[0139]

从上述内容可以发现,卷积和深度卷积的基础运算是矩阵运算(相乘和累加),只

是卷积和深度卷积涉及更多维度,但是在程序处理时,可将卷积和深度卷积的高维矩阵运算转换为多次迭代的多个低维矩阵运算。以图6a-6c为例,将图6b-6c中的bwh对应于图6a中的m,cin对应于图6a中的k,cout对应于图6a中的n,按照这种方式,图6b-6c所指示的卷积和深度卷积转换为多次迭代的m*k的二维矩阵与 k*n的矩阵运算。在执行神经网络应用时,还涉及到利用直接内存访问(dma,directmemory access)模块235将每次运算所需的数据加载到片上内存236的操作。

[0140]

在实施时,将卷积和深度卷积的高维矩阵运算转换为多次迭代的多个低维矩阵运算有多种实现方式。本实施例定义了三种映射方法:输入固定(input stationary) 映射方法、权重固定(weight staionary)映射方法和输出固定(output stationary) 映射方法。命令处理器238在处理神经网络应用时,可选择其中之一的映射方法。对于每个神经网络应用来说,优选的映射方式应该能够减少加速单元2301与外部存储器210之间的数据传输。为此,加速单元2301可配置每个神经网络应用的优选的映射方法,以便于在执行每个神经网络应用时使用对应的方法。

[0141]

下面还是以矩阵相乘为例介绍这三种映射方法。

[0142]

输入固定映射方法的核心思想是尽可能长时间地激活数据保留在pe阵列中。下面以图7a所示的伪代码示例进行说明。该段伪代码包括多次迭代过程(迭代次数由 iter_n0,iter_k0和iter_m0决定),每次迭代指定一个在pe阵列上运行的二维矩阵乘法。该二维矩阵乘法的输入矩阵的符号为i(激活数据)和w(权重数据),输出矩阵的符号为o。对于i,通过m_start和m_end定义其在二维矩阵(由高维矩阵的激活数据转换而来)中的行开始序号和行结束序号,通过k_start和k_end定义其在二维矩阵中的列开始序号和列结束序号。同样,对于w,通过k_start和k_end定义其在二维矩阵(由高维矩阵的权重数据转换而来)中的行开始序号和行结束序号,通过n_start和n_end定义其在二维矩阵中的列开始序号和列结束序号。对于o,也是如此。

[0143]

通过伪代码可以看出,作为嵌套循环的条件语句,n先于k发生改变,k先于m 发生改变,由此k*n限定的来自权重数据的二维矩阵将先于m*k限定的来自激活数据的二维矩阵发生改变,因此,当m和k保持不变,n发生变化时,将一个由m*k 限定的二维矩阵部署到pe阵列上,并保持一段时间,该一个由k*n限定的二维矩阵不断地被从外部存储器加载进来并输送到pe阵列中,当k发生变化时,由m*k限定的二维矩阵才发生改变,此时,将新的m*k从外部存储器上加载到pe阵列中。此外,由m*n限定的输出二维矩阵有时需要写回到存储器210中。应注意,如果pe阵列能够保持所有由m*k限定的二维矩阵,则没有必要采用输入固定映射方法。

[0144]

输出固定映射方法的核心思想是尽可能长时间地将输出数据保留在片上内存 236中。对应的伪代码如图7b所示。关于这段伪代码的分析可参见上文,这里就不再详细叙述。应注意,当在片上内存236中能够存储所有激活数据时,则没有必要采用输入固定数据加载方法。

[0145]

权重固定映射方法的核心思想是尽可能长时间地将权重数据保留在片上内存 236中。对应的伪代码如图7c所示。关于这段伪代码的分析可参见上文,这里就不再详细叙述。应注意,权重固定映射方法只能在权重数据和计算分离的情况下才能够使用。如果权重数据和计算交叠在一起,则不能够使用权重固定映射方法。当采用权重固定映射方法时,命

令处理器238在加载新的激活数据到片上内存236之前,还需要将当前的部分结果数据(由pe阵列计算得到)写回到存储器210中。

[0146]

在施行上述映射方法时,还需要考虑到数据传输流水线(data transferpipeline)的问题。参考图7a的伪代码,pe阵列执行第k 1次迭代计算时,pe阵列首先从片上内存236加载本次迭代的激活数据和权重数据。作为本次迭代的激活数据和权重数据是由命令处理器238在第k个迭代时从存储器210加载到片上内存 236中的。注意片上内存236作为全局存储区,每个存储单元都是按照ping-pong 设计的,该设计针对每个存储单元都设计成两个单元,第一单元用于从存储器210 加载数据,第二单元用于将数据提供给pe阵列。因此,在pe计算期间,将下一次迭代的激活和权重数据从存储器210传送到片上内存236以及将下一次迭代的激活数和权重据从片上内存236传送到pe阵列中。因此,如果pe阵列的计算时间大于从存储器210加载激活和权重数据时,从存储器210加载激活和权重数据的时间就被隐藏在pe阵列的计算时间内,这将有助于提高加速单元的执行效率。在最后一次迭代中,需要为下一组的第一次迭代准备输入的激活数据和权重数据。同时,输出数据在最后一次迭代中将被从pe阵列写回到存储器210中。输出数据从片上内存 236写回到存储器210中的操作在下一个组的第一次迭代中执行。

[0147]

在本公开实施例的加速单元中施行的数据切分方法

[0148]

参见前文所述,命令处理器238经由直接内存访问模块235将每次迭代所需的数据加载到片上内存236的各个存储单元中,然后通过分发单元将数据分发给pe集群,pe集群又进一步将数据分发给pe单元。在此过程中,分发单元通常将按照m, n和k的维度将切分矩阵,以得到可分发给pe集群中的矩阵。

[0149]

参考图8所示,激活数据是行数为4,列数为8的二维矩阵;权重数据是行数为 8,列数为8的二维矩阵;输出矩阵为行数为4,列数为8的二维矩阵。下面具体介绍如何将图8所示的矩阵相乘部署到2*2的pe阵列中执行,该2*2的pe阵列包括 pe集群(0,0)、pe集群(1,0)、pe集群(0,1)和pe集群(1,1)。在我们的设计中,每个pe集群是2维网格。因此,将上述矩阵映射到pe阵列时,在每个维度上有三种选择,总计有9种选择。

[0150]

图9a-图9i示出了如何将图8所示的矩阵乘法部署到pe阵列的9种选择。在图中,i、w和o分别表示在相应的pe集群执行的矩阵乘法的激活数据、权重数据和输出矩阵。

[0151]

在图9a中,由pe集群(0,0)执行激活数据的第一行(即i[0:1,0:8])与权重数据(即w[0:8,0:8])相乘的任务,执行结果是输出输出数据的第一行(即o [0:1,0:8])。其中,i[0:1,0:8]中的[0:1,0:8]指定输入数据的行和列,[0,1]表示第一行,[0,8]表示第1列到第8列,w[0:8,0:8]表示权重数据中第1至第8行,第 1至第8列组成的矩阵,即一个完整的权重数据,o[0:1,0:8]表示输出数据的第1 行、第1至第8列组成的矩阵。图9a-9i中这些数据的表示方法都相同,因此在下文中不再详细描述。在pe集群(1,0)上执行激活数据的第二行(即i[1:2,0:8]) 与权重数据(即w[0:8,0:8])相乘的任务,执行结果是输出输出矩阵的第二行(即 o[1:2,0:8])。在pe集群(0,1)上执行激活数据的第三行(即i[2:3,0:8])与权重数据(即w[0:8,0:8])相乘的任务,执行结果是输出输出矩阵的第三行(即 [2:3,0:8])。在pe集群(1,1)上执行激活数据的第四行(即i[3:4,0:8])与权重数据(即w[0:8,0:8])相乘的任务,执行结果是输出输出矩阵的第四行(即o [2:3,0:8])。

[0152]

基于图9a可知,pe集群(0,0)至pe集群(1,1)上参与矩阵相乘的输入和输出矩阵均

不相同,但是在pe集群(0,0)至pe集群(1,1)上参与矩阵相乘的权重数据相同,也就是说,pe集群(0,0)至pe集群(1,1)共享权重数据。

[0153]

在图9b中,由pe集群(0,0)执行激活数据的前两行(i[0:2,0:8])与权重数据的前4列(即w[0:8,0:4])相乘的任务,执行结果是输出输出数据的前两行和前四列(即o[0:2,0:4])。在pe集群(1,0)上执行激活数据的后两行(即i[2:4,0:8]) 与权重数据的后4列(即w[0:8,0:4])相乘的任务,执行结果是输出输出矩阵的前两行和前四列(即o[0:2,0:4])。在pe集群(0,1)上执行激活数据的前两行 (i[0:2,0:8])与权重数据的后四列(即w[0:8,4:8])相乘的任务,执行结果是输出输出矩阵的前两行和后四列(即[0:2,4:8])。在pe集群(1,1)上执行激活数据的前两行(即i[2:4,0:8])与权重数据的后4列(即w[0:8,4:8])相乘的任务,执行结果是输出输出矩阵的前2行和后4列(即o[2:4,4:8])。

[0154]

基于图9b可知,pe集群(0,0)至pe集群(1,1)上参与矩阵相乘的输入和输出矩阵均不相同,但是pe集群(0,0)和pe集群(1,0)之间的权重数据相同,pe集群(0,1)和pe集群(1,1)之间的权重数据相同。

[0155]

在图9c中,由pe集群(0,0)执行激活数据的前两行和前四列(i[0:2,0:4]) 与权重数据的前4行(即w[0:4,0:8])相乘的任务,执行结果是输出输出数据的前两行(即o[0:2,0:8])。在pe集群(1,0)上执行激活数据的后两行和前四列(即 i[2:4,0:4])与权重数据的前四行(即w[0:4,0:8])相乘的任务,执行结果是输出输出矩阵的后两行(即o[2:4,0:8])。在pe集群(0,1)上执行激活数据的前两行和后四列(i[0:2,4:8])与权重数据的后四行(即w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的前两行(即[0:2,0:8])。在pe集群(1,1)上执行激活数据的前两行和后四列(即i[2:4,4:8])与权重数据的后4行(即w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的前2行(即o[2:4,0:8])。

[0156]

基于图9c可知,pe集群(0,0)至pe集群(0,1)输出的矩阵相同,需要将两个矩阵对应位置上的值相加得到最终值。同样,pe集群(1,0)和pe集群(1,1)输出的矩阵相同,需要将两个矩阵对应位置上的值相加得到最终值。

[0157]

在图9d中,由pe集群(0,0)执行激活数据的前两行(i[0:2,0:8])与权重数据的前4列(即w[0:8,0:4])相乘的任务,执行结果是输出输出数据的前两行和前四列(即o[0:2,0:4])。在pe集群(1,0)上执行激活数据的前两行(即i[0:2,0:8]) 与权重数据的后四列(即w[0:8,4:8])相乘的任务,执行结果是输出输出矩阵的前两行和后四列(即o[0:2,4:8])。在pe集群(0,1)上执行激活数据的后两行 (i[2:4,0:8])与权重数据的前四列(即w[0:8,0:4])相乘的任务,执行结果是输出输出矩阵的后两行和前四列(即[2:4,0:4])。在pe集群(1,1)上执行激活数据的后两行(即i[2:4,0:8])与权重数据的后4列(即w[0:8,4:8])相乘的任务,执行结果是输出输出矩阵的后两行和后四列(即o[2:4,4:8])。

[0158]

基于图9d,将pe集群(0,0)至pe集群(1,1)上的输出矩阵组合起来得到最终的矩阵相乘结果。

[0159]

在图9e中,由pe集群(0,0)执行激活数据(i[0:4,0:8])与权重数据的前2 列(即w[0:8,0:2])相乘的任务,执行结果是输出输出数据的前两列(即o[0:4, 0:2)。在pe集群(1,0)上执行激活数据(即i[0:4,0:8])与权重数据的第三列和第四列(即w[0:8,2:4])相乘的任务,执行结果是输出输出矩阵的第三列和第四列(即o[0:4,2:4])。在pe集群(0,1)上执行激活数据(i[0:4,0:8])与权重数据的第五到第六列(即w[0:8,4:6])相乘的任务,执行结果

是输出输出矩阵的第五到第六列(即[0:4,4:6])。在pe集群(1,1)上执行激活数据(即i[0:4,0:8]) 与权重数据的第七到第八列(即w[0:8,6:8])相乘的任务,执行结果是输出输出矩阵的第七到第八列(即o[0:4,6:8])。

[0160]

基于图9e,将pe集群(0,0)至pe集群(1,1)上的输出矩阵组合起来得到最终的矩阵相乘结果。

[0161]

在图9f中,由pe集群(0,0)执行激活数据的前四列(i[0:4,0:4])与权重数据的前四行和前四列(即w[0:4,0:4])相乘的任务,执行结果是输出输出数据的前四列(即o[0:4,0:4)。在pe集群(1,0)上执行激活数据的前四列(即i[0:4,0:4]) 与权重数据的前四行和后四列(即w[0:4,4:8])相乘的任务,执行结果是输出输出矩阵的前四行和后四列(即o[0:4,4:8])。在pe集群(0,1)上执行激活数据的后四列(i[0:4,4:8])与权重数据的后四行和前四列(即w[4:8,4:4])相乘的任务,执行结果是输出输出矩阵的前四行和前四列(即[0:4,0:4])。在pe集群(1,1)上执行激活数据的后四列(即i[0:4,4:8])与权重数据的后四行和后四列(即 w[4:8,4:8])相乘的任务,执行结果是输出输出矩阵的后四列(即o[0:4,4:8])。

[0162]

基于图9f,将pe集群(0,0)和pe集群(0,1)上的输出矩阵的对应值相加得到最终值,将pe集群(1,0)和pe集群(1,1)上的输出矩阵的对应值相加得到最终值,最后组合而成的矩阵为最终的矩阵相乘结果。

[0163]

在图9g中,由pe集群(0,0)执行激活数据的前两行和前四列(i[0:2,0:4]) 与权重数据的前4行(即w[0:4,0:8])相乘的任务,执行结果是输出输出数据的前两行(即o[0:2,0:8)。在pe集群(1,0)上执行激活数据的前两行和后四列(即 i[0:2,4:8])与权重数据的或四行(即w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的前两行(即o[0:2,0:8])。在pe集群(0,1)上执行激活数据的第三和四行和前四列(i[2:4,0:4])与权重数据的前四行(即w[0:4,0:8])相乘的任务,执行结果是输出输出矩阵的第三行和第四行(即[2:4,0:8])。在pe集群(1,1)上执行激活数据的后两行和后四列(即i[2:4,4:8])与权重数据的后四行(即 w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的后两行(即o[2:4,0:8])。

[0164]

基于图9g,将pe集群(0,0)和pe集群(1,0)上的输出矩阵的对应值相加得到最终值,将集群(0,1)和pe集群(1,1)上的输出矩阵的对应值相加得到最终值,最终组合而成的矩阵为最终的矩阵相乘结果。

[0165]

在图9g中,由pe集群(0,0)执行激活数据的前两行和前四列(i[0:2,0:4]) 与权重数据的前4行(即w[0:4,0:8])相乘的任务,执行结果是输出输出数据的前两行(即o[0:2,0:8)。在pe集群(1,0)上执行激活数据的前两行和后四列(即 i[0:2,4:8])与权重数据的后四行(即w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的前两行(即o[0:2,0:8])。在pe集群(0,1)上执行激活数据的第三和四行和前四列(i[2:4,0:4])与权重数据的前四行(即w[0:4,0:8])相乘的任务,执行结果是输出输出矩阵的第三行和第四行(即[2:4,0:8])。在pe集群(1,1)上执行激活数据的后两行和后四列(即i[2:4,4:8])与权重数据的后四行(即 w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的后两行(即o[2:4,0:8])。

[0166]

基于图9g,将pe集群(0,0)和pe集群(1,0)上的输出矩阵的对应值相加得到最终值,将集群(0,1)和pe集群(1,1)上的输出矩阵的对应值相加得到最终值,最终组合而成的矩阵为最终的矩阵相乘结果。

[0167]

在图9h中,由pe集群(0,0)执行激活数据的前四列(i[0:4,0:4])与权重数据的前4

行和前四列(即w[0:4,0:4])相乘的任务,执行结果是输出输出数据的前四列(即o[0:4,0:4)。在pe集群(1,0)上执行激活数据的后四列(即i[0:4,4:8]) 与权重数据的后四行(即w[4:8,0:8])相乘的任务,执行结果是输出输出矩阵的前四列(即o[0:4,0:4])。在pe集群(0,1)上执行激活数据的前四列(i[0:4,0:4]) 与权重数据的前四行和后四列(即w[0:4,4:8])相乘的任务,执行结果是输出输出矩阵的前四行和后四列(即[0:4,4:8])。在pe集群(1,1)上执行激活数据的后四列(即i[0:4,4:8])与权重数据的后四行和后四列(即w[4:8,4:8])相乘的任务,执行结果是输出输出矩阵的后四列(即o[0:4,4:8])。

[0168]

基于图9h,将pe集群(0,0)和pe集群(1,0)上的输出矩阵的对应值相加得到最终值,将集群(0,1)和pe集群(1,1)上的输出矩阵的对应值相加得到最终值,最终组合而成的矩阵为最终的矩阵相乘结果。

[0169]

在图9i中,由pe集群(0,0)执行激活数据的前两列(i[0:4,0:2])与权重数据的前2行(即w[0:2,0:8])相乘的任务,执行结果是输出输出数据(即o[0:4, 0:8)。在pe集群(1,0)上执行激活数据的第三和四列(即i[0:4,2:4])与权重数据的第三行和第四行(即w[2:4,0:8])相乘的任务,执行结果是输出输出矩阵的前四行(即o[0:4,0:8])。在pe集群(0,1)上执行激活数据的第五和第六列 (i[0:4,4:6])与权重数据的第五行和第六行(即w[4:6,0:8])相乘的任务,执行结果是输出输出矩阵(即[0:4,0:8])。在pe集群(1,1)上执行激活数据的后两列 (即i[0:4,6:8])与权重数据的第七和第八行(即w[6:8,0:8])相乘的任务,执行结果是输出输出矩阵(即o[0:4,0:8])。

[0170]

基于图9h,将pe集群(0,0)至pe集群(1,1)上的输出矩阵的对应值相加得到最终的矩阵相乘结果。

[0171]

总结而言,沿m方向(激活数据的行方向)切分意味由不同的pe集群处理激活数据和输出矩阵的不同行数据,但是这些pe集群之间共享相同的权重数据。可根据激活数据的有效行数确定参与计算的pe集群的个数。例如,在spmv(sparsematrix-vector multiplication,稀疏矩阵-向量乘法)中,只有一个pe集群是有效的(pe阵列的行和列方向包含不同的m)。

[0172]

沿着n方向(权重数据的列方向)切分意味着由不同pe集群计算各种沿着n方向切分的各种输出矩阵切片,并且pe集群之间共享相同的输入矩阵切片。在这种切分方法下,不同pe集群需要不同的权重数据。如果在计算中权重数据的复用程度较低 (更小的m),则数据传输延迟将变得更加严重。

[0173]

沿着k方向(权重数据的行方向)切分意味着不同pe集群计算同一输出矩阵切片的部分和。在这种切分方法下,在计算期间不同pe集群之间不共享数据。同时,不同集群产生的部分和需要累加到一起,以得到最终结果。

[0174]

本公开实施例提供的加速单元,通过将神经网络模型的待执行指令分解成多个迭代进行的多个子操作,通过所述直接内存访问模块获取所述多个子操作的操作数据,然后将多个子操作部署到pe阵列上执行,由于pe阵列包括三维pe单元,每个 pe单元可执行设定操作,因此三维pe单元的并行执行能够实现对神经网络应用的硬件加速。

[0175]

进一步地,所述通过将神经网络模型的待执行指令分解成多个迭代进行的多个子操作并将多个子操作部署到pe阵列上为:将高维矩阵的激活数据和权重数据的运算转换成迭代进行的低维矩阵的激活数据和权重数据的运算,并将低维矩阵的激活数据和权重数据

的运算部署到pe阵列上,每个pe单元可用于执行一维矩阵相乘运算并且一维相乘运算结果还可以累加到一起,如此有助于实现对于对神经网络应用的硬件加速。

[0176]

进一步地,由于神经网络模型主要包括几个关键的神经网络应用,例如矩阵乘法、卷积和深度卷积等神经网络应用,这些关键神经网络应用都可以转换为转换成迭代进行的低维矩阵的激活数据和权重数据的运算,由此实现对神经网络应用的硬件加速,并进一步实现对神经网络模型的硬件加速。

[0177]

进一步地,虽然每个神经网络应用可以采用不同映射方法将其映射为迭代进行的低维矩阵的激活数据和权重数据的运算,但是发明人发现针对每个神经网络应用的固有特征,可以采用优选的映射方法,优选的映射方法相比其余映射方法,能够减少外部存储器与pe阵列之间的数据移动。例如,对于矩阵乘法,优选的映射方法是输入固定映射方法。

[0178]

本公开实施例的商业价值

[0179]

本公开实施例提供一种针对神经网络应用的新构思的指令集架构,以应用于神经网络模型的加速单元,这种加速单元在目前已有很多落地应用,即本公开实施例提供的加速单元具有现实的应用场景,因而具有市场前景和商业价值。

[0180]

本领域的技术人员能够理解,本公开可以实现为系统、方法和计算机程序产品。因此,本公开可以具体实现为以下形式,即完全的硬件、完全的软件(包括固件、驻留软件、微代码),还可以实现为软件和硬件结合的形式。此外,在一些实施例中,本公开还可以实现为一个或多个计算机可读介质中的计算机程序产品的形式,该计算机可读介质中包含计算机可读的程序代码。

[0181]

可以采用一个或多个计算机可读介质的任意组合。计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质。计算机可读存储介质例如但不限于为电、磁、光、电磁、红外线或半导体的系统、装置或器件,或其他任意以上的组合。计算机可读存储介质的更具体的例子包括:具体一个或多个导线的电连接,便携式计算机磁盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦除可编程只读存储器(eprom或者闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器、磁存储器或者上述任意合适的组合。在本文中,计算机可读的存储介质可以是任意包含或存储程序的有形介质,该程序可以被处理单元、装置或者器件使用,或者与其结合使用。

[0182]

计算机可读信号介质可以包括在基带中或者作为截波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或者其他任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质之外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令系统、装置或器件使用或者与其结合使用的程序。

[0183]

计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、电线、光缆、rf等等,以及上述任意合适的组合。

[0184]

可以以一种或者多种程序设计语言或者组合来编写用于执行本公开实施例的计算机程序代码。所述程序设计语言包括面向对象的程序设计语言,例如java、c ,还可以包括常规的过程式程序设计语言,例如c。程序代码可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算

机可以通过任意种类的网络包括局域网(lan)或广域网(wan)连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。

[0185]

以上所述仅为本公开的优选实施例,并不用于限制本公开,对于本领域技术人员而言,本公开可以有各种改动和变化。凡在本公开的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。