1.本发明涉及显示驱动芯片领域,具体是一种防止撕裂效应(tearing effect,te)的方法。

背景技术:

2.在以往传统的显示系统中,显示驱动芯片分为:没有内置帧存储器并以视频模式动作的显示驱动芯片,以及带有内置帧存储器并以命令模式动作的显示驱动芯片。

3.但是在显示条件功能要求日益复杂多样的现实下,即使是以命令模式动作的显示驱动芯片,也会发生在特定系统中需要使用视频模式动作的情况,以视频模式动作的系统中,也会发生需要使用显示驱动芯片内置帧存储器进行显示的情况。

4.例如,在以视频模式动作的系统中显示驱动芯片需要使用内部up-scaler的情况,或者虽然是视频模式,但为了减少系统整体的功耗,在图像没有变化时应用处理器(application processor,ap)以低帧率发送图像,显示驱动芯片需要先将其存储在内部存储器中,再以高于应用处理器发送的帧率进行显示的情况。

5.像这样在以视频模式动作的系统中,显示驱动芯片需要使用内置帧存储器进行显示的情况下,由于应用处理器和显示驱动芯片之间没有同步所需的te引脚,就会发生撕裂效应。

6.为了消除以视频模式动作的系统中发生的撕裂效应,需要在显示驱动芯片内部实现与应用处理器发送的图像同步的功能。

7.鉴于上述研究,提出了本发明申请。

技术实现要素:

8.本发明的目的是提供一种防止撕裂效应的方法,通过添加wait状态,使来自应用处理器的同步信号与显示驱动芯片内部产生的同步信号之间的时间差d始终保持不变,从而避免发生撕裂效应。

9.本发明采用的技术方案如下:

10.一种防止撕裂效应的方法,应用于显示驱动芯片,所述显示驱动芯片包括帧存储器、显示通道、以及向所述帧存储器和所述显示通道提供同步信号的同步信号产生器,所述防止撕裂效应的方法包括:检测到上电时序时,在所述同步信号产生器产生的同步信号中添加wait状态,所述wait状态自vactive状态结束时开始,且至收到来自外部应用处理器的vsync(vertical synchronization,垂直同步)时终止,所述上电时序为收到来自外部应用处理器的休眠命令时,所述显示驱动芯片为了进行显示,在内部进行调整电源状态的上电时序。

11.作为一种方案,只在上电时序之后的第一帧添加所述wait状态。

12.作为另一种方案,只在上电时序进行的帧内添加所述wait状态。

13.还有一种方案,在上电时序之后的每一帧均添加所述wait状态。

14.优选地,所述防止撕裂效应的方法还包括,在wait状态时,向显示面板发送用于生成黑色图像的图像数据。

15.与现有技术相比,本发明至少具有以下有益效果:

16.能够消除在视频模式下使用内置帧存储器的显示驱动芯片时产生的撕裂效应

附图说明

17.图1表示了在使用视频模式动作的系统中,使用带有内置帧存储器的显示驱动芯片时的外部接口与内部帧同步信号;

18.图2表示了视频模式接口与显示驱动芯片内部同步信号的常规动作;

19.图3表示了休眠后显示驱动芯片中生成的帧同步信号与通过mipi(mobile industry processor interface,移动行业处理器接口)输入的帧同步之间的时序关系;

20.图4表示了为了防止撕裂效应而提出的功能所包含的时序图。

具体实施方式

21.下面结合附图和实施例对本发明做进一步说明。

22.图1表示以视频模式动作的系统中,显示驱动芯片使用内置帧存储器时,帧同步是如何构成并动作的。通常,由于视频模式动作系统不使用帧存储器,所以直接使用通过外部接口进入的帧同步信号。

23.但是因某些特殊原因,显示驱动芯片内部必须使用帧存储器时,显示驱动芯片需要在内部生成帧同步信号使用,以进行显示动作。图中101表示mipi的视频模式接口信号,包括有pclk、vsync(vertical synchronization,垂直同步)、hsync(horizontal synchronization,水平同步)、de(有效数据选通)、rgb_data,其中的vsync、hsync、de作为帧同步信号。102表示显示驱动芯片内部生成的用来显示的帧同步信号,包括vsync、hsync、de。

24.图2表示了常规同步信号为传递显示数据的动作时序。

25.201表示从vsync到实际显示图像数据传送前的时序,用vbp(vertical back porch,垂直后沿)表示。

26.202表示在每个hysnc之间传送图像数据的active区间,用vactive表示。实际图像数据传送的时序上de信号是active状态。

27.203表示图像数据传送后,到下一个vsync之间的时序,用vfp(vertical front porch,垂直前沿)表示。

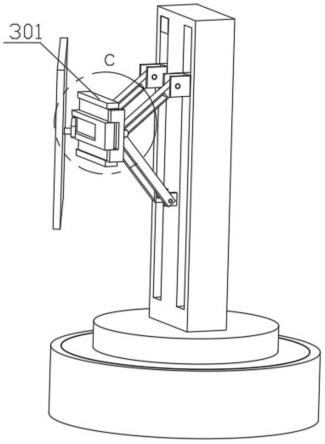

28.图3表示了应用处理器向显示驱动芯片发送休眠命令slpout 301后,通过mipi输入的vsync信号305与显示驱动芯片内部生成的vsync信号304之间的时序差异。

29.由于通过mipi输入的vsync信号305与显示驱动芯片内部生成的vsync信号304之间,没有使其时间同步的信号,导致两个信号之间的时间差异306是随机的,从而产生撕裂效应。

30.若应用处理器向显示驱动芯片发送休眠命令时,显示驱动芯片为了进行显示,在内部进行各种调整电源状态的上电时序。302表示此时的上电时序状态,该状态结束后,在之后的sleep_out状态303下运行实质的显示。

31.图4表示了本实施例防止撕裂效应的方法。

32.图中401表示应用处理器通过视频模式接口mipi发送的帧的周期,402表示显示驱动芯片内部的一个帧的周期。

33.由于在显示驱动芯片内部的帧率可以调节多个参数值,可设置成与应用处理器的帧率相同,因此都用同样的p来表示。图4假设显示驱动芯片内部的帧率与应用处理器发送的帧率相同。但是像这样仅让帧率配合一致,是无法防止撕裂效应的,因此本实施例提出了如下防止撕裂效应的方法。

34.如403所示,显示驱动芯片进入休眠状态后,在第一帧的vactive结束后,不进入vfp状态,而是进入wait状态。该wait状态一直等待,直到收到从mipi进入的vsync为止,也即当收到来自外部的应用处理器的vsync时终止,因此wait状态持续的时间不是固定的,而是可变的。

35.如404所示,在wait状态下,若收到从mipi进入的vsync,则会进入vfp状态。

36.如405所示,如此一来,该帧的周期就不是p,而是p wait,比其它帧更长。

37.使用该方法,通过mipi输入的帧同步信号,与显示驱动芯片内部生成的帧同步信号就可以保持一定的时间差异。

38.应用处理器也和显示驱动芯片一样,由于通过mipi重复vbp-vactive-vfp状态并传送数据,如406所示,在mipi接口中,vbp状态经过后进入vactive状态,输入图像数据,此时输入的数据开始存储在显示驱动芯片内部的帧存储器中。

39.由于显示驱动芯片在内部的同步信号的vactive状态下读取帧存储器的数据进行显示,因此如407所示,时间差d表示帧存储器开始写入数据的时间与帧存储器开始读取数据的时间差异。

40.在显示驱动芯片内部对调节帧率的参数值进行调节,决定mipi帧同步与内部帧同步值的差异d,使每帧的d值始终保持不变,即可避免发生撕裂效应。

41.虽然上述的撕裂效应可以防止,但是其它帧的周期都是p,增加wait状态的帧的周期是p wait,由于增加的周期可能会影响面板的动作,所以最好增加一个功能,在wait状态时,向显示面板发送用于生成黑色图像的图像数据,使面板显示黑色图像来代替mipi输入该帧的图像。

42.上述实施例中,以上电(power on)时序的结束为起点,且只在上电时序之后的第一帧添加wait状态,为最佳方案。

43.作为一种次佳的方案,是在上电时序进行的帧内添加wait状态,也可以使每帧的d值始终保持不变,从而可避免发生撕裂效应。

44.作为一种扩展方案,可在上电时序之后的每一帧均添加wait状态,通过添加在每一帧的wait状态,使每帧的d值始终保持不变,从而可避免发生撕裂效应。

45.应当理解,上述实施例中,以mipi接口作为视频模式接口仅为一种具体的例子,本方法同样适用于非mipi接口的一般rgb接口系统。

46.上述通过具体实施例对本发明进行了详细的说明,这些详细的说明仅仅限于帮助本领域技术人员理解本发明的内容,并不能理解为对本发明保护范围的限制。本领域技术人员在本发明构思下对上述方案进行的各种润饰、等效变换等均应包含在本发明的保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。