1.本发明涉及显示面板领域,特别涉及一种薄膜晶体管及其制备方法、显示面板。

背景技术:

2.在传统的铟镓锌氧化物(indium gallium zinc oxide,igzo)顶栅结构器件制作过程中,首先依次进行igzo的沉积及图案化、栅极绝缘层沉积、栅极层沉积后,进行栅极绝缘层和栅极层自对准的图案化。接下来,会利用等离子体(氢气或氦气或氩气)进行偏移区的导体化处理,这是因为沉积后的igzo是半导体态,电阻较大,源漏极通过过孔与igzo进行连接,而顶栅(top-gate)结构决定了栅极无法控制过孔部分的igzo,因此需要通过等离子体的轰击降低非栅极覆盖区的igzo的氧含量,从而降低电阻。导体化制程以后,则会进行层间介质层(氧化硅或氮化硅)的沉积,由于为了器件稳定性考虑,一般与igzo接触的介电层一般为氧化硅,因此,在沉积过程中,气体及膜层中的氧会渗入igzo层中,降低导体化的效果。

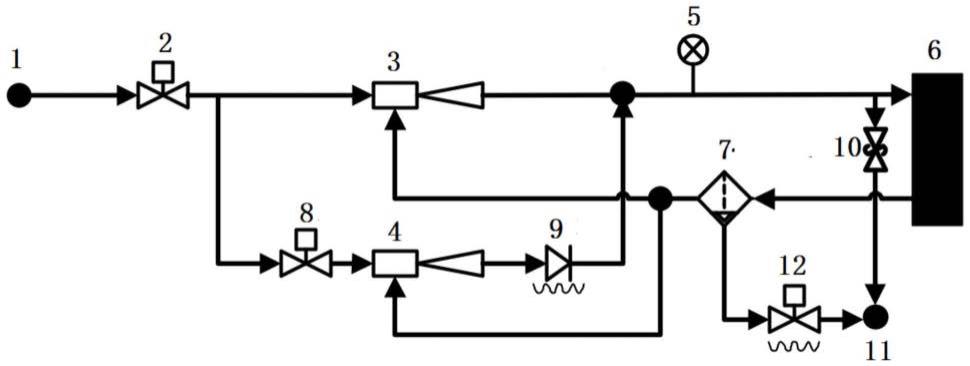

3.请参阅图1,图1为现有技术中薄膜晶体管900的结构示意图,薄膜晶体管900包括基板层910、缓冲层920、有源层930、栅极绝缘层940、栅极层950、层间介质层960、接触孔970和源漏极层980。有源层930包括偏移区9301和沟道区9302,偏移区9301的有源层930包括导体化区域931和氧渗透有源区932。

4.氧渗透有源区由于电阻升高会造成薄膜晶体器件有效迁移率降低,甚至由于氧渗透有源区的存在,很可能产生稳定性的问题。

技术实现要素:

5.本发明的实施例提供一种薄膜晶体管及其制备方法,用以解决现有技术中有源层导体化的效果差,进而导致的薄膜晶体管稳定性差的问题。

6.为了解决上述技术问题,本发明的实施例公开了如下技术方案:

7.一方面,提供一种薄膜晶体管包括:基板层;有源层、栅极绝缘层和栅极层,依次层叠设置在所述基板层上;所述有源层具有未被所述栅极层覆盖的偏移区,在所述偏移区的所述有源层包括相连接的沉积区和导体区,所述导体区的电阻至少小于一部分所述沉积区的电阻;层间介质层,设置在所述栅极层上,且覆盖所述有源层的所述沉积区;接触孔,从所述层间介质层远离所述基板层的一面延伸至所述有源层远离所述基板层的表面;所述接触孔暴露所述有源层的所述导体区。

8.除了上述公开的一个或多个特征之外,或者作为替代,所述薄膜晶体管包括:源漏极层,设置于所述层间介质层上,所述源漏极层穿过所述接触孔与所述有源层的所述导体区连接。

9.除了上述公开的一个或多个特征之外,或者作为替代,所述沉积区包括相连接的第一有源区和第二有源区,所述第二有源区位于所述偏移区靠近所述层间介质层的区域,所述第一有源区位于所述偏移区远离所述层间介质层的区域,所述第一有源区的电阻小于

所述第二有源区的电阻。

10.除了上述公开的一个或多个特征之外,或者作为替代,所述导体区位于所述偏移区靠近所述接触孔的区域,并且所述导体区与所述第一有源区相邻且接触,所述导体区与所述第二有源区相连接,所述导体区的电阻小于所述第二有源区的电阻。

11.另一方面,还提供一种制备方法,用于制备本发明涉及的薄膜晶体管,所述制备方法包括以下步骤:提供一基板层;在所述基板层上依次制备有源层、栅极绝缘层和栅极层,其中所述有源层具有未被所述栅极层覆盖的偏移区;对所述偏移区的所述有源层进行第一次导体化;制备层间介质层于所述栅极层上、且部分沉积于所述有源层的偏移区;在所述层间介质层上制备接触孔,所述接触孔从所述层间介质层远离所述基板层的一面延伸至所述有源层远离所述基板层的表面,所述偏移区的所述有源层裸露于所述接触孔中;对裸露于所述接触孔中的所述有源层进行第二次导体化,从而形成所述有源层的导体区,其中位于所述偏移区但处于所述导体区以外的区域为所述有源层的沉积区。

12.除了上述公开的一个或多个特征之外,或者作为替代,所述第一次导体化和所述第二次导体化采用等离子体处理的方式。

13.除了上述公开的一个或多个特征之外,或者作为替代,所述等离子体的气体包括氮气、氩气、氦气、氢气中的任意一种。

14.除了上述公开的一个或多个特征之外,或者作为替代,所述有源层的材料包括铟镓锌氧化物、铟锌锡氧化物、铟镓锌锡氧化物、铟锡氧化物、铟锌氧化物(izo)、铟铝锌氧化物、铟镓锡氧化物或锑锡氧化物中的任意一种。

15.除了上述公开的一个或多个特征之外,或者作为替代,制备所述有源层的步骤具体包括:采用化学气相的方式沉积有源层薄膜,对所述有源层薄膜图案化形成所述有源层。

16.除了上述公开的一个或多个特征之外,或者作为替代,所述栅极层的材料包括钼、铝、铜、钛中的任意一种所述对裸露于所述接触孔中的所述有源层的部分再次进行导体化的步骤后,还包括沉积源漏极层薄膜于所述层间介质层上及所述接触孔中,并对所述源漏极层薄膜进行图案化处理形成源漏极层,所述源漏极层通过所述接触孔与所述有源层连接。

17.除了上述公开的一个或多个特征之外,或者作为替代,所述层间介质层的材料采用氧化硅。

18.另一方面,还提供一种显示面板,包括阵列基板,所述阵列基板采用本发明涉及的所述薄膜晶体管。

19.上述技术方案中的一个技术方案具有如下优点或有益效果:在沉积层间介质层后对有源层增加一道二次导体化的制程,将暴露于接触孔处导体区的有源层的电阻降低,获得更好的电学连接特性,提高薄膜晶体管的稳定。

附图说明

20.下面结合附图,通过对本发明的具体实施方式详细描述,将使本发明的技术方案及其它有益效果显而易见。

21.图1为现有技术中提供的薄膜晶体管的结构示意图;

22.图2为本发明实施例提供的薄膜晶体管的结构示意图;

23.图3为本发明实施例提供的薄膜晶体管的制备方法的流程图;

24.图4为本发明实施例提供的薄膜晶体管的制备方法的步骤1的结构示意图;

25.图5为本发明实施例提供的薄膜晶体管的制备方法的步骤2的结构示意图;

26.图6为本发明实施例提供的薄膜晶体管的制备方法的步骤3的结构示意图;

27.图7为本发明实施例提供的薄膜晶体管的制备方法的步骤4的结构示意图;

28.图8为本发明实施例提供的薄膜晶体管的制备方法的步骤5的结构示意图;

29.图9为本发明实施例提供的薄膜晶体管的制备方法的步骤6的结构示意图;

30.图10为本发明实施例提供的薄膜晶体管的制备方法的步骤7的结构示意图;

31.图11为本发明实施例提供的薄膜晶体管的制备方法的步骤8的结构示意图。

32.背景技术中的附图标记:

33.薄膜晶体管-900;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板层-910;

34.缓冲层-920;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

有源层930;

35.栅极绝缘层-940;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极层-950;

36.层间介质层-960;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接触孔-970;

37.源漏极层-980;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

偏移区-9301;

38.沟道区-9302;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导体化区域-931;

39.氧渗透有源区-932;

40.具体实施方式中的附图标记:

41.薄膜晶体管-100;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板层-10;

42.缓冲层-20;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

有源层-30;

43.栅极绝缘层-40;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极层-50;

44.层间介质层-60;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接触孔-70;

45.源漏极层-80;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

偏移区-301;

46.沟道区-302;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一有源区-31;

47.第二有源区-32;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

沉积区-311;

48.导体区-33。

具体实施方式

49.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

50.本发明实施例提供一种薄膜晶体管100,请参阅图2,图2为薄膜晶体管100的结构示意图,薄膜晶体管100包括基板层10、缓冲层20、有源层30、栅极绝缘层40、栅极层50、层间介质层60、接触孔70和源漏极层80。

51.基板层10采用的材料可以为聚合物树脂,诸如聚醚砜(pes)、聚丙烯酸酯(par)、聚醚酰亚胺(pei)、聚萘二甲酸乙二酯(pen)、聚对苯二甲酸乙二酯(pet)、聚苯硫醚(pps)、聚

芳酯、聚酰亚胺(pi)、聚碳酸酯(pc)或醋酸丙酸纤维素(cap)。

52.缓冲层20设于基板层10上,缓冲层20的材料采用氮化硅、氧化硅或氮氧化硅,缓冲层20的厚度可以1000埃至5000埃之间。缓冲层20用于在遮光层上起平坦作用,方便后续对有源层30的制作。

53.有源层30设于缓冲层20上,有源层30具有未被栅极层50覆盖的偏移区301和被栅极层50覆盖的沟道区302,偏移区301的有源层30包括相连接的沉积区311和导体区33。沉积区311包括相连接的第一有源区31和第二有源区32,第二有源区32位于偏移区301靠近层间介质层60的区域,第一有源区31位于偏移区301远离层间介质层60的区域,导体区33位于偏移区301靠近接触孔70的区域,并且导体区33与第一有源区31相邻且接触,导体区33与第二有源区32相连接。第一有源区31的电阻小于第二有源区32的电阻,导体区33的电阻小于第二有源区32的电阻。有源层30的材料可以为铟镓锌氧化物(igzo)、铟锌锡氧化物(izto)、铟镓锌锡氧化物(igzto)、铟锡氧化物(ito)、铟锌氧化物(izo)、铟铝锌氧化物(iazo)、铟镓锡氧化物(igto)或锑锡氧化物(ato)中的任一种。

54.栅极绝缘层40设于有源层30上,栅极绝缘层40的材料采用氧化硅或氮化硅的无机层,并且可以包括单层或多个层。栅极绝缘层40的厚度介于1000埃至3000埃之间。

55.栅极层50设于栅极绝缘层40上,栅极层50可以是单层钼、单层铝、单层铜或单层钛,也可以是钼/铝/钼的叠层、铝/钼的叠层、铝/铜的叠层或钼钛合金/铜的叠层。栅极层50的厚度介于500埃至10000埃之间。

56.层间介质层60设于栅极层50上,且覆盖有源层30的沉积区311。层间介质层60采用氧化硅,层间绝缘层的厚度介于3000埃至10000埃。

57.接触孔70从层间介质层60远离基板层10的一面延伸至有源层30远离基板层10的表面,导体区33的有源层30裸露于所述接触孔70中。

58.源漏极层80设于层间介质层60上及接触孔70中,源漏极层80通过接触孔70与导体区33的有源层30连接。源漏极层80的材料可以为银、钼、铝、铜中的任意一种或多种。源漏极层80的厚度介于2000埃至10000埃之间。

59.本实施例还提供一种显示面板,包括阵列基板,阵列基板采用本发明实施例涉及的薄膜晶体管100。

60.本发明实施例还提供一种制备方法,用于制备本发明涉及的薄膜晶体管100,请参阅图3,图3为薄膜晶体管100的制备方法的流程图,制备方法包括步骤1-步骤8。

61.步骤1:提供一基板层10。

62.请参阅图4,图4为制备方法步骤1的结构示意图。

63.步骤2:制备缓冲层20于基板层10上。

64.请参阅图5,图5为制备方法的步骤2的结构示意图。

65.具体地,在基板层10上沉积缓冲层20,缓冲层20的材料采用氮化硅、氧化硅或氮氧化硅,缓冲层20的厚度可以1000埃至5000埃之间。

66.缓冲层20用于在遮光层上起平坦作用,方便后续对有源层30的制作。

67.步骤3:在基板层10上依次制备有源层30、栅极绝缘层40和栅极层50,有源层30具有未被栅极层50覆盖的偏移区301。

68.请参阅图6,图6为制备方法的步骤3的结构示意图。

69.具体地,在缓冲层20上采用化学气相的方式沉积有源层30薄膜,对有源层30薄膜图案化形成有源层30,有源层30的材料可以为铟镓锌氧化物(igzo)、铟锌锡氧化物(izto)、铟镓锌锡氧化物(igzto)、铟锡氧化物(ito)、铟锌氧化物(izo)、铟铝锌氧化物(iazo)、铟镓锡氧化物(igto)或锑锡氧化物(ato)中的任一种。以上材料具有很好的导电性和透明性,并且厚度较小,不会影响显示面板的整体厚度。同时,还可以减少对人体有害的电子辐射及紫外、红外光。有源层30的厚度介于100埃至1000埃之间。

70.在有源层30上采用化学气相的方式沉积栅极绝缘层40薄膜,对栅极绝缘层40薄膜图案化形成栅极绝缘层40,栅极绝缘层40的材料采用氧化硅或氮化硅的无机层,并且可以包括单层或多个层。栅极绝缘层40的厚度介于1000埃至3000埃之间。

71.在栅极绝缘层40上沉积采用化学气相的方式沉积栅极层50薄膜,对栅极层50薄膜图案化形成栅极层50,栅极层50可以是单层钼、单层铝、单层铜或单层钛,也可以是钼/铝/钼的叠层、铝/钼的叠层、铝/铜的叠层或钼钛合金/铜的叠层。栅极层50的厚度介于500埃至10000埃之间。

72.有源层30还具有被栅极层50覆盖的沟道区302。

73.步骤4:对未被栅极层50覆盖的偏移区301的有源层30进行第一次导体化。

74.请参阅图7,图7为制备方法的步骤4的结构示意图。

75.具体地,采用等离子体对有源层30未被栅极层50覆盖的偏移区301进行处理,形成n 导体区域,用于后续与源漏极相接,被栅极层50覆盖的沟道区302不做处理,作为薄膜晶体管100器件的沟道。等离子体的气体包括氮气、氩气、氦气、氢气中的任意一种。

76.步骤5:制备层间介质层60于栅极层50上、且部分沉积于有源层30的偏移区301。

77.请参阅图8,图8为制备方法的步骤5的结构示意图。具体地,在栅极层50、上沉积层间介质层60作为介电层,层间介质层60采用氧化硅。沉积的层间绝缘层的厚度介于3000埃至10000埃。

78.由于层间介质层60采用氧化硅,因此沉积层间介质层60的过程中,层间介质层60中的氧会渗入有源层30中,降低导体化的效果,偏移区301的有源层30形成相连接的第一有源区31和第二有源区32,第二有源区32位于偏移区301靠近层间介质层60的区域,第一有源区31位于偏移区301远离层间介质层60的区域,第一有源区31的电阻小于第二有源区32的电阻。在沉积层间介质层60的过程中,层间介质层60中的氧的渗入,导致第二有源区32的电阻增大,大于第一有源区21的电阻。第二有源区32的电阻增大进而会导致后续源漏极与有源层30的接触电阻会大幅度提高。

79.这会造成器件有效迁移率降低,甚至由于这部分电阻升高的第二有源区32的有源层的存在,很可能产生稳定性的问题。

80.步骤6:在层间介质层60上制备接触孔70,接触孔70从层间介质层60远离基板层10的一面延伸至有源层30远离基板层10的表面,偏移区301的有源层30裸露于接触孔70中。

81.请参阅图9,图9为制备方法的步骤6的结构示意图。

82.具体地,采用干法刻蚀的方式制备接触孔70,更利于后续对有源层30的二次导体化的进行。

83.步骤7:对裸露于接触孔70中的有源层30的进行第二次导体化,从而形成有源层30的导体区33,其中位于偏移区301但处于导体区33以外的区域为有源层30的沉积区311。

84.请参阅图10,图10为制备方法的步骤7的结构示意图。

85.具体地,采用等离子体对裸露于接触孔70中的有源层30进行处理,使得偏移区301的有源层30的二次导体化,裸露于接触孔70中的部分有源层30的电子会降低形成导体区33。导体区33位于偏移区301靠近接触孔70的区域,并且导体区33与第一有源区31相邻且接触,导体区33与第二有源区32相连接。

86.在沉积层间介质层60后对有源层30增加一道二次导体化的制程,将接触孔70处导体区33的有源层30的电阻重新降低,获得更好的电学连接特性,提高薄膜晶体管100的稳定。

87.步骤8:沉积源漏极层80薄膜于层间介质层60上及接触孔70中,并对源漏极层80薄膜进行图案化处理形成源漏极层80,源漏极层80穿过接触孔70与导体区33的有源层30连接。

88.请参阅图11,图11为制备方法的步骤8的结构示意图。

89.具体地,采用物理气相沉积源漏极层80薄膜,源漏极层80的材料可以为银、钼、铝、铜中的任意一种或多种。源漏极层80的厚度介于2000埃至10000埃之间。

90.本技术实施例对薄膜晶体管100的制作进行了示例性描述,可以理解的是,薄膜晶体管100中还可以包括其他装置。其他装置及其装配为本领域技术人员所熟知的技术手段,在此不再赘述。

91.以上对本发明实施例所提供的一种薄膜晶体管及其制备方法、显示面板进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例的技术方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。