1.本发明涉及电气设计技术领域,特别是一种基于国产器件的采集显示电路及其工作方法。

背景技术:

2.在工业控制及状态监视技术领域,通过rs422和ttl电平传输需要监视的信息极为常见,因此需要相应的电路对其进行采集检测并进行处理、显示和控制。fpga由于具有可编程、可重构、可多路并行处理等优势,使得其在采集检测电路中得到广泛应用。

3.目前现有的工业控制及状态监视产品基本都是基于进口器件,现有发明专利1(数字量采集电路及采集方法,申请号202010902689.2)和发明专利2(一种分机数据实时采集显示方法及系统,申请号202010946319.9),均基于国外器件进行设计,基于完全国产自主可控器件的采集显示电路尚未见到报道。

技术实现要素:

4.本发明的目的在于提供一种基于国产器件的采集显示电路及其工作方法。

5.实现本发明目的的技术解决方案为:一种基于国产器件的采集显示电路,包括fpga、flash、晶振、第一~第四电平转换收发器c1~c4、第一~第三rs422差分驱动器a1~a3、第一~第三电平保持器d1~d3、dc/dc电源、第一~第三ldo电源、第一~第六八段数码显示管、第一~第三对外接插件j1~j3、电容、电阻、电感和印制板;

6.所述dc/dc电源、第一~第三ldo电源用于为采集显示电路提供电源;

7.所述fpga用于控制采集显示电路的运行;

8.所述flash用于存储控制程序;

9.所述晶振用于提供100mhz的采样时钟;

10.所述第一~第二电平转换收发器c1~c2用于接收外界信号,第三~第四电平转换收发器c3~c4用于驱动第一~第六八段数码管进行显示;

11.所述第二~第三rs422差分驱动器a2~a3用于接收外界信号,第一rs422差分驱动器a1用于输出控制数据;

12.所述第一~第二电平保持器d1~d2用于接收外界信号,第三电平保持器d3用于输出控制电平;

13.所述第一~第六八段数码显示管用于显示采集到的信号。

14.进一步地,所述dc/dc电源将外部输入的dc24v滤波处理后产生dc5v;dc5v经过第一ldo电源、第二ldo电源处理分别产生dc3.3v和dc1.8v,经过第三ldo电源处理产生dc1v,产生的dc5v、dc3.3v、dc1.8v、dc1v经过多级滤波处理后供fpga、flash、晶振、第一~第四电平转换收发器c1~c4、第一~第三rs422差分驱动器a1~a3、第一~第三电平保持器d1~d3、第一~第六八段数码显示管使用。

15.进一步地,所述fpga上电后从flash读取初始化程序,从晶振采集100mhz采样时

钟,同时采集第一~第二电平转换收发器c1~c2、第一~第二电平保持器d1~d2、第二~第三rs422差分驱动器a2~a3接收的外界信号,根据采集到的信号和初始设置的显示逻辑控制第三~第四电平转换收发器c3~c4驱动六路八段数码管进行显示,同时根据初始设置的控制逻辑,输出对应控制电平经第三电平保持器d3输出,或输出对应控制数据经第一rs422差分驱动器a1输出。

16.进一步地,所述fpga为电路复旦微电子的jfmk50;所述flash为复旦微电子的jfm25f32a;所述晶振为北京晨晶的zpb-26-100mhz-3.3v;所述第一~第四电平转换收发器c1~c4为圣邦微电子的sgm8t245xts24g/tr;所述第一rs422差分驱动器a1为天水天光的er26c31s,第二、第三rs422差分驱动器a2~a3为天水天光的er26lv32s;所述第一~第三电平保持器d1~d3为深圳国微的sm708s;所述dc/dc电源为南京天仪航太的mac1805gle;所述第一ldo电源、第二ldo电源为北京伽略电子的ged1963bes8,第三ldo电源为深圳国微的sm74401rgw;所述第一~第六八段数码显示管为华城常半微电子的lcl002ii;所述第一~第三对外接插件j1~j3为贵州航天电器的j30j型对外接插件;所述电容为福建火炬电子的电容;所述电阻为振华云科的电阻;所述电感为株洲宏达电子的电感;所述印制板为杰赛科技的印制板。

17.进一步地,所述第一~第三对外接插件j1~j3将编写的fpga程序加载到配置的flash中,实现多种采集显示功能。

18.一种基于国产器件的采集显示电路的工作方法,包括以下步骤:

19.步骤1、dc/dc电源将外部输入的dc24v滤波处理后产生dc5v;dc5v经过第一ldo电源、第二ldo电源处理分别产生dc3.3v和dc1.8v,经过第三ldo电源处理产生dc1v;

20.步骤2、产生的dc5v、dc3.3v、dc1.8v、dc1v经过多级滤波处理后供fpga、flash、晶振、第一~第四电平转换收发器c1~c4、第一~第三rs422差分驱动器a1~a3、第一~第三电平保持器d1~d3、第一~第六八段数码显示管使用;

21.步骤3、fpga上电后从flash读取初始化程序,从晶振采集100mhz采样时钟,同时采集第一~第二电平转换收发器c1~c2、第一~第二电平保持器d1~d2、第二~第三rs422差分驱动器a2~a3接收的外界信号,根据采集到的信号和初始设置的显示逻辑控制第三~第四电平转换收发器c3~c4驱动六路八段数码管进行显示,同时根据初始设置的控制逻辑,输出对应控制电平经第三电平保持器d3输出,或输出对应控制数据经第一rs422差分驱动器a1输出;

22.步骤4、根据具体应用需求,将编写的fpga程序从fpga程序加载接插件加载到配置的flash中,该采集显示电路即实现新的采集显示功能。

23.本发明与现有技术相比,的显著优势在于:(1)可采集外界输入rs422接口信息和ttl接口信息,并通过八段数码管显示,同时可输出rs422接口信息和ttl接口信息;(2)使用rs422和ttl电平进行状态监控的装备,具有小型化、使用安装方便的优点;(3)所使用的全部元器件均为国产化产品,具有良好自主可控性。

附图说明

24.图1是采集显示电路总体框图

25.图2是本发明一种基于国产器件的采集显示电路的结构示意图。

26.图3是本发明中电源单元的结构示意图。

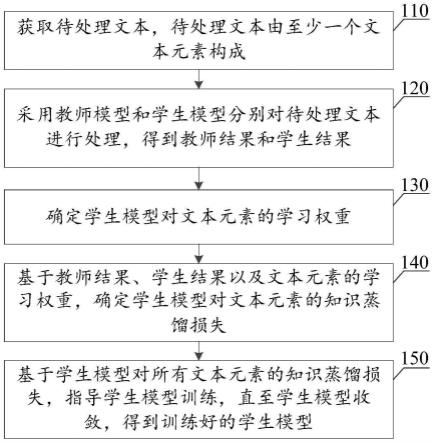

27.图4是本发明实施例中某具体应用工作的流程示意图。

具体实施方式

28.下面结合附图和具体实施例对本发明作进一步的详细说明。

29.结合图1~图2,本发明一种基于国产器件的采集显示电路,包括fpga、flash、晶振、第一~第四电平转换收发器c1~c4、第一~第三rs422差分驱动器a1~a3、第一~第三电平保持器d1~d3、dc/dc电源、第一~第三ldo电源、第一~第六八段数码显示管、第一~第三对外接插件j1~j3、电容、电阻、电感和印制板;

30.所述dc/dc电源、第一~第三ldo电源用于为采集显示电路提供电源;

31.所述fpga用于控制采集显示电路的运行;

32.所述flash用于存储控制程序;

33.所述晶振用于提供100mhz的采样时钟;

34.所述第一~第二电平转换收发器用于接收外界信号,第三~第四电平转换收发器用于驱动第一~第六八段数码管进行显示;

35.所述第二~第三rs422差分驱动器用于接收外界信号,第一rs422差分驱动器用于输出控制数据;

36.所述第一~第二电平保持器用于接收外界信号,第三电平保持器用于输出控制电平;

37.所述第一~第六八段数码显示管用于显示采集到的信号。

38.作为一种具体示例,所述dc/dc电源将外部输入的dc24v滤波处理后产生dc5v;dc5v经过第一ldo电源、第二ldo电源处理分别产生dc3.3v和dc1.8v,经过第三ldo电源处理产生dc1v,产生的dc5v、dc3.3v、dc1.8v、dc1v经过多级滤波处理后供fpga、flash、晶振、第一~第四电平转换收发器c1~c4、第一~第三rs422差分驱动器a1~a3、第一~第三电平保持器d1~d3、第一~第六八段数码显示管使用。

39.作为一种具体示例,所述fpga上电后从flash读取初始化程序,从晶振采集100mhz采样时钟,同时采集第一~第二电平转换收发器c1~c2、第一~第二电平保持器d1~d2、第二~第三rs422差分驱动器a2~a3接收的外界信号,根据采集到的信号和初始设置的显示逻辑控制第三~第四电平转换收发器c3~c4驱动六路八段数码管进行显示,同时根据初始设置的控制逻辑,输出对应控制电平经第三电平保持器d3输出,或输出对应控制数据经第一rs422差分驱动器a1输出。

40.作为一种具体示例,所述fpga为电路复旦微电子的jfmk50;所述flash为复旦微电子的jfm25f32a;所述晶振为北京晨晶的zpb-26-100mhz-3.3v;所述第一~第四电平转换收发器c1~c4为圣邦微电子的sgm8t245xts24g/tr;所述第一rs422差分驱动器a1为天水天光的er26c31s,第二、第三rs422差分驱动器a2~a3为天水天光的er26lv32s;所述第一~第三电平保持器d1~d3为深圳国微的sm708s;所述dc/dc电源为南京天仪航太的mac1805gle;所述第一ldo电源、第二ldo电源为北京伽略电子的ged1963bes8,第三ldo电源为深圳国微的sm74401rgw;所述第一~第六八段数码显示管为华城常半微电子的lcl002ii;所述第一~第三j1~j3对外接插件为贵州航天电器的j30j型对外接插件;所述电容为福建火炬电子的

电容;所述电阻为振华云科的电阻;所述电感为株洲宏达电子的电感;所述印制板为杰赛科技的印制板。

41.作为一种具体示例,所述第一~第三对外接插件j1~j3可以将新编写的fpga程序加载到配置的flash中,实现多种采集显示功能。

42.作为一种具体示例,图3为本发明采集电路中的电源单元原理图,图中外界输入的dc24v经滤波处理输入至n1,产生dc5v,经滤波处理后分别供n2、n3、n4进行再次转换后产生dc3.3v、dc1.8v和dc1v,本采集显示电路外界供电需求为dc24v,经n1、n2、n3、n4转换后产生全部的内部用电需求。

43.本发明一种基于国产器件的采集显示电路的工作方法,包括以下步骤:

44.步骤1、dc/dc电源将外部输入的dc24v滤波处理后产生dc5v;dc5v经过第一ldo电源、第二ldo电源处理分别产生dc3.3v和dc1.8v,经过第三ldo电源处理产生dc1v;

45.步骤2、产生的dc5v、dc3.3v、dc1.8v、dc1v经过多级滤波处理后供fpga、flash、晶振、第一~第四电平转换收发器c1~c4、第一~第三rs422差分驱动器a1~a3、第一~第三电平保持器d1~d3、第一~第六八段数码显示管使用;

46.步骤3、fpga上电后从flash读取初始化程序,从晶振采集100mhz采样时钟,同时采集第一~第二电平转换收发器c1~c2、第一~第二电平保持器d1~d2、第二~第三rs422差分驱动器a2~a3接收的外界信号,根据采集到的信号和初始设置的显示逻辑控制第三~第四电平转换收发器c3~c4驱动六路八段数码管进行显示,同时根据初始设置的控制逻辑,输出对应控制电平经第三电平保持器d3输出,或输出对应控制数据经第一rs422差分驱动器a1输出;

47.步骤4、根据具体应用需求,将编写的fpga程序从fpga程序加载接插件加载到配置的flash中,该采集显示电路即实现新的采集显示功能。

48.下面结合具体实施例对本发明做进一步详细说明。

49.实施例1

50.结合图4,本实施例为本发明的采集显示电路在某侦察装备中的具体应用工作流程图,结合图2,第二rs422差分驱动器a2接收侦察装备温度传感器输入的温度rs422电平信号和湿度传感器输入的湿度rs422电平信号并输入fpga,第三rs422差分驱动器a3接收侦察装备接收机输入的rs422差分电平形式的pdw信息并输入fpga,第一电平转换收发器c1接收侦察装备内部风机故障信息ttl电平信号,并输入fpga;

51.fpga进行检测并判断温度、湿度是否超门限值,风机是否故障,如果超门限值通过第一rs422差分驱动器a1给上位机发rs422电平告警信息;fpga检测到风机故障通过第四电平转换收发器c4给声光告警设备输出ttl单端高电平。

52.在侦察设备无外界按键控制时,该电路按照pdw、温度、湿度固定时间片的方式进行循环显示,当fpga检测到图2中第一电平保持器d1收到开关电平信号时,进入单次选择模式,外界开关第一次按下显示pdw,第二次按下则显示温度,第三次按下则显示湿度,第四次按下则按照时间片循环显示;当fpga检测到图2中第二电平保持器d2收到按键信号后,如果当前显示的pdw,则按外界按键每下一次则分别显示方位、载频、脉宽、幅度,单独显示完后则循环显示;如果当前在显示温度或湿度则不起作用。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。