用于更新显示装置上显示的图像的系统和方法

1.相关申请

2.本技术要求2020年1月8日提交的美国临时申请第62/958,627号的权益。该申请的全部内容通过引入并入本文。

技术领域

3.本公开内容涉及显示器。更具体地,本公开内容涉及更新显示装置上显示的图像,这样的显示装置包括空间光调制器和/或显示器,诸如液晶显示器、硅上液晶(lcos)显示器、led显示器、微型led显示器和微型显示器,这些显示器由显示驱动器电路系统和/或软件(例如,电路系统、逻辑部件或电路系统、ic和/或驱动软件)进行驱动。

背景技术:

4.在诸如增强现实(ar)头戴式显示器的移动系统中,功耗和电池使用率至关重要。在这些系统中,主机(例如,诸如电话、计算机、平板电脑或其他移动装置的视频源)上的视频数据的生成(渲染)、所述数据(例如,通过线缆)的传输以及所述视频数据在显示驱动器ic和一个或多个背板ic中的处理/加载都消耗流水线中硬件的每一位中传输或切换的每一位的功率。这些系统从主机的帧缓冲器发送整个数据帧,包括要显示的未更改的数据和更改的数据。例如,一些系统可能仅渲染正在显示的图像的变化部分并将这些变化部分写至主机上的帧缓冲器,而然后将整个帧发送至显示子系统。此外,这些系统还采用固定的刷新率。部分地由于这种重复和专用于通过系统进行的数据传输的功率浪费,已知技术和常规系统目前在提供还使电池重量和体积最小化的重量轻、使用时间长的系统方面存在不足。

5.这样的具有用于渲染图像帧数据的数据源或主机的已知显示系统渲染并传输来自帧缓冲器的整个图像帧数据,以用于更新整个显示器的当前显示的图像。这包括在两个图像帧之间发送重复的或未更改的数据。该数据可以是例如视频、图像或表征图像的图像数据。显示器可以是微型显示器诸如lcd或lcos微型显示器,或者是直视型的较大显示器。

技术实现要素:

6.在本发明的实施方式中,提供了用于更新显示在显示装置上的图像的显示系统,所述显示装置包括像素阵列中的像素,所述系统包括:用于执行命令的显示子系统,其中,命令指示显示子系统如何更新显示器,所述显示子系统包括:解析器,其用于接收图像帧数据,其中,解析器提取更新的图像数据和命令;存储装置,其用于根据命令将更新的图像数据存储在更新的高速缓冲存储器位置中;加载器,其用于读取命令以从存储装置识别和提取更新的图像数据;以及显示背板电路系统,其用于从加载器接收更新的图像数据,并用于针对更新的图像数据内的像素来更新像素驱动器电路系统。

7.在本发明的实施方式中,提供了更新显示在显示装置上的图像的方法,所述显示装置包括像素阵列中的像素,所述方法包括以下步骤:在显示子系统中接收图像帧数据;在解析器中接收图像帧数据,该解析器从图像帧数据中提取更新的图像数据和相关联的命

令,所述图像帧数据包括指示加载器如何更新显示器的命令;根据命令将更新的图像数据存储在更新的高速缓冲存储器位置中;读取命令以从更新的高速缓冲存储器位置识别和提取更新的图像数据;从加载器接收更新的图像数据;以及针对仅在更新的图像数据内的像素更新像素驱动器电路系统。

8.在本发明的实施方式中,存储装置可以包括高速缓冲存储器存储器。高速缓冲存储器或存储装置可以是诸如ram、eeprom等的物理存储器,或者可以是基于软件的高速缓冲存储器存储器或存储装置。

9.在本发明的实施方式中,提供了用于更新显示在显示装置上的图像的显示系统,所述显示装置具有包括像素阵列中的像素的显示器,所述系统包括:用于执行命令的显示子系统,其中,所述命令包括:用于显示装置的描述如何根据更新的图像帧数据来更新显示器的指令,所述显示子系统包括用于接收更新的图像帧数据的解析器,其中,解析器提取更新的图像数据和命令;用于存储装置的描述如何将更新的图像数据存储在更新的高速缓冲存储器位置的指令;用于加载器的描述如何从高速缓冲存储器位置识别和提取更新的图像数据的指令;以及显示背板电路系统,其用于从加载器接收更新的图像数据,并用于针对更新的图像数据内的像素来更新像素驱动器电路系统。

10.在根据本发明的系统中,显示背板部分仅将数据重新加载到显示器的一部分中,而使所有其他像素的状态保持静态。这通过以下方式实现:通过利用定义块308中的列的水平范围的关于列的每一组的一个或更多个列定向加载使能信号(例如,激活或去激活(启用或禁用)像素分组的控制电压),使显示器通过寻址像素的分组(例如,显示器的像素中的像素的小矩形块或子集或者显示器的像素中的像素的块的集合或子集)来加载其像素,所述一个或更多个列定向加载使能信号与行定向加载信号(例如,控制电压)结合工作,以启用或禁用将新的数据加载到像素的块308内的像素中。

11.在本发明的实施方式中,一种用于更新显示在显示装置上的图像的显示系统,所述显示装置可以包括像素阵列中的像素,并且所述系统包括用于执行命令的显示子系统,其中,命令指示加载器如何更新显示器,所述显示子系统包括:用于接收图像帧数据的解析器,其中,解析器提取更新的图像数据和命令,所述命令包括识别显示器中要更新或不更新的部分的命令;由数据的集合组成的图,其中,数据的集合包括指示显示器中的活动和需要更新的区域的坐标和块位置中的至少之一(例如,显示器中的位置的坐标、或显示器中的像素或像素元件的位置、或显示器中的像素或像素元件的块的位置或坐标、或对应的图像或图像数据中的位置);存储装置,其用于根据命令将更新的图像数据存储在存储装置、更新的存储位置或高速缓冲存储器中,所述存储装置例如可以基于图的内容选择性地存储或确定传入数据将被存储在哪里;加载器,其用于读取命令,以从存储装置、更新的存储位置或高速缓冲存储器中识别和提取更新的图像数据,并且加载器可以根据图选择性地提取数据;以及显示背板电路系统,其用于从加载器接收更新的图像数据,并用于针对更新的图像数据内的像素来更新像素驱动器电路系统。在本发明的实施方式中,一种用于更新显示在显示装置上的图像的显示系统,所述显示装置包括像素阵列中的像素,所述系统包括:用于接收图像帧数据的解析器,其中,解析器提取更新的图像数据和命令,所述命令包括识别显示器中用于更新的部分的命令;由数据的集合组成的图,其中,数据的集合包括显示器的用于更新的活动区域的坐标和块位置中的至少之一;存储装置,其用于基于命令和图中的至

少之一来存储更新的图像数据;加载器,其用于读取命令,并且其中,加载器识别更新的图像数据,并且根据图从存储装置提取更新的图像数据;以及显示背板电路系统,其用于从加载器接收更新的图像数据,并用于更新像素驱动器电路系统,该像素驱动器电路系统使用更新的图像数据来更新像素。

12.在实施方式中,命令包括描述符,该描述符标识更新的图像数据示出了图像的相应部分的哪个位置。在实施方式中,解析器执行以下操作中的至少一项:将命令发送至存储装置以及/或者将命令发送至加载器。在实施方式中,加载器读取描述符并从更新的存储位置提取更新的图像数据。在实施方式中,加载器识别像素阵列中与描述符中的位置相对应的像素行和/或像素列。在实施方式中,加载器对描述符的读取进行排队直到加载器从存储装置提取数据。在实施方式中,加载器对描述符的读取进行排队,以以预定间隔发生。在实施方式中,该系统还包括图像源,并且其中,该图像源识别显示器中要更新的位置,并且仅针对该位置渲染更新的图像数据。在实施方式中,图像源是视频数据源,并且其中,更新的图像数据被存储在存储器和缓冲器中的至少一个中。在实施方式中,存储器和缓冲器中的至少一个是缓冲器,并且存储在缓冲器中的更新的图像数据被传输至显示系统,并且其中,显示系统包括驱动器显示逻辑,该驱动器显示逻辑用于根据更新的图像数据来计算显示器的活动区域的占用图。在实施方式中,显示器的区域包括显示器的像素、像素的行和像素的部分像素中的至少之一的矩形图块。在实施方式中,占用图通过分析显示器的区域中是否存在任何非黑色的像素来确定活动区域。在实施方式中,仅非黑色的数据被写入存储装置。在实施方式中,从存储装置中检索仅与显示器的活动区域相对应的更新的图像数据。在实施方式中,显示系统包括像素阵列,并且包含像素的像素阵列中的每个像素包括:耦接至像素逻辑电路系统的像素元件;以及耦接至像素逻辑电路系统的像素存储器。在实施方式中,存储元件存储像素的当前灰度值。在实施方式中,像素还包括像素驱动电路系统。在实施方式中,像素逻辑电路系统对当前灰度值进行解码,并调制像素驱动电路系统,并生成像素强度和亮度中的至少一个。在实施方式中,存储器元件包括锁存器电路系统,该锁存器电路系统用以存储由多个位表示的针对该像素的图像数据。在实施方式中,该系统还包括图像源,其中,所述图像源执行以下操作中的至少一项:渲染所述图像帧数据以及传输所述图像帧数据,该图像帧数据包括:图像的至少一部分的更新的图像数据,所述更新的图像数据用以替换当前显示的图像的图像数据的相应部分;以及描述更新的图像数据如何替换图像数据的相关联的命令。在实施方式中,存储装置是高速缓冲存储器存储器。在实施方式中,一种更新显示在显示装置上的图像的方法,所述显示装置包括像素阵列中的像素,该方法包括以下步骤:在显示子系统中接收图像帧数据;在解析器中接收图像帧数据,该解析器从图像帧数据中提取更新的图像数据和相关联的命令,所述图像帧数据包括指示加载器如何更新显示器的命令;根据命令将更新的图像数据存储在更新的高速缓冲存储器位置;读取命令以从更新的高速缓冲存储器位置识别和提取更新的图像数据;从加载器接收更新的图像数据;以及针对仅在更新的图像数据内的像素来更新像素驱动器电路系统。

13.本发明的装置、系统和方法通过优化数据(例如,视频、图像、视频数据/图像数据)的渲染、传输和刷新来节省显示系统中的功率。在本文中,本发明的实施方式允许在每个阶段仅改变正在改变的内容,即,选择性地仅刷新相对于整个先前的帧或子帧需要改变的数据部分以及非空白的那些部分。因此,仅这些变化的或活动的部分被渲染、传输和刷新,而

图像或图像数据的其他部分保持不变或不被显示驱动器电路系统和/或软件改变。根据本文中的实施方式,这种选择性的刷新可以发生在流水线的一个或更多个阶段,即可以发生在显示器的主机渲染、传输和/或更新期间。

14.作为使发送的数据量以及随后在流水线的多个阶段处理、传输和刷新的数据量最小化(例如,不发送完整的视频帧)的结果,整个系统提高了效率,并降低使用这样的显示系统和方法的相关联的装置的电池尺寸和功耗。这些节省(例如,更小的电池和更小/更轻的移动系统)对于需要更长的电池寿命的应用(诸如包括ar、vr等的头戴式系统)来说是理想的。此外,本文中的实施方式对于驱动显示器(例如,液晶显示器、lcos显示器、led显示器、微型led显示器)是理想的。在本发明的实施方式中,显示驱动器电路系统和/或软件可以被集成、包括或耦接至显示器,以形成单个装置(例如,具有包括显示驱动器ic的硅背板的显示装置(显示装置可以被接合或以其他方式耦接至背板))。在本发明的实施方式中,显示器可以与显示驱动器电路系统和/或软件(例如,显示驱动器ic)分离,并且例如经由柔性线缆、电线或电连接器元件电耦接至显示装置。可以使用术语“耦接”和“连接”以及其派生词。应理解,这些术语并不旨在彼此作为同义词。而是,在特定实施方式中,“连接”可以用于指示两个或更多个元件彼此直接物理接触。“耦接”可以意指两个或更多个元件直接物理接触。然而,“耦接”也可以意指两个或更多个元件彼此不直接接触,但仍然彼此协作或相互作用。

15.在审查以下附图、具体实施方式和权利要求书之后,将更充分地理解所公开的主题的这些和其他能力。应当理解,本文中采用的措辞和术语是出于描述的目的,而不应被认为是进行限制。

附图说明

16.本文参照各种附图说明和描述本公开内容,在附图中,相同的附图标记用于适当地表示相同的系统部件,并且在附图中:

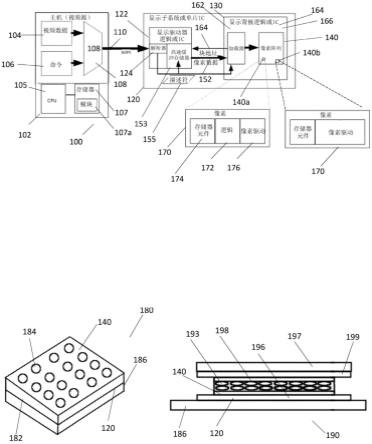

17.图1a示出了根据本发明的系统及其部件的框图。

18.图1b示出了并入图1a的系统的微型led显示系统。

19.图1c示出了并入图1a的系统的lcos显示系统。

20.图2是根据本发明的实施方式显示的示例性图像的图示。

21.图3是根据本发明的实施方式的被划分为活动区域和非活动区域的图像的图示。

22.图4示出了根据本发明的方法。

具体实施方式

23.图1a示出了诸如主机的数据源102的说明性框图,例如图像、图像数据或视频源或视频数据104。在本发明的实施方式中,主机可以包括处理器105,例如应用处理器,该处理器105执行存储在主机的存储装置(例如,存储器装置107)中的应用、指令或命令106(例如,软件)。在本发明的实施方式中,主机可以经由例如耦接至主机或包含在主机中的中央处理单元、图形处理单元、显示处理单元、dma引擎、mipi dsi控制器和mipi phy接口来流式传输图像数据或图像(例如视频数据)。在本发明的实施方式中,软件模块107a包括命令106。

24.图1b是微型led显示系统180的图示,在实施方式中,该微型led显示系统180可以

包括本发明的显示系统100。微型led显示系统180通常包括布置在基板182上的单个像素led元件184的像素阵列140。在本发明的实施方式中,基板182可以耦接至驱动器背板或背板ic 186、可以与驱动器背板或背板ic 186集成或者可以形成在驱动器背板或背板ic 186上。在本发明的实施方式中,像素led元件被直接布置在驱动器背板或背板ic 186上。在本发明的实施方式中,驱动器背板或背板ic 186包括用以驱动像素阵列140的电路系统,例如显示驱动器逻辑122或集成电路和/或显示背板逻辑130或集成电路。显示驱动器逻辑122可以包括解析器124和/或高速缓冲存储器或存储装置153。显示背板逻辑130可以包括加载器162。还可以提供描述符152。还可以提供像素阵列140的像素的像素驱动电路系统170。

25.类似地,图1c是具有类似元件的lcos显示系统190的图示,并且在实施方式中,该lcos显示系统190也可以包括本发明的显示系统100。特别地,lcos显示装置包括基板120,显示背板或显示驱动背板ic 186可以耦接至基板120或与基板120集成。基板120是硅。单独的反射装置的层196被布置、耦接至显示背板120或者与显示背板120集成,所述单独的反射装置可以是诸如镜或铝装置的单独的反射装置(此处表示为单个层)。在层196的顶部上形成取向层140。液晶层193、取向层198、透明电极(通常在铟锡氧化物层内)199和玻璃或其它透明材料层197形成也形成显示器的结构。

26.在本发明的实施方式中,显示背板ic 130可以被包括、并入或集成在显示背板120中(该显示背板120可以耦接至例如lcos显示系统中的反射装置186;196或者led诸如微型led显示系统中的微型led)。像素阵列(即,微型led或led)可以在其自己的基板上,其中每个led被耦接至背板上的像素驱动器。在本发明的实施方式中,显示背板120被耦接至显示装置180、190(例如,lcos装置)或lcos像素阵列140或像素元件(例如,反射装置186;196或led或led阵列,例如微型led)。在本发明的实施方式中,显示装置100包括显示背板120、显示背板电路系统130、像素电路系统174(例如,作为像素驱动电路系统或像素电路)以及像素元件140a,所述像素元件140a被耦接(例如,电耦接)至ddic 122、集成到、包括在和/或定位在ddic 122中。在本发明的实施方式中,显示装置100(包括ddic 122)被电耦接至ddic,并且形成显示子系统120,并且被一起组装在显示模块100中。

27.在本发明的实施方式中,显示子系统120包括显示器197。在本发明的实施方式中(诸如图1c中所示),显示器197是布置在背板120上或耦接至背板电路系统(例如,像素电路系统170、像素驱动电路系统或被并入、集成到背板中或耦接至背板的驱动电路系统)的像素元件140的阵列。在本发明的实施方式中,显示子系统120是硅上液晶(lcos)显示系统190的lcos显示子系统。在根据本发明的lcos系统190的实施方式中,显示器197是液晶显示器或液晶单元(包括放置在两个基板196、199之间的液晶193),被电耦接至显示子系统的背板120或背板ic或者与显示子系统的背板120或背板ic集成。在本发明的实施方式中,液晶显示器或单元的基板196之一是背板120或背板ic。在本发明的实施方式中,液晶显示器或液晶单元193被包括在、集成在显示背板集成电路130(ic)或其基板中或电耦接至显示背板集成电路130(ic)或其基板。在本发明的实施方式中,显示背板ic 130被电耦接至液晶单元的侧部中之一,例如被电耦接至显示器的不发射光或与图像对应的光的侧部。在本发明的实施方式中,液晶单元被耦接至硅基板182,并且该基板是形成显示背板ic 120的一个侧部的相同硅基板或者是耦接至显示背板ic的基板(例如,基板,诸如包括驱动电路系统、像素电路系统、像素电路170和/或驱动电路166的硅基板)的硅基板。

28.在本发明的实施方式中(诸如图1b中所示),显示子系统120是微型led显示子系统180。在本发明的实施方式中,显示子系统100是微型led系统180。在根据本发明的微型led子系统180的实施方式中,显示器是led 184或微型led的阵列,该阵列被电耦接至显示子系统100的背板120或显示背板ic、或者被集成到显示子系统100的背板120或显示背板ic中、或者与显示子系统100的背板120或显示背板ic集成。在本发明的实施方式中,微型led 184的阵列被包括、集成到显示背板集成电路(ic)122和/或其基板182中或电耦合至显示背板集成电路(ic)122和/或其基板182。在本发明的实施方式中,显示背板ic 122被电耦接至led(例如,微型led)的阵列的侧部中之一,例如被电耦接至led(例如,微型led)的阵列的不发射光或与图像对应的光的侧部。在本发明的实施方式中,led 184(例如,微型led)的阵列被耦接至硅基板182,并且该基板是形成显示背板ic 122的一个侧部的相同硅基板,或者是耦接至显示背板ic 122的基板186(例如,显示背板ic的硅基板)的硅基板182。

29.在本发明的实施方式中,像素184的阵列包括组装在阵列140中的像素元件或在阵列中组装在基板182上的像素元件。在本发明的实施方式中,像素阵列180是发光二极管(led)的阵列。在本发明的实施方式中,led可以是微型led。在本发明的实施方式中,像素元件184的阵列140是控制lcos装置190或其他液晶装置中的液晶193的双折射的反射元件196的阵列。在本发明的实施方式中,像素元件184是反射元件/装置,例如镜。在本发明的实施方式中,像素阵列140或像素的阵列被形成在、并入到、集成到显示背板ic 122中或耦接至显示背板ic 122。在本发明的实施方式中,ddic或显示驱动器电路系统驱动布置在显示子系统100的背板120上的像素元件的阵列的像素元件(例如,发光二极管(led)、微型led 184、反射元件)的操作。

30.在本发明的实施方式中,数据源或主机可以是例如移动装置,诸如智能电话、平板电脑、膝上型电脑、抬头显示系统、头戴式装置或混合装置(或上述装置的某种组合)。在本发明的实施方式中,图像、图像数据和/或视频数据由主机102的实时数据软件模块107a和/或mux 108接收,并且实时数据软件或软件模块107a在多路复用器(mux)108和/或实时数据软件模块107a处将数据与从包含期望的驱动序列的主序列文件解析的命令进行组合。另外地或可替选地,mux 108可以是由实时数据软件模块107a控制的硬件。在本发明的实施方式中,与命令组合的数据是从数据源(例如,主机)102输出并传输到显示子系统的组合数据。在本发明的实施方式中,经由数据源102的实时数据软件模块107a和/或mux 108输出组合数据。

31.与已知系统相比,本文中的实施方式的数据源或主机102渲染并传输各帧之间的数据104的已经更改的部分,而不是所有的图像数据(即,更改的数据和未更改的数据)。在本发明的实施方式中,由主机传输的唯一图像数据是各帧之间的已经更改的数据部分,并且将该更改的图像数据连同一个或更多个命令106从主机102传输至显示器197或显示背板130和/或驱动器电路系统122和/或用于驱动显示背板130的软件。这种节省可以发生在将在下面更详细描述的五个阶段处:1)将数据从主机102传输至显示器197;2)将数据放入高速缓冲存储器153中;3)从高速缓冲存储器153中读取数据;4)经由显示加载器162将数据从高速缓冲存储器153写入显示器130中;以及5)调制显示器197的活动像素。本发明的实施方式利用了在诸如ar系统的系统应用中呈现的图像的性质,其通常具有稀疏的图像数据(因为图像被覆盖在真实世界上),所述稀疏的图像数据具有高比例的黑色背景,该黑色背景在

ar头戴式显示器中变得透明。根据本发明的实施方式,可能存在可能需要刷新整个显示区域以及将数据传输到显示器的线缆上的全部数据带宽的情况,例如,当正在呈现全运动视频时或者当用户正在移动并且图形正在被更新以与用户的真实世界有利位置对准时。在本发明的实施方式中,显示器197可以在某些区域(诸如沿着显示器的底部边缘、顶部边缘或侧部边缘的条带,而中心区域是空白的)示出图标、图形或文本,并且这些可以是静态的或偶尔变化的,并且在这些类型的情况下,根据本发明,发送各帧之间的已经更改的数据部分而不是所有的图像数据(即,更改的数据和未更改的数据)是有利的,因为这例如节省了功率。根据本发明的实施方式,数据104也可以是正在移动的符号、图标或指示符,但相对于整个显示区域较小并因此仅需要更新该区域的子集。对于小区域刷新的情况,在运动需要快速以跟上环境的变化的情况下,也可以增加刷新率,这是因为可用的时间和传输带宽可以完全专用于显示器的变化部分。本发明解决了流水线的多个阶段处的数据处理、传输和刷新的最小化。在一个实施方式中,整个显示器在不刷新整个高速缓冲存储器的情况下被刷新,而在另一实施方式中,整个显示器从高速缓冲存储器开始被刷新。在本发明的实施方式中,加载器162可以从高速缓冲存储器153仅提取或读取更改的数据,并刷新或更新显示器197。可替选地,例如,加载器162可以利用或读取高速缓冲存储器153中的全部内容或图像数据——而不是从高速缓冲存储器153仅读取更改的数据——来刷新或更新显示器197以更新或刷新显示器197。

32.根据本发明的实施方式的显示子系统120的显示背板部分130并入了仅将数据重新加载到显示器的一部分中同时使所有其他像素140的状态保持静态的能力。这在图3中示出并且通过以下方式实现:通过具有定义块308中的列的水平范围的关于列301的每一组的列定向加载使能信号或启用或禁用的控制电压,使显示器300通过寻址显示器的像素140a、140b中的像素的小矩形块308或子集或者显示器的像素中的像素的块的集合或子集来加载其像素,所述列定向加载使能信号或启用或禁用的控制电压与行定向加载信号或控制电压结合工作,以启用或禁用将新的数据加载到像素的块308内的像素中。在本发明的实施方式中,像素140a并入了足够的存储器174(例如,诸如锁存器或锁存器电路系统的像素电路系统170)以完全描述该像素的灰度值,并且逐帧地保持静态(不改变的)像素140a的状态。

33.再次转向图1a,主机102(即,作为图像数据例如图像、视频、图像数据和/或视频数据104的来源的主机)上的软件应用渲染图像中需要在显示器197上更改的一部分图像(或全部图像)的(例如,帧缓冲器内的)图像数据。在本发明的实施方式中,图像数据被格式化。在本发明的实施方式中,通过将图像数据与命令106(例如,指示关于要更改的图像数据的大小和定位的描述符或图像描述符)进行组合、附加或集成来格式化这样的图像数据,并将图像数据如同其是纯视频数据104(即,没有图像数据包括命令106或命令数据的任何指示)一样传送至传输协议110(例如mipi)的较低层。在本发明的实施方式中,命令106可能在传输之后不进行后续处理,直到命令106被解析器124从发送的数据或图像数据中解析出来。

34.在本发明的实施方式中,使用命令106诸如描述符(例如,区域描述符)来识别哪些像素和/或像素块要被重新加载(即,更改的数据),并且可以由主机102通过传输信道装置110将该更改的数据(与新的图像和/或视频数据104一起)发送至显示子系统120和/或显示加载器逻辑162(即,加载器电路系统和/或软件)。传输信道(例如,线缆、物理层电子器件和传输协议的较高层)110可以保持标准化以实现互操作性,然而,数据流的内容被改变以包

含伪装成图像和/或视频数据104(即,纯图像和/或视频数据104或者对于其包括的命令106不被识别的数据)的命令106和图像和/或视频数据104二者。主机102上的软件的实施方式和显示驱动器逻辑122(或单独的显示驱动器ic)中的解析器124达成一致或根据图像/视频数据包和命令106二者的格式(即,相同的格式或兼容的格式)以及系统100的刷新率进行操作,所述命令诸如提供被刷新的区域的大小和位置的块描述符155。在本发明的实施方式中,主机102和解析器124被设计成达成一致。在本发明的实施方式中,解析器124可以是硬件和/或软件。

35.在显示子系统120(或单片显示ic)中,由解析器124对接收的数据流110进行解析,以提取图像数据152(例如,图像或视频数据104的块)及其随附的命令106或标识符(例如,描述符155)。在本发明的实施方式中,描述符155用于标识新的数据104将被存储在本地高速缓冲存储器153中的何处。在本发明的实施方式中,描述符155被发送至高速缓冲存储器153和加载器162二者,使得驱动器逻辑(即,驱动器电路系统122和/或软件)知道将更改的数据放在哪里,并且使得加载器162知道当其需要将更改的数据写入像素阵列140时从高速缓冲存储器153中的哪里读取所述更改的数据。在本发明的实施方式中,(可以在显示加载器162之前的)高速缓冲存储器153被用于在图像和/或视频数据104被加载到显示器197上之前暂存或存储图像和/或视频数据104。在本发明的实施方式中,高速缓冲存储器153中仅被更新的部分、区段或地址是该高速缓冲存储器153的内容中与如由描述符155(例如,区域描述符)所标识或设置的被更新的显示区域相对应或相关的那些部分。在一些实施方式中,使用整个方案的仅一部分。例如,在实施方式中,主机102可以识别显示器197中要更新的区域,并且仅发送针对该区域的数据,并且高速缓冲存储器153将被重写,而显示器197可以被设置成:如果例如多色显示器需要顺序地显示来自3种单独的颜色的数据(颜色顺序操作),则从高速缓冲存储器153开始进行刷新。

36.在本发明的实施方式中,解析器124将描述符155发送至高速缓冲存储器153并且还发送至加载器162,以及该加载器使用描述符来识别块地址164,从该块地址164读取或提取高速缓冲存储器153中的更改的数据(使得加载器162可以将更改的数据加载到像素阵列140中),然后,该加载器使用描述符155来识别阵列140、300中的用以加载该数据(例如图像数据)的行303和列301。在本发明的实施方式中,可以针对加载器162将从高速缓冲存储器153中提取数据以加载到显示像素140中的时间对描述符155进行排队(即,以与将在显示器或显示器197的像素阵列或像素元件上更新的区域的顺序相同的顺序将描述符155放置在缓冲存储器中)。排队可以以预定的间隔发生。在本发明的实施方式中,可以存在固定的刷新率,其中,将在下一帧时间显示的所有数据到达高速缓冲存储器153以用于根据刷新率来更新显示器197。相比之下,根据本发明的系统100可以以预定间隔(以及这样的间隔的定时可以变化)周期性地更新显示器197或显示器197的像素阵列或像素元件。可替选地,在本发明的实施方式中,根据本发明的系统100可以在显示驱动器逻辑(即,显示驱动器电路系统122和/或软件和/或解析器124)接收到更改的数据时推出所述更改的数据。

37.在本发明的另一实施方式中,主机处理器105仅渲染图像中的活动或改变为视频缓冲的部分,但为方便起见,整个视频缓冲被传输至显示器197,并且显示驱动器逻辑122基于每个区域308中是否存在任何非黑色的像素来计算显示器的各区域的占用图300,诸如矩形图块308或线303的部分。这在图3中示出。该占用图300可以替换从主机102发送的已占用

和已更改的区域的描述符152。只有非黑色的数据303、305、308被写入高速缓冲存储器153,并且只有在占用图中被标记为活动的区域304从高速缓冲存储器153中被检索,并且只有被标记为活动的区域304被写入显示像素存储器174。在本发明的实施方式中,占用图300是数据的集合,并且可以由显示驱动器软件和/或电路系统/硬件进行访问。

38.通过利用本文中的实施方式的系统和方法,通过以下方式节省功耗:仅渲染、传输和刷新显示器的需要更改的部分的数据同时使其他部分保持未改变,而不是发送完整的视频帧。这也产生了与常规系统和方法相比更高的帧速率。

39.在一个实施方式中,像素阵列140中的每个像素140a、140b包括存储器元件174(例如,锁存器)、逻辑172(例如,诸如组合门、晶体管等的硬件)以及像素驱动电路系统176(诸如水平移位器)。可替选地,像素140b中的每一个的一个或更多个可以仅包括存储器元件174和像素驱动逻辑172。这在图1中由两个替选的像素块140a、140b的分解图示出。像素本身并入了足够的存储器174以完整地描述该像素的灰度值,这然后使得像素值在图像没有变化的情况下能够保持静态而没有负载活动。换言之,存在足够的存储器174以存储像素140a、140b中的信息,使得像素140a、140b在不被刷新的情况下逐帧地保持正确的颜色或亮度。像素140a、140b中的逻辑172用于对所存储的灰度值进行解码并调制像素驱动器输出176(例如,设置模拟值、或者在帧的过程中给出期望光强度的一系列二进制值)。在本发明的实施方式中,存储器元件174可以是存储由多个位表示的图像数据的锁存器或锁存器电路系统。

40.像素逻辑172可以并入从g总线接收的信息,并基于图像数据确定哪个波形输出至像素阵列140。参见例如标题为“dynamic pixel modulation”的pct文件pct/us2021/012262的图10至图11,其全部内容完整地并入本文作为本公开内容的一部分。

41.图2示出了根据本文中的实施方式的将在示例性和非限制性的系统应用(即,ar头戴式显示器)中查看的显示区域200。(替选方案可以是用于车辆的hud的显示器)。在本发明的实施方式中,图2示出了覆盖在由装置(例如,ar头戴式装置)的用户所看到的真实世界上的图像210。在图2的示例中,因为观看者正在看叠加了信息的真实世界,所以图像210的大部分214是清晰的(没有光从显示器反射到眼睛)并且不需要更新。移动指示器/符号212占据移动的小区域,并且需要响应佩戴者在其环境中的外部运动。示出了在图像210中具有固定位置的带状区域220,并且该带状区域220的内容仅需要根据需要(根据需要频繁地)进行更新。例如,更新对于时钟可能每秒发生一次,而对于电池指示器222可能非常缓慢。在本发明的实施方式中,根据本发明的系统100在用于显示对叠加在观看者在真实世界中看到的内容上的图像的更改时将是有效的,这是因为该系统将仅更新叠加图像中变化的部分,例如图2中的移动的指示器箭头。

42.图3示出了示例性稀疏图像300,该示例性稀疏图像300被细分为固定大小的区域302、303、305、307、308,这些区域被标记为活动304(包含非黑色的图像数据)或无源302。出于说明的目的,包含非黑色像素的区域的背景被示出为白色。占用图300按这样的方式标记活动区域,并且只有这些区域的数据将被存储到高速缓冲存储器153中、从高速缓冲存储器153中被检索并被加载到每个像素的存储器174中。

43.如图4中所示,描述了根据本发明的显示系统100的操作的方法400。在对显示系统进行操作的方法的实施方式中,该方法可以包括提供显示系统100的步骤410。根据本发明

的实施方式,后续步骤420可以包括从图像或视频数据源120发送图像帧数据,其中,所述图像帧数据包括:图像200的至少一部分的更新的图像数据104,该更新的图像数据104用以替换当前显示的图像200的图像数据的相应部分210。相关联的命令106(例如,用以更新显示驱动序列的各方面(诸如时序参数)的命令)提供区域的描述符以及/或者描述更新的图像数据如何替换图像数据。在由源120以前述方式呈现之后,该方法可以包括在显示子系统120中接收图像帧数据的步骤430。图像帧数据可以由解析器124接收和解析,该解析器124在步骤440中从图像帧数据中提取更新的图像数据104和相关联的命令106并将更新的图像数据104存储在存储装置或高速缓冲存储器153中。然后,在步骤450中,可以根据相关联的命令106将存储装置或高速缓冲存储器153的内容(例如,更新的图像数据104)发送至加载器。加载器162然后可以读取460相关联的命令106以从高速缓冲存储器253中识别和提取更新的图像数据104;以及随后,像素阵列140从加载器162接收470更新的图像数据104;以及在步骤480中,针对仅在更新的图像数据内的像素更新像素驱动器电路系统。

44.可以以数字电子电路系统或以计算机软件、固件和/或硬件(包括本说明书中公开的结构性装置及其结构性等同物)或者以它们的组合来实现本文中描述的主题。本文中描述的主题可以被实现为硬件、一个或更多个计算机程序产品诸如有形地实施在信息载体(例如,机器可读存储装置)中以及/或者实施在传播的信号(例如,电压波形或电流波形)中,以供数据处理设备(例如,可编程处理器、计算机或多个计算机)执行或者以控制数据处理设备(例如,可编程处理器、计算机或多个计算机)的操作的一个或更多个计算机程序。可以以任何形式的编程语言来编写计算机程序(也被称为程序、软件、软件应用或代码),所述任何形式的编程语言包括编译语言或解释语言,并且可以以任何形式——包括作为独立程序或者作为模块、组件、子例程或适合用在计算环境中的其他单元——来部署计算机程序。计算机程序不一定对应于文件。程序可以存储在保存其他程序或数据的文件的一部分中,程序可以存储在专用于正被讨论的程序的单个文件中,或者程序可以存储在多个协调文件(例如,存储一个或更多个模块、子程序或代码的一部分的文件)中。计算机程序可以被部署成在一个计算机上执行或者在多个计算机上执行,所述多个计算机处于一个站点处或者被分布成跨多个站点并且通过通信网络进行互连。

45.本说明书中描述的过程和逻辑流程——包括本文中描述的主题的方法步骤——可以由一个或更多个可编程处理器执行,所述一个或更多个可编程处理器执行一个或更多个计算机程序,以通过对输入数据进行操作并且生成输出来执行本文中描述的主题的功能。还可以由专用逻辑电路系统例如fpga(现场可编程门阵列)或asic(专用集成电路)来执行过程和逻辑流程,并且本文中描述的主题的设备可以被实现为专用逻辑电路系统例如fpga(现场可编程门阵列)或asic(专用集成电路)。

46.通过示例的方式,适合于执行计算机程序的处理器包括通用微处理器和专用微处理器二者以及任何种类的数字计算机的任何一个或更多个处理器。通常,处理器将从只读存储器或随机存取存储器或这二者接收指令和数据。计算机的基本元件是用于执行指令的处理器以及用于存储指令和数据的一个或更多个存储器装置。通常,计算机还将包括或在操作上耦接至用于存储数据的一个或更多个大容量存储装置例如磁盘、磁光盘或光盘以从其接收数据或向其传送数据或两者兼具。适合于实施计算机程序指令和数据的信息载体包括所有形式的非易失性存储器,通过示例的方式包括:半导体存储器装置(例如,eprom、

eeprom和闪存装置);磁盘(例如,内部硬盘或可移动磁盘);磁光盘;以及光盘(例如,cd和dvd盘)。处理器和存储器可以由专用逻辑电路系统补充或被并入专用逻辑电路系统中。

47.本文中描述的主题可以实现在如下计算系统中,所述计算系统包括后端部件(例如,数据服务器)、中间件部件(例如,应用服务器)或前端部件(例如,具有图形用户接口或用户可以通过其与本文中描述的主题的实现进行交互的web浏览器的客户端计算机移动装置、可穿戴装置)或者这样的后端部件、中间件部件和前端部件的任何组合。系统的部件可以通过数字数据通信的任何形式或介质(例如,通信网络)互连。通信网络的示例包括局域网(“lan”)和广域网(“wan”)例如因特网。

48.应当理解,所公开的主题在其应用中不限于构造的细节并且不限于以下描述中阐述或在附图中示出的部件的布置。所公开的主题能够是其他实施方式并且能够以各种方式被实践和执行。此外,应当理解,本文中采用的措词和术语是出于描述的目的并且不应该被视为进行限制。因此,本领域技术人员将认识到,本公开内容所基于的构思可以容易地被用作用于设计用于执行所公开的主题的一些目的的其他结构、方法和系统的基础。因此,重要的是,在等同构造没有脱离所公开的主题的精神和范围的情况下,权利要求应该被视为包括这样的等同构造。

49.尽管已经在前述示例性实施方式中描述和示出了所公开的主题,但是应当理解,本公开内容仅通过示例的方式进行,并且在不脱离所公开的主题的精神和范围的情况下,可以对所公开的主题的实现的细节做出许多改变,所公开的主题的精神和范围仅由所附权利要求限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。