计算机系统及其接口电路

1.相关申请的交叉引用

2.本专利文献要求于2021年3月9日提交的申请号为10-2021-0030510的韩国专利申请的优先权和权益,该韩国专利申请通过引用全部并入本文作为本专利文献的公开内容的一部分。

技术领域

3.本专利文献中公开的技术和实施方式总体上涉及一种半导体集成设备,并且更具体地涉及一种计算机系统及其接口电路。

背景技术:

4.在一些计算机系统中,主机装置和从装置(slave device)通过通道连接。

5.数据存储装置可以包括在计算机系统中用作从装置以保存数据的存储器装置和在计算机系统中用作主机装置以执行将数据写入存储器装置的写入操作和从存储器装置读取数据的读取操作的控制器。存储器装置和控制器通过传输线和接口电路相互连接以发送和接收数据。

6.沿着传输线传输的电信号波可能在传输线的终端(termination)处被反射。反射的信号波可能作为噪声分量被添加到正在传输的电信号波中,从而降低传输信号的质量。因此,这种信号反射是不希望的,并且可以提供终端电路来减少这种不期望的信号反射并且提高信号质量。

7.为了减少或最小化传输信号的反射,终端技术可以用于将终端电阻器连接到传输线的终端。可以通过终端电阻器以恒定的电压电平来端接(terminate)传输线的终端。终端技术的示例包括取决于终端的目标电压电平的中心抽头终端(center tap termination,ctt)方案和低抽头终端(low tap termination,ltt)方案。

8.随着半导体集成技术的发展,提出了用于输入/输出接口的各种通信标准。当发送装置和接收装置的输入/输出接口彼此不匹配时,发送侧和接收侧的系统可能不兼容,或者发送侧与接收侧之间的通信效率可能降低。

技术实现要素:

9.根据所公开的技术的一些实施例的一种计算机系统可以包括:主机装置,包括存储器控制器和被配置为向存储器控制器提供与其它装置的接口的第一接口电路;以及数据存储单元,通过通道与主机装置通信并且被配置为通过包括终端电路的第二接口电路与主机装置通信,其中第一接口电路被配置为在不同的终端方案之间进行选择,并且其中第一接口电路被配置为基于终端电路的终端方案将添加信号(addition signal)添加到传输信号,并且将带有添加信号的传输信号传输到终端电路。

10.根据所公开的技术的一些实施例的一种计算机系统可以包括:第一装置,包括被配置为向第一装置提供与其它装置的接口的第一接口电路;以及第二装置,被配置为通过

通道与第一装置通信,其中第一接口电路被配置为将第一添加信号或与第一添加信号不同的第二添加信号添加到传输信号,并且其中基于通道的终端电压电平来确定是添加第一添加信号还是添加第二添加信号。

11.根据所公开的技术的一些实施例的一种接口电路可以包括:内部电路,被配置为将添加信号添加到第一传输信号以生成第二传输信号;以及输出驱动器,被配置为输出第二传输信号;并且其中接口电路位于计算机系统中的第一装置中,该计算机系统包括第一装置和通过通道与第一装置通信的第二装置,其中接口电路被配置为在多个终端方案之间切换,并且其中添加信号基于连接到通道的终端的终端电路的终端方案而被添加到第一传输信号。

附图说明

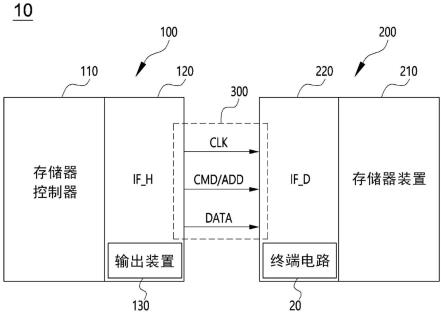

12.图1示出基于所公开的技术的一些实施例的计算机系统的示例。

13.图2示出终端电路的接口连接操作(interfacing operation)的示例。

14.图3示出终端电路的接口连接操作的另一示例。

15.图4示出基于所公开的技术的一些实施例的输出装置的示例。

16.图5示出基于所公开的技术的一些实施例的输出装置的示例。

17.图6是基于所公开的技术的一些实施例的输出装置的时序图。

18.图7示出基于所公开的技术的一些实施例的数据存储系统的示例。

19.图8示出基于所公开的技术的一些实施例的数据处理系统的示例。

20.图9示出基于所公开的技术的一些实施例的数据处理系统的示例。

21.图10是示出基于所公开的技术的一些实施例的包括数据存储装置的网络系统的示例的示图。

22.图11是示出基于所公开的技术的一些实施例的数据存储装置中包括的非易失性存储器装置的示例的框图。

具体实施方式

23.在下文中,将参照附图更详细地描述所公开的技术的一些实施例。

24.图1示出基于所公开的技术的一些实施例的计算机系统10的示例。

25.计算机系统10可以包括第一装置和通过传输线连接到第一装置的第二装置。在一些实施方式中,第一装置可以包括主机装置100,第二装置可以包括用于存储数据的存储单元200,并且传输线可以包括通道300。在一些实施方式中,计算机系统10可以是数据存储装置。

26.主机装置100可以包括用于控制存储单元200的存储器控制器110和第一接口电路120。在一个示例中,第一接口电路120可以包括主机侧接口电路(if-h)。存储单元200可以包括存储器装置210和第二接口电路220。在一个示例中,第二接口电路220可以包括存储器侧接口电路(if-d)。

27.主机装置100可以包括处理器和多个功能块,例如在处理器的控制下操作的功能或功能块,该功能或功能块可具有相应的知识产权(ip)。主机装置100可以包括将具有各种功能的多个功能或功能块合并到单个芯片中的片上系统(soc)。主机侧接口电路120也可以

被实施为集成在主机装置100中的单个功能或功能块。

28.存储器装置210的示例可以包括诸如动态随机存取存储器(dram)、静态随机存取存储器(sram)和晶闸管随机存取存储器(tram)的易失性存储器装置。

29.存储器装置210的示例还可以包括诸如以下的非易失性存储器装置:电可擦除可编程rom(eeprom)、nand闪速存储器、nor闪速存储器、相变ram(pram)、电阻式ram(reram)、铁电ram(fram)以及自旋转矩磁性ram(stt-mram)。

30.存储器装置210可以包括多个管芯、多个芯片或多个封装。另外,存储器装置210可以作为将一位数据存储在一个存储器单元中的单层单元(slc)或将多位数据存储在一个存储器单元中的多层单元(mlc)来操作。

31.计算机系统10可以以固态驱动器(ssd)、存储卡、通用闪速存储(ufs)装置和类似的数据存储装置的形式来实施。

32.通道300可以是在主机装置100与存储单元200之间传送数据或其它信号的路径。

33.主机装置100可以通过主机侧接口电路120将时钟信号(clk)、命令信号(cmd)、地址信号(add)和其他信号传输到存储器侧接口电路220。此外,主机装置100可以通过主机侧接口电路120将数据data传输到存储器侧接口电路220。

34.存储单元200可以通过存储器侧接口电路220将数据data传输到主机装置100。

35.在一些实施方式中,多个存储单元可以共享路径。例如,将数据data从主机装置100传送到存储单元200的路径也可以将数据data从存储单元200传送到主机装置100。在一些实施方式中,从主机装置100传输到存储单元200的数据data可以被称为“写入数据”,而从存储单元200传输到主机装置100的数据data可以被称为“读取数据”。

36.存储器侧接口电路220可以包括终端电路20,以减少或最小化从通道300传输的信号的不期望的反射,以用于提高信号质量,从而“终止”不期望的信号反射。

37.终端电路20的配置可以根据不同的存储单元200而变化。在一些实施方式中,终端电路20可以基于根据各种接口标准的第一终端方案(中心接头终端(ctt)方案)或第二终端方案(低接头终端(ltt)方案)来实施。

38.在所公开的技术的一些实施例中,主机侧接口电路120可以包括输出装置130,输出装置130基于根据存储器侧接口电路220中包括的终端电路20的终端方案确定的选择信号来选择和/或放大输出信号。

39.在所公开的技术的一些实施例中,当终端电路20使用ctt方案时,输出装置130可以增加输出信号的信号边沿的电压电平。例如,可以添加预加重(pre-emphasis)信号以增大和减小输出信号的上升沿和下降沿的电压电平。

40.在所公开的技术的一些实施例中,当终端电路20使用ltt方案时,输出装置130可以增大输出信号的信号边沿之间的电压差。例如,可以添加去加重(de-emphasis)信号以增大输出信号的上升沿和下降沿之间的电压差。

41.图2和图3示出终端电路的接口连接操作的示例。

42.图2示出存储器侧接口电路220-1的终端电路20-1使用ctt方案的示例实施方式。

43.诸如主机装置100的第一装置的主机侧接口电路120可以包括放大和/或输出传输信号in的输出驱动器121。

44.施加到输出驱动器121的输出端子dout的信号可以通过通道300传输到诸如存储

单元200的第二装置。

45.存储器侧接口电路220-1可以包括终端电路20-1和接收电路rx。

46.终端电路20-1可以包括连接在通道300的终端与电源电压vccq端子之间的第一终端电阻器r1,以及连接在通道300的终端与接地电压端子之间的第二终端电阻器r2。第一终端电阻器r1和第二终端电阻器r2可以具有彼此相同的电阻值,或者它们可以具有相似的电阻值。

47.因此,通道300的终端电压在中间电平的基础上增大或减小预定电平,该中间电平例如是通过对第一终端电阻器r1和第二终端电阻器r2两端的电压进行划分而与电源电压vccq的一半相对应的电压电平。根据ctt方案,通道300的终端电压将是中心抽头终端(ctt)。

48.接收电路rx可以通过将通过终端电路20-1接收的信号与参考电压vref进行比较来确定输入信号的逻辑电平(或电压电平)。

49.图3示出存储器侧接口电路220-2的终端电路20-2使用ltt方案的示例实施方式。

50.诸如主机装置100的第一装置的主机侧接口电路120可以包括放大和/或输出传输信号in的输出驱动器121。

51.输出驱动器121的输出信号可以通过通道300传输到诸如存储单元200的第二装置。

52.存储器侧接口电路220-2可以包括终端电路20-2和接收电路rx。

53.终端电路20-2可以包括连接在通道300的终端与接地电压端子之间的第三终端电阻器r3。因此,通道300的终端电压在例如接地电压电平的较低电平的基础上增大预定电平。根据ltt方案,通道300的终端电压将是低抽头终端(ltt)。

54.通过通道300在主机装置100与存储单元200之间移动的信号的高频分量可能衰减,使得信号失真。为了避免潜在的信号失真,可以使用预加重技术和去加重技术来增强发送/接收的数据信号的高频分量。

55.在预加重技术中,第一添加信号被添加到待传输的信号的上升沿和下降沿中的每一个,以增大上升沿的电压并减小下降沿的电压,并且第一添加信号使用传输信号in和传输信号in的反相延迟信号inb_d来生成。

56.在去加重技术中,第二添加信号被添加到待传输的信号的上升沿和下降沿中的每一个,以增大上升沿与下降沿之间的电压差,并且第二添加信号使用传输信号in和传输信号in的延迟信号in_d来生成。

57.通过通道300传输的信号可以通过在传输之前对传输信号in执行预加重并且在接收侧对传输信号执行去加重来保持其波形。

58.图4示出基于所公开的技术的一些实施例的输出装置130的示例。

59.参照图4,基于所公开的技术的一些实施例的输出装置130可以包括主驱动器140和均衡器150。

60.主驱动器140可以被激活以向输出端子dout提供传输信号in。

61.均衡器150可以响应于终端方案选择信号selterm而生成传输信号in的预加重信号或去加重信号,并且将所生成的预加重信号或去加重信号添加到输出端子dout。

62.在所公开的技术的一些实施例中,根据存储单元200的存储器侧接口电路220中包

括的终端电路20的终端方案,终端方案选择信号selterm可以由包括嵌入了计算机系统10的主装置来设置。

63.在所公开的技术的一些实施例中,当存储单元200连接到主机装置100时,终端方案选择信号selterm可以由主机装置100设置。

64.当终端电路20使用ctt方案时,均衡器150可以通过增大传输信号in的上升沿的电压并减小传输信号in的下降沿的电压来生成预加重信号。在所公开的技术的一些实施例中,当终端电路20使用ltt方案时,均衡器150可以通过增大传输信号in的上升沿与下降沿之间的电压差来生成去加重信号。

65.图5示出基于所公开的技术的一些实施例的输出装置的示例。

66.参照图5,主驱动器140可以包括缓冲电路141和第一输出单元143,缓冲电路141将传输信号in的反相信号inb存储预设时间段,第一输出单元143放大和/或输出缓冲电路141的输出信号并且将经驱动的输出信号施加到输出端子dout。

67.均衡器150可以包括延迟电路151、边沿检测单元153、添加信号生成单元155和第二输出单元157。

68.延迟电路151可以将传输信号in延迟例如1个单位间隔(ui)的目标时间段,并且输出延迟的传输信号in_d。

69.边沿检测单元153可以包括第一检测部1531和第二检测部1533,第一检测部1531响应于传输信号in和传输信号in的反相延迟信号inb_d而生成上升沿检测信号vr,第二检测部1533响应于传输信号in和传输信号in的反相延迟信号inb_d而生成下降沿检测信号vf。

70.添加信号生成单元155可以包括第一添加信号生成部电路1551和第二添加信号生成部电路1553,第一添加信号生成部电路1551响应于终端方案选择信号selterm而选择由延迟电路151延迟的传输信号in_d和上升沿检测信号vr中的任意一个,第二添加信号生成部电路1553响应于终端方案选择信号selterm而选择延迟的传输信号in_d和下降沿检测信号vf中的任意一个。

71.第二输出单元157可以激活添加信号生成单元155的输出信号以将第一添加信号或第二添加信号添加到输出端子dout。

72.因此,通过将第一添加信号添加到传输信号in而获得的预加重输出信号或通过将第二添加信号添加到传输信号in而获得的去加重输出信号可以通过通道传输到接收侧装置。

73.在所公开的技术的一些实施例中,缓冲电路141保持传输信号in的反相信号inb的预设时间段可以对应于传输信号in通过均衡器150的边沿检测单元153和添加信号生成单元155的时间段。然而,所公开的技术不限于此。

74.图6是基于所公开的技术的一些实施例的输出装置的时序图。

75.参照图5和图6,当终端电路20基于ctt方案而实施时,可以以逻辑高电平来启用终端方案选择信号selterm。在这种情况下,第一添加信号生成部1551可以输出上升沿检测信号vr,而第二添加信号生成部1553可以输出下降沿检测信号vf。

76.因此,主驱动器140的输出信号与作为均衡器150的输出信号的预加重分量vr和vf可以相加,并且预加重输出信号dout_pre可以被施加到输出端子dout。

77.预加重输出信号dout_pre的电压电平可以基于与终端电路20的终端电压电平相对应的均衡器150的输出信号而增大预定电平。另外,由于均衡器150的预加重分量vr和vf,预加重输出信号dout_pre具有上升沿的电压电平增大预定电平a并且下降沿的电压电平减小预定电平b的波形。

78.当终端电路20基于ltt方案而实施时,可以以逻辑低电平来启用终端方案选择信号selterm。在这种情况下,第一添加信号生成部1551和第二添加信号生成部1553可以输出延迟的传输信号in_d。结果,作为第二输出单元157的输出信号的第二添加信号可以具有与反相延迟传输信号inb_d的相位基本相同的相位。

79.主驱动器140的输出信号和作为均衡器150的输出信号的第二添加信号可以相加,并且去加重输出信号dout_de可以被施加到输出端子dout。

80.去加重输出信号dout_de的电压电平可以基于与终端电路20的终端电压电平相对应的均衡器150的输出信号而增大预定电平。另外,由于均衡器150的去加重分量,去加重输出信号dout_de具有上升沿的电压电平与下降沿的电压电平之间的差增大预定电平的波形,如由图6中的c所指示的。

81.主机装置100可以使用可以在存储单元200中包括的终端电路20中实施的各种终端方案来生成输出信号。因此,单个主机装置100可以根据各种通信标准通过改变终端方案来与不同的存储单元200通信,这可以增加主机装置100和存储单元200与计算机系统10的兼容性,并且确保发送/接收信号的完整性。

82.图7示出基于所公开的技术的一些实施例的数据存储系统1000的示例。

83.参照图7,数据存储系统1000可以包括主机装置1100和数据存储装置1200。在所公开的技术的一些实施例中,数据存储装置1200可以被配置为固态驱动器(ssd)。

84.数据存储装置1200可以包括控制器1210、多个非易失性存储器装置1220-0至1220-n、缓冲存储器装置1230、电源1240、信号连接器1101和电源连接器1103。

85.控制器1210可以控制数据存储装置1200的总体操作。控制器1210可以包括主机接口单元、控制单元、用作工作存储器的随机存取存储器、错误校正码(ecc)单元和存储器接口单元。在所公开的技术的一些实施例中,数据存储装置1200可以包括图2至图5所示的接口电路。

86.主机装置1100可以通过信号连接器1101与数据存储装置1200交换信号。该信号可以包括命令、地址、数据等等。

87.控制器1210可以处理从主机装置1100接收的信号。控制器1210可以根据用于驱动数据存储装置1200的固件或软件来控制内部功能块的操作。

88.缓冲存储器装置1230可以临时存储待存储在非易失性存储器装置1220-0至1220-n中的至少一个中的数据。进一步,缓存存储器装置1230可以临时存储从非易失性存储器装置1220-0至1220-n中的至少一个读取的数据。临时存储在缓冲存储器装置1230中的数据可以基于控制器1210的命令和控制信号而被传输到主机装置1100或非易失性存储器装置1220-0至1220-n中的至少一个。

89.非易失性存储器装置1220-0至1220-n可以用作数据存储装置1200的存储介质。非易失性存储器装置1220-0至1220-n可以通过多个通道ch0至chn分别与控制器1210联接。一个或多个非易失性存储器装置可以联接到一个通道。联接到每个通道的非易失性存储器装

置可以联接到相同的信号总线和数据总线。

90.电源1240可以向数据存储装置1200的控制器1210、非易失性存储器装置1220-0至1220-n和缓冲存储器装置1230提供通过电源连接器1103输入的电力。电源1240可以包括辅助电源。辅助电源可以供应电力以允许在发生突然断电时正常终止数据存储装置1200。辅助电源可以包括足以存储所需电荷的大容量电容器。

91.根据主机装置1100与数据存储装置1200之间的接口方案,信号连接器1101可以被配置为各种类型的连接器中的一个或多个。

92.根据主机装置1100的供电方案,电源连接器1103可以被配置为各种类型的连接器中的一个或多个。

93.图8示出基于所公开的技术的一些实施例的数据处理系统3000的示例。参照图8,数据处理系统3000可以包括主机装置3100和存储器系统3200。

94.主机装置3100可以以板,例如印刷电路板的形式来配置。尽管未示出,但是主机装置3100可以包括用于执行主机装置的功能的内部功能块。

95.主机装置3100可以包括连接端子3110,诸如插座、插槽或连接器。存储器系统3200可以与连接端子3110配合。

96.存储器系统3200可以以板,例如印刷电路板的形式来配置。存储器系统3200可以被称为存储器模块或存储卡。存储器系统3200可以包括控制器3210、缓冲存储器装置3220、非易失性存储器装置(nvm)3231和3232、电源管理集成电路(pmic)3240以及连接端子3250。

97.控制器3210可以控制存储器系统3200的总体操作。存储器系统3200可以包括图2至图5所示的接口电路。

98.缓冲存储器装置3220可以临时存储待存储在非易失性存储器装置3231和3232中的数据。此外,缓冲存储器装置3220可以临时存储从非易失性存储器装置3231和3232读取的数据。基于控制器3210的命令和控制信号,可以将临时存储在缓冲存储器装置3220中的数据传输到主机装置3100或非易失性存储器装置3231和3232。

99.非易失性存储器装置3231和3232可以用作存储器系统3200的存储介质。

100.pmic 3240可以向存储器系统3200的内部提供通过连接端子3250输入的电力。pmic 3240可以基于控制器3210的命令和控制信号来管理存储器系统3200的电力。

101.连接端子3250可以联接到主机装置3100的连接端子3110。通过连接端子3250,诸如命令、地址和数据的信号以及电力可以在主机装置3100与存储器系统3200之间传递。根据主机装置3100与存储器系统3200之间的接口方案,连接端子3250可以被配置为一种或多种类型。连接端子3250可以设置在存储器系统3200的一侧。

102.图9示出基于所公开的技术的一些实施例的数据处理系统4000的示例。参照图9,数据处理系统4000可以包括主机装置4100和存储器系统4200。

103.主机装置4100可以以板,例如印刷电路板的形式来配置。尽管未在图中示出,但是主机装置4100可以包括用于执行主机装置的功能的内部功能块。

104.可以以表面安装式封装的形式来配置存储器系统4200。存储器系统4200可以通过焊球4250并入主机装置4100中。存储器系统4200可以包括控制器4210、缓冲存储器装置4220和非易失性存储器装置4230。

105.控制器4210可以控制存储器系统4200的总体操作。存储器系统4200可以包括图2

至图5所示的接口电路。

106.缓冲存储器装置4220可以临时存储待存储在非易失性存储器装置4230中的数据。进一步,缓冲存储器装置4220可以临时存储从非易失性存储器装置4230读取的数据。基于控制器4210的命令和控制信号,可以将临时存储在缓冲存储器装置4220中的数据传输到主机装置4100或非易失性存储器装置4230。

107.非易失性存储器装置4230可以用作存储器系统4200的存储介质。

108.图10是示出基于所公开的技术的一些实施例的包括数据存储装置的网络系统5000的示例的示图。参照图10,网络系统5000可以包括通过网络5500相互通信的服务器系统5300和多个客户端系统5410、5420和5430。

109.服务器系统5300可以响应于来自多个客户端系统5410至5430的请求而提供数据服务。在示例实施方式中,服务器系统5300可以存储由多个客户端系统5410至5430提供的数据。在另一示例实施方式中,服务器系统5300可以向多个客户端系统5410至5430提供数据。

110.服务器系统5300可以包括主机装置5100和存储器系统5200。存储器系统5200可以被配置为图1所示的存储器系统10,图7所示的数据存储装置1200,图8所示的存储器系统3200,或图9所示的存储器系统4200。

111.图11是示出基于所公开的技术的一些实施例的诸如数据存储装置10的数据存储器装置中包括的非易失性存储器装置300的示例的框图。参照图11,非易失性存储器装置300可以包括存储器单元阵列310、行解码器320、数据读取/写入块330、列解码器340、电压生成器350和控制逻辑360。

112.存储器单元阵列310可以包括存储器单元mc,存储器单元mc布置在字线wl1至wlm和位线bl1至bln按行和列布置的区域处。

113.存储器单元阵列310可以包括三维存储器阵列。例如,三维存储器阵列具有沿垂直于半导体衬底的平坦表面的方向的堆叠结构。此外,三维存储器阵列包括nand存储器单元串,nand存储器单元串中的每一个包括竖直堆叠在半导体衬底上的存储器单元。

114.三维存储器阵列的结构不限于上面讨论的结构。可以以高度集成的方式在水平方向和竖直方向上形成存储器阵列结构。在所公开的技术的一些实施例中,在三维存储器阵列的nand串中,存储器单元布置在相对于半导体衬底的表面的水平和竖直方向上。存储器单元可以以不同的距离彼此间隔开。

115.行解码器320可以通过字线wl1至wlm与存储器单元阵列310联接。行解码器320可以基于控制逻辑360的命令和控制信号而操作。行解码器320可以对由外部装置(未示出)提供的地址进行解码。行解码器320可以基于解码结果来选择并且激活字线wl1至wlm。例如,行解码器320可以向字线wl1至wlm提供由电压生成器350提供的字线电压。

116.数据读取/写入块330可以通过位线bl1至bln与存储器单元阵列310联接。数据读取/写入块330可以包括分别与位线bl1至bln相对应的读取/写入电路rw1至rwn。数据读取/写入块330可以基于控制逻辑360的命令和控制信号而操作。根据操作模式,数据读取/写入块330可以作为写入驱动器或读出放大器进行操作。例如,数据读取/写入块330可以作为写入驱动器进行操作,写入驱动器在写入操作中将由外部装置提供的数据存储在存储器单元阵列310中。再如,数据读取/写入块330可以作为读出放大器(sense amplifier)进行操作,

读出放大器在读取操作中从存储器单元阵列310读出数据。

117.列解码器340可以基于控制逻辑360的命令和控制信号而操作。列解码器340可以对由外部装置提供的地址进行解码。列解码器340可以基于解码结果,将数据读取/写入块330的、分别与位线bl1至bln相对应的读取/写入电路rw1至rwn与数据输入/输出线或数据输入/输出缓冲器联接。

118.电压生成器350可以生成待在非易失性存储器装置300的内部操作中使用的电压。可以将由电压生成器350生成的电压施加到存储器单元阵列310的存储器单元。例如,可以将在编程操作中生成的编程电压施加到存储器单元的、要被执行编程操作的字线。再如,可以将在擦除操作中生成的擦除电压施加到存储器单元的、要被执行擦除操作的井区。又再如,可以将在读取操作中生成的读取电压施加到存储器单元的、要被执行读取操作的字线。

119.基于由外部装置提供的控制信号,控制逻辑360可以控制非易失性存储器装置300的总体操作。例如,控制逻辑360可以控制非易失性存储器装置300的操作,例如非易失性存储器装置300的读取操作、写入操作和擦除操作。

120.本专利文献中公开的技术特征可以以各种配置或方式来实施,并且所公开的实施例仅仅是某些实施方式的示例。可以基于本专利文献中公开和说明的内容对所公开的实施例和其它实施例进行变更和增强。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。