一种基于spi的dsp备份启动实现方法

技术领域

1.本发明涉及嵌入式设备上电启动技术领域,特别涉及一种基于spi的dsp备份启动实现方法。

背景技术:

2.随着dsp在图像、雷达等领域应用愈加广泛,搭载dsp的平台呈现多样化发展,如车载、船载、机载等;这些产品随着功能需求的完善,需要对dsp程序进行更新升级。设备在线升级一旦失败会导致设备无法正常工作,只能通过拆机连接仿真器重新写入程序至flash中解决。受产品密封性要求及运行环境的影响,设备拆机变得十分困难;同时,设备在实际使用过程中,由于flash写入错误程序dsp不能正常启动,导致设备无法正常运行,设备必须暂停当前工作状态,进行维修升级。这种状态大大降低了系统的可靠性。

3.当前技术仅对dsp在线升级进行了保护,保障在线升级过程中的准确性;但dsp启动失败问题,没有给出很好的解决方案。当前技术对基于emif启动进行了设计,由于dsp的emif片选只有4个,当emif与fpga、nand flash、双口ram等芯片连接时,没有可用于dsp启动的emif flash接口。

技术实现要素:

4.本发明的目的在于提供一种基于spi的dsp备份启动实现方法,以解决目前因串口升级失败导致dsp系统无法正常工作、需要拆机的问题。

5.为解决上述技术问题,本发明提供了一种基于spi的dsp备份启动实现方法,包括:

6.(1)dsp的gpio口与fpga的i/o口连接,dsp的上电由fpga控制,spi nor flash存储器外挂在dsp处理器上;dsp上电启动,主核core0自动运行片上的rbl程序,根据硬件配置,选择spi启动模式,配置pll,初始化spi接口;

7.(2)rbl程序运行二级引导程序,从spi nor flash存储器的首地址搬移uboot程序至主核core0运行空间,搬移完成后执行uboot程序;

8.(3)uboot程序根据外部gpio的信号,选择spi nor flash存储器不同分区的应用程序加载至core0~core7的运行空间,并将core1~core7的程序入口地址写入boot_magic_address地址,加载完成后,pc指针跳转到core0应用程序入口地址,运行core0程序,core0向core1~core7发送中断,激活core1~core7。

9.在一种实施方式中,所述dsp外挂一片spi nor flash存储器,所述spi nor flash的存储空间分为三段:flash_space1、flash_space2和flash_space3,其中首地址段flash_space1存放uboot程序,第二段flash_space2和第三段flash_space3存放用户应用程序。

10.在一种实施方式中,所述第三段flash_space3中的应用程序是可用的,在更新程序时,先更新第二段flash_space2中的应用程序,当第二段flash_space2中的应用程序经过验证无问题后,更新第三段flash_space3中的程序。

11.在一种实施方式中,所述uboot程序检测dsp的管脚gpio_m,m为gpio编号,9~15状

态,根据管脚gpio_m的信号高低电平搬移所述spi nor flash存储器中不同分区的应用程序到dsp的运行空间,并跳转至应用程序入口地址。

12.在一种实施方式中,当管脚gpio_m的信号为低电平,uboot程序从第二段flash_space2中搬移应用程序至dsp运行空间;当管脚gpio_m的信号为高电平,uboot程序从第三段flash_space3中搬移应用程序至dsp运行空间。

13.在一种实施方式中,所述dsp的应用程序运行后,管脚gpio_n给出高电平,通知外部处理器dsp启动成功,其中n为gpio编号,9~15,与m不同。

14.在一种实施方式中,所述外部处理器需检测dsp的管脚gpio_n,当未检测到gpio_n的信号为高电平,配置dsp的bootmode为spi方式,将gpio_m的信号拉高,fpga配置dsp的上电时序,复位dsp并重启。

15.在一种实施方式中,所述dsp的型号为飞腾m6678,所述spi nor flash存储器的型号为mt25ql256aba8esf,所述fpga的型号为xc7k325t。

16.在本发明提供的基于spi的dsp备份启动实现方法中,dsp的gpio口与fpga的i/o口连接,dsp的上电由fpga控制,spi nor flash存储器外挂在dsp处理器上;dsp上电启动,主核core0自动运行片上的rbl程序,根据硬件配置,选择spi启动模式,配置pll,初始化spi接口;rbl程序运行二级引导程序,从spi nor flash存储器的首地址搬移uboot程序至主核core0运行空间,搬移完成后执行uboot程序;uboot程序根据外部gpio的信号,选择spi nor flash存储器不同分区的应用程序加载至core0~core7的运行空间,并将core1~core7的程序入口地址写入boot_magic_address地址,加载完成后,pc指针跳转到core0应用程序入口地址,运行core0程序,core0向core1~core7发送中断,激活core1~core7。本发明提供的方法能够有效解决因串口在线升级失败需要拆开设备重新更新程序的问题,以及实际使用中因程序加载失败导致系统无法正常工作的问题。

附图说明

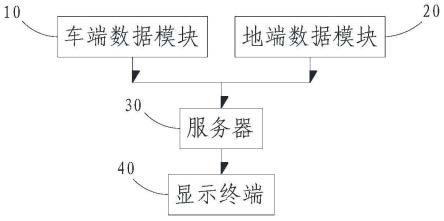

17.图1是硬件连接示意图;

18.图2是spi nor flash中程序存放示意图;

19.图3是基于spi的dsp备份启动流程图。

具体实施方式

20.以下结合附图和具体实施例对本发明提出的一种基于spi的dsp备份启动实现方法作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

21.本发明所使用的dsp芯片型号为飞腾m6678,使用的spi nor flash存储器型号为mt25ql256aba8esf,fpga芯片的型号为xc7k325t。

22.本发明提供一种基于spi的dsp备份启动实现方法,其中处理器的启动过程是处理器在上电或复位后,将存储在外部的非易失存储器中的可执行代码根据外部信号从spi nor flash加载到内存中,并正确运行程序的过程。

23.以飞腾m6678的dsp芯片为例,飞腾m6678具有no boot、host boot和slave boot等

启动方式,其中slave boot包含emif、i2c、spi、串口启动;加载模式由外部的13个引脚bootmode[12:0],即gpio[13:1]复位时的硬件状态来选择。bootmode[2:0]用于选择加载模式。本发明采用spi的启动方式,gpio配置如表1所示。

[0024][0025]

表1配置spi启动模式的gpio配置

[0026]

本发明为实现基于dsp的spi备份启动,将dsp的上电时序控制管脚与fpga连接,gpio/bootmode管脚与fpga连接,由fpga控制dsp上电和启动模式控制。dsp外挂spi nor flash存储器,用于存放用户uboot程序和应用程序,如图1所示。

[0027]

本发明为实现基于dsp的spi备份启动,将spi nor flash的存储空间分为3段:flash_space1、flash_space2和flash_space3,其中第一段存放用户uboot程序,第二段和第三段存放应用程序,如图2所示。

[0028]

本发明为实现基于dsp的spi备份启动,编写uboot的汇编程序,uboot程序初始化pll,初始化spi nor flash接口,读取dsp的内部的devstat寄存器,判断devstat寄存器的第15位,即管脚gpio15的状态:若管脚gpio15为低电平,则uboot从spi nor flash存储器的flash2地址搬移程序;若管脚gpio15为高电平,则uboot从spi nor flash存储器的flash3地址搬移程序。为保证uboot程序和应用程序在dsp主核core0中的运行空间不会冲突,对uboot程序和应用程序的代码存放空间进行了约束。存放uboot程序的空间不允许运行应用程序。具体方法如下,在函数定义的地方增加:

[0029]

.sect"bootsection",其中bootsection是用户自定义的段名,该段需要在cmd文件中定义

[0030]

memory{boot:o=0x10800000l=0x2000}

[0031]

sections{"bootsection"》boot}

[0032]

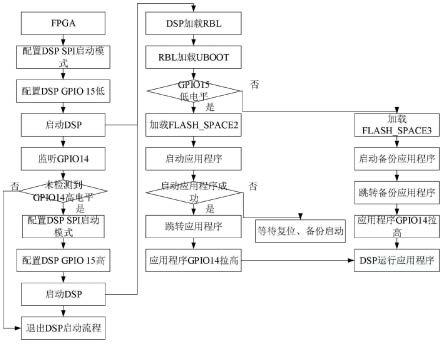

本发明提供的基于spi的dsp备份启动实现方法的流程如图3所示,包括如下步骤:

[0033]

(1)系统上电后,fpga配置dsp的bootmode为spi启动模式,同时将管脚gpio15置低电平,复位dsp;

[0034]

(2)dsp复位启动后,通过rbl(rom bootloader,rom引导加载程序)程序从spi nor flash的首地址加载uboot程序,然后core0运行uboot程序;

[0035]

(3)uboot程序初始化pll、初始化spi nor flash、读取devstat寄存器,判断devstat寄存器的第15位,即管脚gpio15的状态;若管脚gpio15的信号为低,uboot程序将从flash_space2的空间加载应用程序;

[0036]

(4)uboot程序配置core1~core7的boot_magic_address地址,然后core0跳转到应用程序入口地址,开始执行应用程序;

[0037]

(5)若dsp正常启动,core0激活core1~core7,将管脚gpio14置高电平,运行应用程序;

[0038]

(6)fpga在dsp上电后5s内检测管脚gpio14的电平,若为高电平,则判定dsp启动成功,若检测到管脚gpio14的信号为低电平,则判定dsp启动失败;

[0039]

(7)若dsp启动成功,fpga退出启动流程,dsp正常运行应用程序;

[0040]

(8)若dsp启动失败,fpga复位dsp,并配置dsp为spi启动模式,同时将管脚gpio15置高电平,复位dsp;

[0041]

(9)dsp复位后,通过rbl程序加载uboot程序,然后core0运行uboot程序;dsp检测到管脚gpio15的信号为高电平,uboot程序从flash_space3的空间加载应用程序,然后core0跳转到应用程序入口地址,开始执行应用程序;完成dsp备份程序的启动。

[0042]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。