低阻外延层,所述外延层为p型高阻外延层。

9.上述带箝位功能的双层硅外延达林顿晶体管芯片的制作方法,其步骤是:

10.1、选用重掺杂的n 型或p 型硅片衬底,在硅片衬底表面生长与硅片衬底同型的缓冲低阻外延层和高阻外延层,在高阻外延层的正面生长一层氧化层;

11.2、对氧化层光刻腐蚀后,在高阻外延层的正面通过扩散工艺形成箝位二极管、前级晶体管t1和后级晶体管t2的基区、前级晶体管t1的be间的电阻r1及后级晶体管t2的be间的电阻r2;

12.3、在基区内通过扩散工艺形成前级晶体管t1的发射区及后级晶体管t2的发射区;

13.4、在所述后极晶体管t2的发射区极条与后极晶体管t2的集电极间寄生形成续流保护二极管;

14.5、在前级晶体管t1的基区上方设有基极金属层,用于形成前极晶体管t1的基极b;在后级晶体管t2的发射区上方设有发射极金属层,用于形成t2管的发射极e;在前级晶体管t1的发射极及后级晶体管t2的基区上形成连接金属层以及该达林顿晶体管的连接电极;在芯片表面非引出电极部位上设有氮化硅表面保护层;

15.6、将所述硅片衬底背面减薄后,蒸钛镍银后形成背面金属层,用于形成前级晶体管t1与后级晶体管t2共接的集电极c。

16.进一步,在形成前、后级晶体管的基区时,同时在基区周围形成与所述硅片衬底不同型的场限环。

17.进一步地,前级晶体管t1及后级晶体管t2的基区为一体结构并且是通过去除高阻外延层的正面覆盖的氧化层,重新生长一层氧化层,光刻后进行硼扩散形成。

18.进一步地,前、后级晶体管的基区及前级晶体管t1的be间的电阻r1、后级晶体管t2的be间的电阻r2是通过第二次扩散工艺形成。

19.进一步,所述缓冲低阻外延层为n-型且电阻率为0.1~0.6ω

·

cm,高阻外延层为n型且电阻率为28~40ω

·

cm。

20.进一步,所述缓冲低阻外延层为p-型且电阻率为0.25~1.5ω

·

cm,高阻外延层为p型且电阻率为70~100ω

·

cm。

21.本发明的有益效果在于:

22.1、选用双层外延结构,为了满足功率达林顿晶体管的击穿电压(bvceo)的指标要求,除去电阻率选定合适之外,选择的高阻外延层总厚度由集电结结深、集电结雪崩击穿时对应的空间电荷区宽度及缓冲外延层反扩散层厚度三者确定,使高阻外延层厚度符合穿通击穿的设计要求。采用该外延片生产的双极型器件导通时集电极串联电阻值比较小,可以获得较小的饱和压降。通过在高阻外延层与重掺杂衬底间增加一层缓冲低阻外延层,降低了高阻外延层与重掺杂衬底间的浓度梯度,提高了二次击穿耐量。双层外延片具有厚度可控、重复性均匀性好、衬底掺杂浓度高、规避了三重扩散片机械减薄引入的损伤和缺陷,有利于高可靠产品的生产与技术指标的控制,从而提高产品的抗反向二次击穿能力,晶体管参数一致性更好。

23.2、芯片上集成箝位二极管,箝位二极管工作状态与达林顿晶体管的饱和或截止状态同步,设计上控制其反向击穿,将达林顿晶体管的击穿电压箝位在一定数值范围内,使其低于集电结的二次击穿电压,确保晶体管工作在安全工作区内,提高产品抗正向二次击穿

能力。因此可以防止达林顿器件发生二次击穿烧毁,起到对器件的保护作用。

附图说明

24.图1是普通达林顿晶体管芯片的电路原理图;

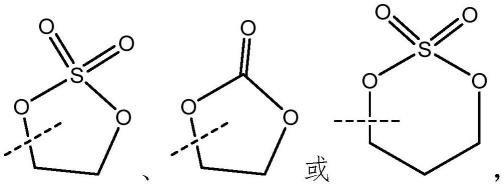

25.图2是带箝位功能的双层硅外延npn达林顿晶体管芯片的电路原理图;

26.图3是本发明的带箝位功能的双层硅外延npn达林顿晶体管芯片的纵向结构图;

27.图4是本发明的带箝位功能的双层硅外延达林顿晶体管芯片结构示意图;

28.图中:1-硅片衬底、2-缓冲外延层、3-高阻外延层、4-氧化层、5-氮化硅、6-金属铝电极b、7—金属钛镍银电极、8—箝位二极管、9—基区、10—t1发射区、11—t2发射区、12—续流保护二极管、13—p型场限环、14—电阻r1、15—电阻r2、16-金属铝电极e、17—t1的发射极及t2的基区的连接金属层。

具体实施方式

29.以下结合附图和实施例对本发明进行详细说明:

30.实施例1

31.如图2所示,该带箝位功能的双层硅外延达林顿晶体管属于二级npn达林顿晶体管,包括前级晶体管t1与后级晶体管t2,前级晶体管t1的基极作为达林顿晶体管的基极,所述前级晶体管t1的集电极与后级晶体管t2的集电极相连,前级晶体管t1的基极与集电极间集成箝位二极管z-di,用于提高产品的抗二次击穿能力,提高产品的可靠性;前级晶体管t1的发射极与后级晶体管t2的基极相连,后级晶体管t2的发射极作为达林顿晶体管的发射极。前、后级晶体管的be间分别连接电阻r1和r2,用于提高产品的开关速度及热稳定性;前级晶体管be间的电阻为1.5kω,后级晶体管be间的电阻为160ω;在后级晶体管t2的集电极和发射极之间接有续流保护二极管vd。

32.如图3和图4所示,该带箝位功能的双层硅外延达林顿晶体管,包括n 型重掺杂硅片衬底1,在所述硅片衬底1表面由下至上设有n-型缓冲低阻外延层2和高阻外延层3,n型高阻外延层3正面通过扩散工艺设有箝位二极管8、前级晶体管t1和后级晶体管t2的基区9、电阻r1和r2以及p型场限环13,所述p型场限环13位于前级晶体管t1和后级晶体管t2的基区9周围。所述箝位二极管8位于前级晶体管t1的基区下面,在基区9内通过扩散工艺设有前级晶体管t1的发射区10及后级晶体管t2的发射区11,在后级晶体管t2发射区极条之间的基区与t2的集电极之间寄生形成续流保护二极管12。在前级晶体管t1的基区上方设有基极金属层6引出t1管的基极b,在后级晶体管t2的发射区上方设有发射极金属层引16出t2管的发射极e,在前级晶体管t1的发射极及后级晶体管t2的基区之间形成连接金属层17,在硅片衬底1背面蒸钛镍银后形成背面金属层7,用于形成前级晶体管t1与后级晶体管t2共接的集电极c,在高阻外延层3的正面覆盖有氧化层4,在芯片表面非引出电极部位设有氮化硅表面保护层5。

33.该带箝位功能的双层硅外延npn达林顿晶体管的制作步骤包括:

34.1、选用n 型《111》重掺杂硅片衬底1,衬底厚度450

±

5μm且电阻率为0.002~0.003ω

·

cm;

35.2、在硅片衬底1外延生长厚度为20~25μm且电阻率为0.2~0.3ω

·

cm的n-型缓冲

低阻外延层2及厚度为70~75μm且电阻率为28~30ω

·

cm的n型高阻外延层3,生长氧化层4,氧化层厚度为1.2~1.4μm;

36.3、进行第一次氧化光刻后,经硼扩散形成箝位二极管8,表面浓度2*10

19

cm-3

~3*10

19

cm-3

,结深60~65μm;

37.4、进行第二次氧化光刻后,经硼扩散形成前级晶体管t1和后级晶体管t2的基区9(前级晶体管t1的基区与后级晶体管t2的基区连接),所述基区9的表面浓度1*10

18

cm-3

~2*10

18

cm-3

,结深20~22μm;并同时形成前级晶体管t1的be间的电阻r1(图3中标记14)、前级晶体管t2的be间的电阻r2(图3中标记15),同时在基区9周围形成p型场限环13;

38.5、进行第三次氧化光刻后,磷扩散形成前级晶体管t1的发射区10及后级晶体管t2的发射区11,发射区10和发射区11为梳条状,,所述发射区表面浓度2*10

20

cm-3

~3*10

20

cm-3

,结深10~12μm;

39.6、在形成发射区的同时,在后级晶体管t2的发射区极条中间的p型基区与后级晶体管t2的集电极间寄生形成续流保护二极管12;

40.7、进行第四次氧化光刻,蒸铝及铝合金工序后,在前级晶体管t1的p型基区上方形成基极金属层6;在后级晶体管t2的n 型发射区上方形成发射极金属层16;在前级晶体管t1的发射极及后级晶体管t2的基区上形成连接金属层17;铝层厚度为3.5μm~4.0μm。

41.8、对铝层进行光刻腐蚀后,进行表面钝化工序,在芯片表面非电极部位形成氮化硅钝化层5,钝化层厚度为0.2μm~0.3μm。

42.9、最后将n 型硅片衬底4背面减薄后,蒸钛镍银后形成背面金属层7,用于形成前级晶体管t1与后级晶体管t2共接的集电极c,金属层的厚度要求为钛层:0.08μm~0.1μm,镍层:0.25μm~0.30μm,银层:0.45μm~0.5μm。

43.实施例2

44.参照图2、图3,该带箝位功能的双层硅外延达林顿晶体管属于二级pnp达林顿晶体管,芯片具体结构与实施例1相同,该晶体管芯片制作步骤如下:

45.1、选用p 型《111》硅片衬底,衬底厚度450

±

5μm且电阻率为0.002~0.003ω

·

cm;

46.2、在硅片衬底1外延生长厚度为20~25μm且电阻率为0.25~1.5ω

·

cm的p-型缓冲低阻外延层2及厚度为70~75μm且电阻率为70~100ω

·

cm的p型高阻外延层3,在高阻外延层3的正面生长有氧化层4,氧化层厚度为1.2~1.4μm;

47.再按照与实施例1步骤3~步骤9相同的工艺条件,制作出带箝位功能的双层硅外延pnp达林顿晶体管芯片。

48.对比例

49.选用三重扩散片,高阻层厚度为75~80μm,电阻率为28~30ω

·

cm,按照与实施例1步骤4~步骤9相同的工艺条件制作npn型达林顿晶体管芯片。

50.由实施例1与对比例生产的两种npn型达林顿晶体管芯片,经to-257金属封装后测试,各取5只的测试结果如下:

51.序号bvceo(双层外延)bvceo(三重扩散)1362.84v348.23v2351.28v364.15v3357.53v371.76v

4365.11v355.56v5359.30v360.44v

52.由测试结果可看出,基于双层外延片制作的芯片击穿电压区间为15v,而基于三重扩散芯片制作的芯片击穿电压区间超过了20v,因此可看出基于双层外延制作的芯片的击穿电压的一致性更高。

53.在不背离本发明精神及其实质的情况下,本领域技术人员根据本发明作出的各种相应的改变和变形,都应该属于本发明的权利要求的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。