nrhc-14t抗辐照sram存储单元、芯片和模块

技术领域

1.本发明涉及静态随机存储单元技术领域,特别是涉及nrhc-14t抗辐照sram存储单元、芯片和模块。

背景技术:

2.随着互补金属氧化物半导体(complementary metal oxide semiconductor,缩写为cmos)技术不断进步。电子器件的尺寸越来越小,它的集成度越来越高与其工作的太空辐射环境等因素都影响着器件的稳定性。太空中的辐射效应会对正在工作的静态随机存储(static random access memory,缩写为sram)引发单粒子效应(single event effect,缩写为see)。单粒子效应会对电子器件造成硬错误与软错误。硬错误的发生会导致器件物理级的损坏,从而导致灾难性的后果;而软错误主要是影响器件的工作状态,使其无法传递正确的信息。由于空间辐射粒子的能量有限,其造成器件发生软错误的几率要远远大于其导致器件发生硬错误的几率。而在软错误中,单粒子翻转(single event upset,缩写为seu)发生的概率远远大于其它类型错误发生的概率。为了提高单元抗seu的能力,现有技术中主要包括以下几种方案:

3.1.如图1所示是一种抗单粒子翻转的dice 12t电路。它拥有4个存储节点以及4个传输管。当每个单存储节点上发生seu时,该节点终究都会被剩余节点所恢复。但是,当其中任意两个存储节点发生seu时,该电路节点的存储信息将会发生翻转且无法自我恢复,从而导致错误数据发生。

4.2.如图2所示是一种soft error tolerant 10t sram bitcell(quatro 10t)电路。它相比于传统六管单元结构有更好的抗seu的能力,但是该单元的写能力较差,并且其保持噪声容限(hold static noise margin,缩写为hsnm)与读静态噪声容限(read static noise margin,缩写为rsnm)较差。

5.3.如图3所示是一种sar14t电路,该电路利用4个nmos晶体管向单元内部写入数据,但是却用2个nmos晶体管通过外部节点进行读取,由此导致单元有着较大的读取延迟时间。

6.4.如图4所示是一种rsp14t电路,该电路利用源隔离技术,当单元存“1”时,堆叠的pmos结构使晶体管p2连接着信号弱“1”,因此晶体管p2的漏极收集电荷量将被减少,节点qb对seu的抵抗能力得到提高,该单元变得更加稳定。

7.5.如图5所示是一种radiation hardened by polar design(rhpd-12t)电路,该电路在抵抗单节点翻转基础上还可以抵抗部分双节点翻转。但其以较低的hsnm与rsnm为代价。

8.6.如图6所示是一种radiation hardened by design sram bit-cell(rhbd14t)电路。该电路采用极性加固技术,虽然减少了敏感节点的个数,但是却导致了较大的读写延迟,以及较低的噪声容限(snm)数值。

9.基于上述现有方案,需要一种提高存储单元读写速度、降低单元功耗和提高单元

抗单粒子翻转能力的nrhc-14t单元。

技术实现要素:

10.基于此,有必要针对存储单元读写速度慢、单元功耗高和单元抗单粒子翻转能力差的问题,提供一种nrhc-14t抗辐照sram存储单元、芯片和模块。

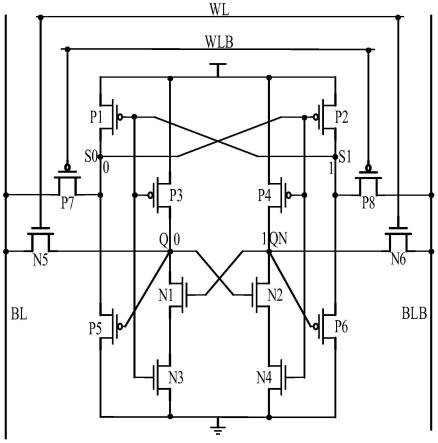

11.nrhc-14t抗辐照sram存储单元,其包括:

12.pmos晶体管p1;

13.pmos晶体管p2,p2的漏极与p1的栅极电连接,p2的栅极与p1的漏极电连接,p2的源极与p1的源极电连接;

14.pmos晶体管p3,p3的栅极与p1的栅极、p2的漏极电连接,p3的源极与p1的源极、p2的源极电连接;

15.pmos晶体管p4,p4的栅极与p2的栅极、p1的漏极电连接,p4的源极与p1的源极、p2的源极、p3的源极电连接;

16.pmos晶体管p5,p5的源极与p1的漏极电连接,p5的栅极与p3的漏极电连接;

17.pmos晶体管p6,p6的源极与p2的漏极电连接p6的栅极与p4的漏极电连接,p6的漏极与p5的漏极电连接;

18.pmos晶体管p7,p7的漏极与p1的漏极电连接,p7的栅极与字线wlb电连接,p7的源极与位线bl电连接;

19.pmos晶体管p8,p8的漏极与p2的漏极电连接,p8的栅极与字线wlb电连接,p8的源极与位线blb电连接;

20.nmos晶体管n1,n1的漏极与p3的漏极、p5的栅极电连接,n1的栅极与p4的漏极、p6的栅极电连接;

21.nmos晶体管n2,n2的漏极与p4的漏极、p6的栅极、n1的栅极电连接,n2的栅极与n1的漏极、p3的漏极、p5的栅极电连接;

22.nmos晶体管n3,n3的漏极与n1的源极电连接,n3的栅极与p3的栅极、p1的栅极、p2的漏极电连接,n3的源极与p5的漏极、p6的漏极电连接;

23.nmos晶体管n4,n4的漏极与n2的源极电连接,n4的栅极与p4的栅极、p2的栅极、p1的漏极、p5的源极电连接,n4的源极与n3的源极、p5的漏极、p6的漏极电连接;

24.nmos晶体管n5,n5的漏极与n1的漏极电连接,n5的栅极与字线wl电连接,n5的源极与位线bl电连接;

25.nmos晶体管n6,n6的漏极与n2的漏极电连接,n6的栅极与字线wl电连接,n6的源极与位线blb电连接;

26.晶体管p1和p2交叉耦合,p1、p2、p3与p4作为上拉管,p5和p6作为下拉管,它们的状态分别由存储节点q和qn控制,p3和n3、p4和n4分别构成反相器,n1和n2分别插入到两个反相器之间并且交叉耦合,两个主存储节点q与qn通过n5与n6分别与位线bl和blb相连,两个冗余存储节点s0与s1通过p7与p8分别与位线bl和blb相连,n5与n6由字线wl控制,p7与p8由字线wlb控制;vdd与晶体管p1、p2、p3与p4的源极电连接;晶体管n3、n4的源极与p5、p6的漏极接地。

27.进一步的,所述晶体管n1~n6以及p1~p8的长均为65nm,其中p1、p2宽为370nm,

p5、p6宽为80nm,其余晶体管宽均为140nm。

28.在其中一个实施例中,所述nrhc-14t抗辐照sram存储单元处于保持阶段时,位线bl和blb预充到高电平,字线wl为低电平,字线wlb为高电平,电路内部保持初始状态。

29.在其中一个实施例中,所述nrhc-14t抗辐照sram存储单元处于读数据阶段时,位线bl和blb预充到高电平,字线wl为高电平,字线wlb为低电平,晶体管n5、n6、p7与p8打开。

30.进一步的,如果该单元电路存储的数据为

‘0’

,则“q=s0=0、qn=s1=1”;位线bl通过放电路径1:晶体管p7、p5和放电路径2:晶体管n5、n1与n3向地放电,使得位线产生电压差,通过灵敏放大器读出数据;如果该单元电路存储的数据为

‘1’

,则“q=s0=1、qn=s1=0”;位线blb通过放电路径1:晶体管p8、p6和放电路径2:晶体管n6、n2与n4向地放电,使得位线产生电压差,通过灵敏放大器读出数据。

31.在其中一个实施例中,所述nrhc-14t抗辐照sram存储单元处于写入数据阶段时,字线wl为高电平,字线wlb为低电平。

32.进一步,如果bl为高电平,blb为低电平,则通过晶体管n5和p7分别向存储节点q点与s0点写

‘1’

;如果bl为低电平,blb为高电平,则通过晶体管n6和p8分别向存储节点qn点与s1点写

‘1’

。

33.本发明还包括nrhc-14t抗辐照sram存储芯片,其采用前述nrhc-14t抗辐照sram存储单元的电路结构封装而成。

34.进一步的,所述nrhc-14t抗辐照sram存储芯片的引脚包括:

35.第一引脚,其通过字线wlb与晶体管p7与p8的栅极电连接;

36.第二引脚,其通过字线wl与晶体管n5与n6的栅极电连接;

37.第三引脚,其通过位线bl与晶体管n5与p7的源极电连接;

38.第四引脚,其通过位线blb与晶体管n6与p8的源极电连接。

39.本发明还包括nrhc-14t抗辐照sram存储模块,其采用前述nrhc-14t抗辐照sram存储单元的电路,所述nrhc-14t抗辐照sram存储模块包括:

40.晶体管p7、p8的栅极电连接字线wlb,由此引出第一连接端;

41.晶体管n5、n6的栅极电连接字线wl,由此引出第二连接端;

42.晶体管n5、p7的源极电连接位线bl,由此引出第三连接端;

43.晶体管n6与p8的源极电连接位线blb,由此引出第四连接端。

44.本发明提供的技术方案,具有如下有益效果:

45.采用rhm-14t抗辐照sram存储单元能够提高单元电路的抗seu的能力,可以在牺牲较小单元面积的情况下大幅度提高单元的速度,并且降低了单元的功耗。

附图说明

46.图1为本发明背景技术提供的现有技术中dice电路的结构示意图;

47.图2为本发明背景技术提供的现有技术中quatro 10t电路的结构示意图;

48.图3为本发明背景技术提供的现有技术中sar14t电路的结构示意图;

49.图4为本发明背景技术提供的现有技术中rsp14t电路的结构示意图;

50.图5为本发明背景技术提供的现有技术中rhpd-12t电路的结构示意图;

51.图6为本发明背景技术提供的现有技术中rhbd14t电路的结构示意图;

52.图7为本发明nrhc-14t抗辐照sram存储单元的结构示意图;

53.图8为图7内nrhc-14t抗辐照sram存储单元的时序波形图;

54.图9为以图7内nrhc-14t抗辐照sram存储单元在不同时刻,不同节点受到双指数电流源脉冲注入的瞬态波形仿真图;

55.图10为图7内nrhc-14t抗辐照sram存储单元与图1~6现有技术进行hsnm、rsnm、wsnm比对的对比图;

56.图11为图7内nrhc-14t抗辐照sram存储单元与图1~6现有技术在不同供电电压与不同频率情况下失败次数对比图;

57.图12为以图7内nrhc-14t抗辐照sram存储单元为基础的nrhc-14t抗辐照sram存储芯片的结构示意图。

具体实施方式

58.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步地详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

59.如图7所示,本实施例提供nrhc-14t抗辐照sram存储单元,其包括pmos晶体管p1~p8和nmos晶体管n1~n6。晶体管p1和p2交叉耦合,p1、p2、p3与p4作为上拉管,p5和p6作为下拉管,它们的状态分别由存储节点q和qn控制,p3和n3、p4和n4分别构成反相器,n1和n2分别插入到两个反相器之间并且交叉耦合,两个主存储节点q与qn通过n5与n6分别与位线bl和blb相连,两个冗余存储节点s0与s1通过p7与p8分别与位线bl和blb相连,n5与n6由字线wl控制,p7与p8由字线wlb控制;vdd与晶体管p1、p2、p3与p4的源极电连接;晶体管n3、n4的源极与p5、p6的漏极接地。

60.具体连接方式如下:位线bl与传输管n5与p7的源极电连接;位线blb与晶体管n6与p8的源极电连接;字线wl与传输晶体管n5和n6的栅极电连接;字线wlb与传输晶体管p7和p8的栅极电连接;传输晶体管n5的漏极与nmos晶体管n1的漏极电连接;传输晶体管n6的漏极与nmos晶体管n2的漏极电连接;传输晶体管p7的漏极与pmos晶体管p1的漏极电连接;传输晶体管p8的漏极与pmos晶体管p2的漏极电连接;vdd与pmos晶体管p1、p2、p3与p4的源极电连接;nmos晶体管n3、n4的源极与pmos晶体管p5、p6的漏极接地。

61.pmos晶体管p1的漏极与pmos晶体管p5的源极、pmos晶体管p2、p4的栅极、nmos晶体管n4的栅极电连接,并且pmos晶体管p1的栅极与pmos晶体管p2的漏极、pmos晶体管p6的源极、pmos晶体管p3的栅极、nmos晶体管n3的栅极电连接。pmos晶体管p2的漏极与pmos晶体管p6的源极、pmos晶体管p1、p3的栅极、nmos晶体管n3的栅极电连接,并且pmos晶体管p2的栅极与pmos晶体管p1的漏极、pmos晶体管p5的源极、pmos晶体管p4的栅极、nmos晶体管n4的栅极电连接。pmos晶体管p3的漏极与nmos晶体管n1的漏极、nmos晶体管n2的栅极、pmos晶体管p5的栅极电连接,并且pmos晶体管p3的栅极与nmos晶体管n3的栅极、pmos晶体管p1的栅极、pmos晶体管p2的漏极、pmos晶体管p6的源极电连接。pmos晶体管p4的漏极与nmos晶体管n2的漏极、nmos晶体管n1的栅极、pmos晶体管p6的栅极电连接,并且pmos晶体管p4的栅极与nmos晶体管n4的栅极、pmos晶体管p2的栅极、pmos晶体管p1的漏极、pmos晶体管p5的源极电连接。pmos晶体管p5的源极与pmos晶体管p1的漏极电连接,并且pmos晶体管p5的栅极与

pmos晶体管p3的漏极、nmos晶体管n1的漏极电连接。pmos晶体管p6的源极与pmos晶体管p2的漏极电连接,并且pmos晶体管p6的栅极与pmos晶体管p4的漏极、nmos晶体管n2的漏极电连接。

62.nmos晶体管n1的漏极与pmos晶体管p3的漏极、pmos晶体管p5的栅极、nmos晶体管n2的栅极电连接,并且nmos晶体管n1的栅极与nmos晶体管n2的漏极、pmos晶体管p4的漏极、pmos晶体管p6的栅极电连接。nmos晶体管n2的漏极与pmos晶体管p4的漏极、pmos晶体管p6的栅极、nmos晶体管n1的栅极电连接,并且nmos晶体管n2的栅极与nmos晶体管n1的漏极、pmos晶体管p3的漏极、pmos晶体管p5的栅极电连接。nmos晶体管n3的漏极与nmos晶体管n1的源极电连接,并且nmos晶体管n3的栅极与pmos晶体管p3、p1的栅极、pmos晶体管p2的漏极、pmos晶体管p6的源极电连接。nmos晶体管n4的漏极与nmos晶体管n2的源极电连接,并且nmos晶体管n4的栅极与pmos晶体管p4、p2的栅极、pmos晶体管p1的漏极、pmos晶体管p5的源极电连接。n5的漏极与n1的漏极电连接,n5的栅极与字线wl电连接,n5的源极与位线bl电连接。n6的漏极与n2的漏极电连接,n6的栅极与字线wl电连接,n6的源极与位线blb电连接。

63.所有晶体管的长均为65nm,其中pmos晶体管p1、p2宽为370nm,p5、p6宽为80nm,剩下所有晶体管宽均为140nm。

64.上述nrhc-14t抗辐照sram存储单元的原理如下:在保持阶段,位线bl和blb都预充到高电平,字线wl为低电平,字线wlb为高电平,电路内部保持初始的状态,电路不工作。当在读数据阶段,位线bl和blb都预充到高电平,字线wl为高电平,字线wlb为低电平,传输晶体管n5、n6、p7与p8打开;如果该单元电路存储的数据为

‘0’

,则“q=s0=0、qn=s1=1”;那么bl通过放电路径1:晶体管p7、p5和放电路径2:晶体管n5、n1、与n3向地放电,使得位线产生电压差,然后通过灵敏放大器读出数据;如果该单元电路存储的数据为

‘1’

,则“q=s0=1、qn=s1=0”那么blb通过放电路径1:晶体管p8、p6和放电路径2:晶体管n6、n2与n4向地放电,使得产生位线电压差,然后通过灵敏放大器读出数据。在写入数据阶段,字线wl为高电平,字线wlb为低电平,如果bl为高电平,blb为低电平,那么通过传输晶体管n5和p7分别向存储节点q点与s0点写

‘1’

;如果bl为低电平,blb为高电平,那么通过传输晶体管n6和p8分别向存储节点qn点与s1点写

‘1’

。当在写入的过程中,因为通过传输晶体管n5与p7和n6与p8同时向内部节点q\s0与qn\s1写入数据,使得存储节点更容易被写入数据,这样写入的速度会大大提高,同时,由于写入速度的大提高从而使电路的功耗降低。

65.当只考虑电路结构对抗辐照性能的提升时,如果电路的存储节点受到粒子轰击,由于电路节点s0和s1均由pmos晶体管包围,根据极性加固原理,空间粒子轰击敏感节点pmos管,在节点仅产生“0-1”的电压脉冲,而该脉冲由于栅电容的存在不能影响其他晶体管的状态,这使得外部节点s0和s1有效避免发生翻转,同时s0和s1节点数据的稳定保证了内部节点q和qn可以在发生翻转后恢复至初始状态,从而使得电路抗seu的能力得到了提高。如果是其他非关键节点受到粒子的轰击,那么存储单元更加不易受到影响。

66.在仿真条件为corner:tt;temperature:27℃;vdd:1.2v的情况下,nrhc-14t抗辐照sram存储单元电路的时序波形情况如图8所示。nrhc-14t抗辐照sram存储单元电路在不同时刻,不同节点受到双指数电流源脉冲注入的瞬态波形仿真情况如图9所示。nrhc-14t抗辐照sram存储单元电路与现有技术sram单元电路相比hsnm、rsnm、wsnm对比情况如图10所示。nrhc-14t抗辐照sram存储单元电路与现有技术sram单元电路相比在不同供电电压与不

同频率情况下失败次数对比情况如图11所示。

67.仿真条件与上述一致,本实施例所提供的14t抗辐照sram存储单元电路整体的电路面积、读写时间和功耗与现有技术sram单元电路有所改善,如下表所示:

68.仿真对比表

69.单元面积(μm2)读延迟(ps)写延迟(ps)功耗(μw)dice8.9756.227.615.16quatro7.48112.525.1315.1sar14t11.03109.52115.17rsp14t10.9611031.915.12rhpd-12t8.7551.8220.415.19rhbd14t9.8599.539.315.13nrhc-14t10.479117.515.12

70.仿真条件与上述一致,本实施例所提供的nrhc-14t抗辐照sram存储单元临界电荷与现有技术sram单元电路相比数值较高,如下表所示:

71.电荷对比表

72.电路名称临界电荷(fc)quatro7.36rsp14t7.24rhpd-12t19.6dice》50sar14t》50rhbd14t》50nrhc-14t》50

73.由此可见,本发明所提供的nrhc-14t抗辐照sram存储单元,能够提高单元电路的抗seu的能力,可以在牺牲较小单元面积的情况下大幅度提高单元的速度,并且降低了单元的功耗。

74.如图12所示,在前述nrhc-14t抗辐照sram存储单元的基础上,进一步的提供了nrhc-14t抗辐照sram存储芯片,该芯片由nrhc-14t抗辐照sram存储单元封装而成;封装成芯片的模式,更易于nrhc-14t抗辐照sram存储单元的推广与应用。

75.所述nrhc-14t抗辐照sram存储芯片的引脚包括:第一引脚,其通过字线wlb与晶体管p7、p8的栅极电连接。第二引脚,其通过字线wl与晶体管n5、n6的栅极电连接。第三引脚,其通过位线bl与晶体管n5、p7的源极电连接。第四引脚,其通过位线blb与晶体管n6与p8的源极电连接。

76.在前述nrhc-14t抗辐照sram存储单元的基础上,本实施例还包括nrhc-14t抗辐照sram存储模块,其采用前述nrhc-14t抗辐照sram存储单元中的电路结构,nrhc-14t抗辐照sram存储模块包括:晶体管p7、p8的栅极电连接字线wlb,由此引出第一连接端。晶体管n5、n6的栅极电连接字线wl,由此引出第二连接端。晶体管n5、p7的源极电连接位线bl,由此引出第三连接端。晶体管n6与p8的源极电连接位线blb,由此引出第四连接端。

77.将nrhc-14t抗辐照sram存储单元设计成nrhc-14t抗辐照sram存储模块,可方便

nrhc-14t抗辐照sram存储单元在市场中的推广与应用,方便本领域技术人员快速使用将nrhc-14t抗辐照sram存储单元,只需参照产品说明书,对模块进行线路连接即可。

78.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

79.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。