1.本发明涉及串行加法器技术,属于数字集成电路设计技术领域,具体涉及一种基于分时复用全加器的串行加法器及其运算方法。

背景技术:

2.在大规模集成电路的发展历程中,数据运算是必不可少的。其中,以加法运算为最基本的数据运算方式。在一些数字系统中,譬如cpu、alu、adc等架构,加法器更是最基础的组件。

3.随着便携式设备朝着更小的方向发展,集成电路对体积的要求越来越高,但目前加法器主流的并行加法器虽然速度较快,但是其中包含的大量全加器所占资源较多,并行输入的特性需要相匹配的引脚数量,也暴露了其不适合超多位加法器的实现。而在很多应用中,并不需要这么高的运算速度,而是希望减少所占用的资源。

4.与传统加法器相比,数字串行加法器具有占用资源少、设计灵活等特点。在国内外的文献中,大多数并行加法器设计是采用集成芯片或异或逻辑实现,串行加法器设计大都是采用位移寄存器等集成芯片实现其功能,而且串行加法器所占内容也很少。

5.目前的串行加法器原理为数据逐位串行送入加法器进行运算。由移位寄存器从低位到高位逐位串行提供操作数相加。如果操作数长n位,加法就要分n次进行,每次产生一位和,并串行地送回寄存器。进位触发器用来寄存进位信号,以便参与下一次的运算。其中大部分串行加法器的半加器部分依然采用经典的28t全加器电路,其时钟信号仅能控制寄存器。

6.针对上述缺陷,本发明从底层设计出一种专门用来实现n位加法功能的电路结构。在避免并行加法器的全加器单元数量多,加速通道占用面积大,电路结构复杂等缺点的前提下,利用分时复用的思想,重复利用全加器电路结构以提高对电路的利用率,克服现有加法器所占面积较大的缺点。从而解决在不需要较快速度、面积资源需求小的场景下的加法器应用。

技术实现要素:

7.技术问题:

8.针对上述缺陷,本发明要解决的技术问题是,在具有传统cmos良好驱动能力和健壮性的同时,如何设计出具有更少的全加器单元的加法器,减少晶体管数目,从而简化加法器的电路结构,降低多位加法器的面积等资源占用,同时设计出具有时钟控制的全加器。

9.技术方案:

10.为解决上述问题,本发明提供了一种基于全加器的串行加法器,所述串行加法器包括:所述全加器包括:由电路切换结构(1)、选择输出结构(2)和输出整合结构(3)组成;

11.所述电路切换结构(1)是以时钟信号clk(4)切换电路结构为基础,clk为不同电平时,电路切换成计算进位信号的电路结构或计算求和信号的电路结构;

12.所述选择输出结构(2)是以两套传输门电路为基础,当传输门接受特定信号后,会传输上述特定信号状态下的进位信号或求和信号;

13.所述输出整合结构(3)是以门电路为基础,利用门电路将所述选择输出结构(2)输出的进位信号或求和信号与所述时钟信号clk(4)组合成为一个端口,上述端口在所述时钟信号clk(4)为不同电平时输出进位信号或求和信号;

14.所述串行加法器包括:以所述全加器为基础,由时延校准结构(6)、反馈输入结构(5)组成;

15.所述时延校准结构(6)是以三态门为基础,通过所述选择输出结构(2)的进位信号或求和信号与时钟控制的三态门组合,延长并延后适当周期,获得延迟后的进位信号或求和信号;

16.所述反馈输入结构(5)以所述时延校准结构(6)中的延迟后的进位信号接入该加法器的进位信号输入端;

17.为解决上述技术问题,本发明还提供了针对本发明所涉及的串行加法器的计算方法,所述方法包括:

18.s1、加数信号a在加数输入端输入一串信息,在被加数输入端输入一串信息后,在i-1级计算单元中,通过所述电路切换结构(1)、所述选择输出结构(2)和所述输出整合结构(3),可得到i-1级进位信号c

i-1

;

19.s2、进位信号c

i-1

通过所述时延校准结构(6)延迟并优化进位信号c

i-1

;

20.s3、优化后的进位信号c

i-1

通过所述反馈输入结构(5)传输到进位信号输入端,并作为第i级的进位信号;

21.进一步地,所述步骤s3的第i级进位信号与第i级加数信号和第i级被加数信号共同经过计算,产生第i级求和信号,延迟并优化第i级求和信号,则可在求和信号输出端口输出所述时钟信号clk(4)的一个时钟周期差的第i级求和信号。

22.有益效果:本发明提供了一种基于全加器的串行加法器及其运算方法,将传统cmos加法器进行改进,具有以下优点:

23.第一、设计出了一个时钟控制的全加器,在一个时钟周期内两次利用全加器结构,提高了全加器电路的利用率;

24.第二、本发明所提出的加法器只用了一个全加器单元,而且没有加速通道,减少了多位加法器引脚数量,有效降低了多位加法器所占面积;

25.第三、本发明所提出的加法器的运算速度取决于时钟频率,将加速问题从如何设计加速通道的角度转移到如何提高时钟频率的角度;

26.第四、当令其中一个被加数输入b一直接地时,输出信号s可以当作加数输入a的一个时钟周期的延时器。

附图说明

27.图1为分时复用全加器的电路原理图;

28.图2为全加器计算进位信号c的电路原理图;

29.图3为全加器计算求和信号s的电路原理图;

30.图4为分时复用全加器multisim仿真电路图;

31.图5为分时复用全加器multisim仿真电路的波形图;

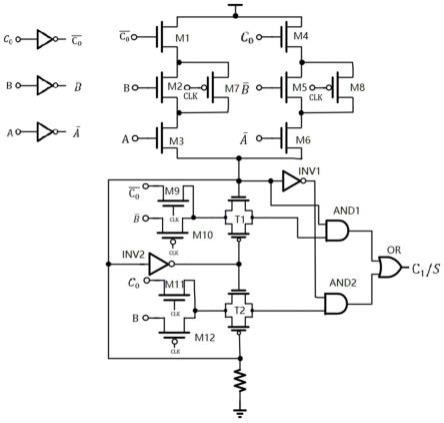

32.图6为时延校准电路的延时关系图;

33.图7为进位信号ci的延迟校准电路;

34.图8为总求和信号si的延迟校准电路;

35.图9为串行加法器原理图;

36.图10为串行加法器multisim仿真电路图;

37.图11为串行加法器multisim仿真电路的波形图。

具体实施方式

38.为了解决现有技术中存在的多位加法器中的大量全加器占用资源较多、并行输入导致引脚众多的问题,本发明实施例提供一种串行输入加法器。该加法器以分时复用的全加器为基础,只需很小的结构就可以实现多位加法器的功能。

39.以下结合说明书附图对本发明实施例进行说明,应当理解,此处所描述的实施例仅用于说明和解释本发明,并不用于限制本发明。并且在不冲突的情况下,本说明中的实施例及实施例中的特征可以相互结合。

40.实施例1:

41.本发明实施例1中首先提供一种基于分时复用的全加器,所述全加器具体包括:电路切换结构1、选择输出结构2和输出整合结构3。

42.其中电路切换结构1如图1所示,利用时钟信号clk控制m7、m8、m9、m10、m11、m12等mos管,当时钟信号clk为高电平时,m7、m8、m10、m12等mos管关闭通路,m9、m11的mos管可以导通,形成计算进位信号c1的电路如图2所示;当时钟信号clk为低电平时,m7、m8、m10、m12等mos管可以导通,从而屏蔽掉m2、m5的mos管,m9、m10等mos管关闭通路,形成计算求和信号s的电路如图3所示。

43.选择输出结构2如图1所示,选择输出结构由t1、t2等传输门m9、m10、m11、m12等mos管以及inv2反相器组成,当在inv1输入端的信号为高电平时,t1传输门打开,t2传输门关闭,输出进位信号或求和信号当在inv1输入端的信号为高电平时,t1传输门关闭,t2传输门打开,输出进位信号c1=c0或求和信号s=b。

44.输出整合结构3如图1所示,由inv1反相器和and1、and2与门以及or或门组成,其中and1的输出端为全加器电路在上拉网络导通时的c1/s的输出,and2的输出端为全加器电路在下拉网络导通时的c1/s的输出,or将and1和and2的输出端整合在一起输出,使得or的输出端口输出为,clk为高电平时进位信号c1的值,clk为低电平时求和信号s的值。

45.本实施例在multisim软件支持下,根据如图1所示的全加器电路原理图进行电路搭建,搭建的仿真电路如图4所示;其中电阻r2、r3、r4、r1、r5、r6用于泄放上一计算单位所存储的电荷,从而提高电路精度;u7a和u6b反相器是用于提高上述反相器inv1输入端的信号的驱动能力,提高电路稳定性;同理,u8a和u3b、u9a和u4b、u19a和u5b、u10a和u7b也是用来提高信号的驱动能力,提高电路稳定性。

46.本实施例在multisim软件支持下,在如图4所示的仿真电路中,设置加数信号a为64hz、占空比为50%的方波,被加数信号b为32hz、占空比为50%的方波,上级进位信号c

i_1

为16hz占空比为50%的方波,控制信号clk1为128hz,占空比为50%的方波,由于控制信号

clk1的频率时加数信号a的两倍,加数信号a的频率是被加数信号b的两倍,被加数信号b的频率时上级进位信号c

i_1

的两倍,之所以如此设置,是因为便于观察波形信息;

47.全加器仿真电路波形如图5所示,其中,从上到下依次为加数信号a波形、被加数信号b波形、上级进位信号c

i_1

波形、输出信号ci/s的波形,由于存在上述关系,在从初始处算起的一个信号a的周期内,前半周期输出进位信号c1,后半周期输出求和信号s;

48.逻辑验证:当信号输入信息为a:10101010

……

、b:11001100

……

、c

i_1

:11110000

……

:abc

i_1

=111的全加器cis输出为11、abc

i_1

=011的全加器cis输出为10、abc

i_1

=101的全加器cis输出为10、abc

i_1

=001的全加器cis输出为01、abc

i_1

=110的全加器cis输出为10、abc

i_1

=010的全加器cis输出为01、abc

i_1

=100的全加器cis输出为01、abc

i_1

=000的全加器cis输出为00;cis的输出波形应为1110100110010100

……

,符合全加器本身的逻辑输出。

49.实施例2:

50.本发明实施例2提供一种基于实施例1所述的全加器的加法器,所述加法器的电路解构如图9所示,具体包括:实施例1所述全加器、时延校准结构4和反馈输入结构5。

51.其中时延校准结构4依据如图6所示的时序关系图,利用三态门组合以及电容等结构构造进位信号ci的延迟校准电路6和求和信号si的延迟校准电路7。

52.其中,进位信号ci延迟校准电路6如图7所示,由and3与门接收ci/s信号和时钟信号,and3与门输出提纯后的进位信号ci,但提纯后的此信号如图6中第二行波形所示,每个有效周期内含有没有信息的低电平,将上述提纯后的进位信号ci通过由tri1、tri2、tri3、tri4、tri5、tri6三态门组以及c1、c2、c3等电容后,可获得如图6所示的第三行波形,即进位信号ci延迟校准电路6延长半个时钟周期,延后一个时钟周期,上述时钟周期为clk的时钟周期。

53.其中,求和信号si的延迟校准电路7如图8所示,由and4与门接收ci/s信号和反相时钟信号,and4与门输出提纯后的求和信号s,但提纯后的此信号如图6中第四行波形所示,每个有效周期内含有没有信息的低电平,将上述提纯后的求和信号s通过由tri7、tri8、tri9、tri10、tri11、tri12三态门组以及c4、c5、c6等电容后,可获得如图6所示的第五行波形,即求和信号si的延迟校准电路7延长半个时钟周期,延后半个时钟周期,上述时钟周期为clk的时钟周期。

54.其中反馈输入结构5如图7所示的tri6的输出信号接入到加法器的进位输入端,使得进位信号链通过时差可以在相应的级数下参与运算,从而实现串行加法的功能,由于ci在第一个时钟周期内的信息为低电平,所以不需要额外的操作使得c-1

=0。

55.如图6所示的第二行波形,经过上述变换后可以输出如图6所示的第三行波形,此波形所示的进位信号,是与该进位信号一起运算的加数a信号和被加数b信号所需要的进位信号,在对应的输入信息下,tri12三态门的输出端输出如图6所示的第三行波形的求和信号,上述求和信号的第一个时钟周期为无效的低电平信息,从第二个时钟周期开始才获得正确的求和信号。

56.本实施例在multisim软件支持下,根据如图9所示的加法器电路原理图进行电路搭建,搭建的仿真电路如图10所示;其中电阻r2、r3、r4、r1、r5、r6用于泄放上一计算单位所存储的电荷,从而提高电路精度;u7a和u6b反相器是用于提高上述反相器inv1输入端的信

号的驱动能力,提高电路稳定性;同理,u8a和u3b、u9a和u4b、u19a和u5b、u10a和u7b也是用来提高信号的驱动能力,提高电路稳定性。

57.本实施例在multisim软件支持下,在如图10所示的仿真电路中,设置加数信号a为64hz、占空比为50%的方波,被加数信号b为32hz、占空比为50%的方波,控制信号clk为128hz,占空比为50%的方波,由于控制信号clk的频率时加数信号a的两倍,加数信号a的频率是被加数信号b的两倍,之所以如此设置,是因为便于观察波形信息;

58.全加器仿真电路波形如图11所示,其中,从上到下依次为加数信号a波形、被加数信号b波形、控制信号clk波形、总求和信号si的波形,由于存在上述关系,在从初始处算起的第二个总求和信号si的周期内,才输出有效的总求和信号;

59.逻辑验证:当信号输入信息为a:10101010

……

、b:11001100

……

:

60.1 1进位1求和0;

61.0 1 1进位1求和0;

62.1 0 1进位1求和0;

63.0 0 1进位0求和1;

64.1 1 0进位1求和0;

65.0 1 1进位1求和0;

66.1 0 1进位1求和0;

67.0 0 1进位0求和1;

68.……

69.如图11所示的总求和信号si的输出波形为(0)00010001

……

,括号内的0是上述的无效低电平信息。符合加法器本身的逻辑输出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。