一种100g以上相干光检测用高速模拟复用器

技术领域

1.本发明属于高速集成电路设计技术领域,具体涉及一种100g以上相干光检测用高速模拟复用器。

背景技术:

2.基于数字信号处理(digital signal processing,dsp)的下一代100gbaud以上相干光通信收发系统需要100gs/s的数模转换器(dac)和模数转换器(adc),而adc和dac则需要超过50ghz的模拟带宽,这对基于cmos工艺的adc和dac提出了巨大的挑战。模拟架构多路复用技术成为弥补adc/dac模拟带宽不足的新技术方案。

3.目前已有部分关于超高速amux的设计与研究工作,包括基于吉尔伯特单元的多路选择架构,以及基于归零码(rz)产生电路和加法器的模拟时间交织架构等。例如采用基于吉尔伯特单元的amux架构,如图1(a)所示,测试的数据和时钟路径的3db带宽均超过110ghz。采用双吉尔伯特单元的amux架构,如图1(b)所示,测试得到56gs/s的pam4信号眼图。但是,以上架构在输出数据率为130gbaud时需要采用65ghz的超高速输入时钟进而导致功耗激增,且无法补偿接口对信道的衰减。除此之外,采用基于归零码生成电路架构,如图2所示,通过调整两抽头系数实现加重,进而针对信道的衰减进行补偿。

技术实现要素:

4.本发明所要解决的技术问题在于针对上述现有技术中的不足,提供一种100g以上相干光检测用高速模拟复用器,基于bicmos工艺,将高速时钟模块集成于片内,同时把均衡技术应用于模拟架构多路复用设计,以补偿板间互联信道衰减,实现高速数据的正确传输。

5.本发明采用以下技术方案:

6.一种100g以上相干光检测用高速模拟复用器,包括前馈均衡器,前馈均衡器的时钟输入端依次经第二时钟缓冲器、电压控制延迟线、时钟选择器、第一时钟缓冲器和传输线分别连接两路时钟信号;前馈均衡器的两个数据输入端分别经连续时间线性均衡器和传输线连接对应的数据信号;前馈均衡器的数据信号输出端经输出缓冲器和传输线输出;通过调整前馈均衡器实现高频信号的衰减补偿。

7.具体的,前馈均衡器包括主抽头和次抽头,前馈均衡器的一个数据输入端经主抽头与前馈均衡器的数据输出端连接,前馈均衡器的另一个数据输入端经次抽头与前馈均衡器的数据输出端连接。

8.进一步的,主抽头和次抽头均包括一个与门电路,主抽头的与门电路经一个跨导单元电路与前馈均衡器的数据输出端连接;次抽头的与门电路经另一个跨导单元电路与前馈均衡器的数据输出端连接;采用rz信号实现mux功能,通过与门时钟与数据信号的相位关系实现1个数据单位时间间隔的延时。

9.更进一步的,与门电路具体为:

10.bjt管q1和bjt管q2的基极分别连接差分输入的数据信号vip和vin;bjt管q3和bjt

管q4的基极连接直流电压vdc,bjt管q1和bjt管q3的集电极与串联连接的电阻r1和电感l1连接作为voutn输出,bjt管q2和bjt管q4的集电极与串联连接的电阻r2和电感l2连接作为voutp输出;bjt管q5和bjt管q6的基极分别接差分输入的时钟信号ckp,ckn,q5的集电极与bjt管q1和bjt管q2的发射极连接,bjt管q6的集电极与bjt管q3和bjt管q4的发射极连接,bjt管q5和bjt管q6的发射极与电流源管m1的漏极连接,m1的源极接地,栅极接偏置电压v

bias

。

11.更进一步的,跨导单元电路具体为:

12.bjt管q7和bjt管q8的基极分别接偏置电压v

biasp

和v

biasn

;bjt管q9和bjt管q10的基极分别连接偏置电压v

biasn

和v

biasp

;bjt管q7的集电极和bjt管q9的集电极连接,作为电流i

outn

输出;bjt管q8的集电极和bjt管q10的集电极连接,作为电流i

outp

输出;bjt管q11和bjt管q12的基极分别连接第一路数据的差分输入vin1p和vin1n;bjt管q13和bjt管q14的基极分别接第二路数据的差分输入vin2p和vin2n;

13.bjt管q11,bjt管q13的集电极与bjt管q7,bjt管q8的发射极连接;bjt管q12,bjt管q14的集电极与bjt管q9,bjt管q10的发射极连接;bjt管q11的发射极分别与电阻r3和电容c1连接,bjt管q12的发射极分别与电阻r4和电容c2连接,bjt管q13的发射极分别与电阻r5和电容c3连接,bjt管q14的发射极分别与电阻r6和电容c4连接;电流源管m2和电流源管m3的栅极连接偏置电压v

bias

;电流源管m2的漏极连接电阻r3,电容c1,电阻r4和电容c2,电流源管m3的漏极连接电阻r5,电容c3,电阻r6和电容c4;电流源管m2和电流源管m3的源极接地。

14.再更进一步的,bjt管q7和bjt管q10的基极接偏置电压v

biasp

,bjt管q8和bjt管q9的基极接偏置电压v

biasn

,通过调节v

biasp

和v

biasn

的差值实现跨导的变化调节。

15.进一步的,对于主抽头,时钟的高电平与第一路数据做与运算,时钟的低电平与第二路数据做与运算,对于次抽头,时钟的低电平与第一路数据做与运算,时钟的高电平与第二路数据做与运算。

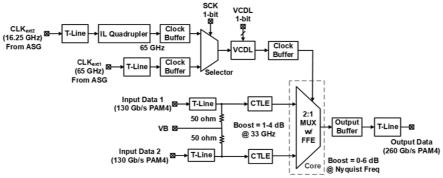

16.具体的,两路时钟信号为16.25ghz时钟信号和65ghz时钟信号。

17.进一步的,16.25ghz时钟信号经传输线和注入锁定四倍频器与第一时钟缓冲器的一个输入端连接,65ghz时钟信号经传输线与第一时钟缓冲器的另一个输入端连接。

18.具体的,数据信号为两路130gb/s的pam4数据信号,两路130gb/s的pam4数据信号分别经对应的传输线和连续时间线性均衡器与带前馈均衡器的两个数据输入端连接。

19.与现有技术相比,本发明至少具有以下有益效果:

20.本发明一种100g以上相干光检测用高速模拟复用器,时钟缓冲器clock buffer依次经选择器selector、vcdl延迟单元和时钟缓冲器clock buffer与带前馈均衡器ffe的amux连接;片上的注入锁定四倍频器提高了芯片集成度,降低了后续系统应用阶段对外部提供的高速时钟速率的要求;输入端的连续时间线性均衡器ctle和输出端的前馈均衡器ffe通过均衡技术可以补偿高速信号在板间信道传输的损耗,确保链路传输过程中的信号完整性,通过与门电路实现rz信号,通过跨导电路实现rz信号的相加,最终实现两路数据输入,一路数据输出的2:1的复用功能。

21.进一步的,在不考虑均衡的情况下,即只打开主抽头,关闭次抽头时,在与门电路中,时钟的高电平与第一路数据做与运算,时钟的低电平与第二路数据做与运算,产生的两

路rz信号通过跨导电路进行加和,实现mux的功能;在考虑均衡的情况下,即打开主抽头以及次抽头时,主抽头与次抽头均产生了mux后的数据信号,且次抽头的数据相较于主抽头的数据滞后了一个ui(unit interval)的时间,通过跨导电路调节两抽头系数,再由主抽头的数据减去次抽头的数据即可实现均衡功能。

22.进一步的,与门电路的目的是实现rz信号,即归零码,当ckp为高电平,ckn为低电平时,q1,q2差分对管对应的通路导通,q3,q4差分对管对应的通路关断,此时数据正常输出;当ckp为低电平,ckn为高电平时,q1,q2差分对管对应的通路关断,q3,q4差分对管对应的通路导通,此时输出无信号。因此在时钟信号的一半周期内数据正常输出,另一半周期内没有数据信号输出,即可实现rz信号。

23.进一步的,跨导电路将两路rz数据进行相加,实现mux的功能;跨导电路可以通过调节跨导大小来完成ffe抽头系数调节的功能。

24.进一步的,本发明只需调节cascode bjt管的偏置电压vbiasp和vbiasn的差值即可实现跨导的变化,尾电流源大小保持不变,可以保证允许的最大输出信号摆幅不变,从而提高电路的线性度。

25.进一步的,主抽头与次抽头对应的与门电路相同,区别是时钟与数据的时序关系不同,只需要调整时钟信号与数据信号的相位关系即可实现1个数据ui(unit interval)的延时,降低了电路设计的复杂度。

26.进一步的,通过设置两条时钟链路,若后续产品形态可以集成片上高速时钟,即65ghz时钟产生模块,则选用倍频时钟这条时钟链路,外部只需注入16.25ghz的时钟信号,降低了对外部信号源的性能需求;若后续产品形态无法集成片上高速时钟(65ghz),则选用备用的时钟链路;amux的设计选择加入前馈均衡器ffe是因为输出的pam4数据速率很高,最高可达到130gbaud,即260gb/s,因此需要前馈均衡器提供均衡功能,补偿高频情况下输出信道的插入损耗。

27.进一步的,两路130gb/s的pam4数据信号分别经对应的传输线和连续时间线性均衡器与带前馈均衡器的两个数据输入端连接,连续时间线性均衡器ctle是为了补偿输入信道的损耗;前馈均衡器ffe是为了补偿输出信道的损耗。

28.综上所述,本发明集成了注入锁定四倍频器,降低了系统应用中对外部所需时钟源速率的要求;针对pam4信号完成了2:1的复用功能,实现了速率超过100gbaud的高速pam4信号传输;引入由与门单元和跨导单元实现的前馈均衡技术,补偿板间互联信道在高频下的损耗。

29.下面通过附图和实施例,对本发明的技术方案做进一步的详细描述。

附图说明

30.图1为现有高速amux架构1示意图,其中,(a)为单吉尔伯特单元,(b)为双吉尔伯特单元;

31.图2为现有高速amux架构2示意图;

32.图3为带有均衡单元及时钟模块的amux架构图;

33.图4为带有ffe功能的amux结构图;

34.图5为时钟与数据的相位关系图;

35.图6为130gbaud输出pam4信号眼图,其中,(a)为均衡前,(b)为均衡后;

36.图7为本发明关于幅频响应的仿真结果图;

37.图8为本发明关于总谐波失真(total harmonic distortion,thd)的仿真结果图。

具体实施方式

38.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

39.还应当理解,在本发明说明书中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本发明。如在本发明说明书和所附权利要求书中所使用的那样,除非上下文清楚地指明其它情况,否则单数形式的“一”、“一个”及“该”意在包括复数形式。

40.还应当进一步理解,在本发明说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

41.在附图中示出了根据本发明公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

42.随着视频流和云计算等宽带应用的快速发展,光网络中的通信流量呈指数增长。尤其是在核心网中,需要大容量、长距离的传输技术来容纳客户数据以及链接城域。结合了相干检测和dsp的数字相干技术已部署在核心网络中,通过增加符号速率、调制阶数或增加子载波数量来增加信道容量,以应对快速增长的流量需求。然而这对于光发射机中基于cmos工艺的dac的模拟带宽提出了巨大的挑战。高符号速率系统中的dac不仅必须具有高采样率,而且还必须具有宽模拟输出带宽。

43.本发明提供了一种100g以上相干光检测用高速模拟复用器,通过一种2:1的高速模拟复用器实现带宽倍增技术,以此缓解对于dac带宽需求的压力。伴随着数据速率不断提高的同时,信道的损耗越来越无法忽略,由于信道对信号不同频率成分的衰减是不一致的,且频率越高衰减越大,导致信号较为严重的码间干扰,因此需要在amux中引入均衡技术,以此来补偿信道的损耗。此外,sige工艺既具备硅工艺的良率、集成度和成本优势,又具备iii-v族化合物半导体良好的高频特性。

44.请参阅图3,本发明一种100g以上相干光检测用高速模拟复用器,能够输出最高可达130gbaud四电平脉冲幅度调制(4pulse amplitude modulation,pam4)信号,不仅实现了2:1的复用功能,而且引入了均衡技术,具体如下:

45.时钟信号包括16.25ghz时钟信号和65ghz时钟信号,16.25ghz时钟信号经传输线,注入锁定四倍频器及第一时钟缓冲器后与时钟选择器的一个输入端连接;65ghz的时钟信号经过传输线及第一时钟缓冲器后与时钟选择器的另外一个输入端连接;时钟选择器选择其中一路时钟信号并将其输出,经电压控制延迟线和第二时钟缓冲器后与前馈均衡器的时钟输入端口连接。

46.数据信号为两路130gb/s的pam4数据信号,两路130gb/s的pam4数据信号分别经各自对应的传输线和连续时间线性均衡器后与前馈均衡器的两个数据输入端连接。

47.前馈均衡器将复用后的数据信号经数据信号输出端经输出缓冲器和传输线后输出;前馈均衡器包括主抽头和次抽头,通过调整主抽头及次抽头的系数实现高频信号的衰减补偿。

48.时钟采用注入锁定技术实现倍频效果,将外部注入的16.25ghz的时钟信号四倍频至65ghz,考虑到实际测试的需要,内置时钟选通模块selector,对内部或外部的时钟进行选择;16.25ghz的时钟信号clk

ext2

经t-line、il quadrupler和时钟缓冲器clock buffer与selector的一个输入端连接,65ghz的时钟信号clk

ext1

经t-line和clock buffer与selector的另一个输入端连接;选择器selector的输出端经vcdl延迟单元和时钟缓冲器clock buffer与带ffe功能的amux时钟输入端连接;input data1和input data2分别经对应的t-line和ctle后与amux的数据输入端连接,amux的数据输出端经输出缓冲器output buffer和t-line连接,用于输出output data。

49.t-line:传输线

50.用于传输高速信号,并可用于50欧姆匹配。

51.il quadrupler:注入锁定四倍频器

52.用于将输入的时钟信号的频率提升至原来的四倍。

53.clock buffer:时钟缓冲器

54.用于增强时钟信号的驱动能力,提高时钟信号的摆幅。

55.selector:选择器

56.用于对两路时钟信号进行选择,起到2选1的功能。

57.vcdl:电压控制延迟线

58.用于调整时钟信号的相位。

59.ctle:连续时间线性均衡器

60.用于输入数据信号的均衡。

61.ffe:前馈均衡器

62.用于实现两路数据输入,一路数据输出的复用功能,均衡输出数据信号。

63.output buffer:输出缓冲器

64.用于增强输出数据信号的驱动能力,提高输出数据信号的摆幅,还可用于50欧姆匹配。

65.数据的输入及输出通路均增加均衡功能,对于输入信道的损耗,由输入连续时间线性均衡器(continuous time linear equalization,ctle)进行补偿,对于输出信道的损耗,由带有前馈均衡器(feedforward equalization,ffe)功能的amux进行补偿,前馈均衡器设置有两个抽头,通过调整主抽头及次抽头系数实现高频信号的衰减补偿,为本发明区别于现有结构的创新所在。

66.请参阅图4,主抽头和次抽头分别包括一个与门(and)及一个跨导(gm)单元,采用rz信号实现mux的功能,通过与门时钟与数据信号的相位关系实现1个数据单位时间间隔(unit interval,ui)的延时。

67.请参阅图5,对于主抽头(main tap),时钟的高电平与第一路数据做“与”运算,时

钟的低电平与第二路数据做“与”运算,次抽头(post tap)反之,从而构成一个两抽头的ffe。与门电路结构如图4所示,其中的电感不仅可以扩大带宽,而且可以保证归零信号中的零电平持续的时间更加接近1/2个ui。

68.与门电路:q1,q2的基极分别接差分输入的数据信号vip,vin,q3,q4的基极接直流电压vdc,差分输出的负载分别是电阻r1和电感l1以及电阻r2和电感l2的串联,q1和q3的集电极与r1相连并作为voutn输出,q2和q4的集电极与r2相连并作为voutp输出。q5,q6的基极分别接差分输入的时钟信号ckp,ckn,q5的集电极与q1,q2的发射极相连,q6的集电极与q3,q4的发射极相连,q5,q6的发射极与电流源管m1的漏极相连,m1的源极接地,栅极接偏置电压v

bias

。

69.跨导电路:q7,q8的基极分别接偏置电压v

biasp

和v

biasn

;q9,q10的基极分别接偏置电压v

biasn

和v

biasp

;q7,q9的集电极相连,作为电流i

outn

输出;q8,q10的集电极相连,作为电流i

outp

输出;q11,q12的基极分别接第一路数据的差分输入vin1p,vin1n;q13,q14的基极分别接第二路数据的差分输入vin2p,vin2n;q11,q13的集电极与q7,q8的发射极相连;q12,q14的集电极与q9,q10的发射极相连;q11的发射极与r3,c1相连,q12的发射极与r4,c2相连,q13的发射极与r5,c3相连,q14的发射极与r6,c4相连;电流源管m2,m3的栅极接偏置电压v

bias

;m2的漏极接r3,c1,r4和c2,m3的漏极接r5,c3,r6和c4;m2,m3的源极接地。

70.本发明一种100g以上相干光检测用高速模拟复用器电路,针对pam4信号完成了2:1的复用功能,实现了速率超过100gbaud的高速pam4信号传输,完成了电域的数据信号合成。之后4个amux产生的4路高速数据信号经过驱动放大器(driver)驱动4个马赫-曾德调制器(mach-zehnder modulator;mzm),随后在光子域经过2个iqm(i/q调制器),被合成为两路16-qam光信号,最后经过偏振光合束器合成为一路光信号(dp-16qam)送入光纤通道,完成光域的信号发射。

71.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中的描述和所示的本发明实施例的组件可以通过各种不同的配置来布置和设计。因此,以下对在附图中提供的本发明的实施例的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

72.跨导单元电路结构如图4所示,相比于传统的通过控制尾电流大小来调节抽头系数的方式,该gm单元可以针对pam4信号实现更好的线性度,其原理是在不改变尾电流源大小的情况下,通过调节cascode bjt管的偏置电压v

biasp

和v

biasn

的差值实现跨导的变化,从而实现抽头系数的调节。

73.当amux输入两路65gbaud的pam4信号时,输出为130gbaud的pam4信号,在有信道损耗的情况下,输出眼图如图6(a)所示,可以看出此时眼图中的眼睛已经闭合,在经过均衡后,输出眼图如图6(b)所示,此时眼图中的眼睛张开,高度为40mv,宽度为2.1ps,高速信号能够正确地传输。同现有技术相比,能够较好地满足实际应用需求。

74.本发明关于幅频响应的仿真结果如图7所示,能够看出3db带宽为63ghz,满足100gbaud以上输出数据信号的奈奎斯特带宽的要求。

75.本发明关于总谐波失真(total harmonic distortion,thd)的仿真结果如图8所示,横轴为输入信号摆幅,能够看出在输入信号频率为40ghz,50ghz及60ghz时,随着输入信号摆幅的增加,最差的thd也小于-30db,因此本发明取得了非常好的线性度。

76.综上所述,本发明一种100g以上相干光检测用高速模拟复用器,集成了注入锁定四倍频器,降低了对于外部测试所需时钟源速率的要求;针对pam4信号完成了2:1的复用功能,实现了速率超过100gbaud的高速pam4信号传输;引入由与门单元和跨导单元实现的前馈均衡技术,可以补偿板间互联信道在高频下的损耗。

77.以上内容仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明权利要求书的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。