1.本公开涉及电子技术领域,特别涉及一种激光投影设备。

背景技术:

2.激光投影设备可以包括系统级芯片、电源电路、复位芯片、多个供电组件和光阀控制芯片。其中,系统级芯片可以响应于开机操作,控制电源电路为复位芯片供电。并且,系统级芯片能够通过复位芯片控制多个供电组件依次向光阀控制芯片发送有效电平的电源正常信号、多个有效电源信号以及有效电平的电源感应信号,由此控制光阀控制芯片上电。

3.但是,由于需要通过多个供电组件控制光阀控制芯片上电,导致控制光阀控制芯片上电的电路较为复杂。

技术实现要素:

4.本公开实施例提供了一种激光投影设备,可以解决相关技术中控制光阀控制芯片上电的电路的问题。所述技术方案如下:

5.一方面,提供了一种激光投影设备,所述激光投影设备包括系统级芯片、电源电路、电源控制芯片、复位芯片、光阀控制芯片和电源转换电路;

6.所述系统级芯片分别与所述电源电路和所述电源控制芯片的第一输入端连接,所述系统级芯片用于响应于开机操作,控制电源电路为所述复位芯片供电,并向所述电源控制芯片发送开机信号;

7.所述复位芯片还与所述电源控制芯片的第二输入端和所述光阀控制芯片的第一输入端连接,所述复位芯片用于在上电后分别向所述电源控制芯片和所述光阀控制芯片发送有效电平的电源正常信号;

8.所述电源控制芯片用于响应于所述开机信号和所述电源正常信号,控制所述电源转换电路依次向所述光阀控制芯片发送多个有效电源信号,并用于向所述光阀控制芯片发送有效电平的电源感应信号,以控制所述光阀控制芯片上电。

9.另一方面,提供了一种激光投影设备,所述激光投影设备包括系统级芯片、电源电路、电源控制芯片、复位芯片、光阀控制芯片和电源转换电路;

10.所述系统级芯片分别与所述电源电路和所述电源控制芯片的第一输入端连接,所述系统级芯片用于响应于待机操作,控制电源电路停止为所述复位芯片供电,并向所述电源控制芯片发送待机信号;

11.所述电源控制芯片用于:

12.在所述复位芯片下电后通过所述第二输入端接收所述复位芯片输出的无效电平的电源正常信号;

13.响应于所述待机信号和所述电源正常信号,向所述光阀控制芯片发送无效电平的电源感应信号;

14.控制所述电源转换电路依次向所述光阀控制芯片发送多个无效电平的电源信号,

以控制所述光阀控制芯片下电。

15.本公开实施例提供的技术方案带来的有益效果至少包括:

16.本公开实施例提供了一种激光投影设备,激光投影设备中的系统级芯片可以响应于开机操作,控制复位芯片上电,并向电源控制芯片发送开机信号。复位芯片在上电后分别向电源控制芯片和光阀控制芯片发送有效电平的电源正常信号。由此电源控制芯片可以响应于该开机信号和电源正常信号,控制电源转换电路依次向光阀控制芯片发送多个有效电源信号,并向光阀控制芯片发送有效电平的电源感应信号,以控制光阀控制芯片上电。由于通过一个电源控制芯片和电源转换电路即可控制光阀控制芯片上电,因此简化了用于控制光阀控制芯片上电的电路,提高了激光投影设备内部器件的集成度,且降低了成本。

附图说明

17.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

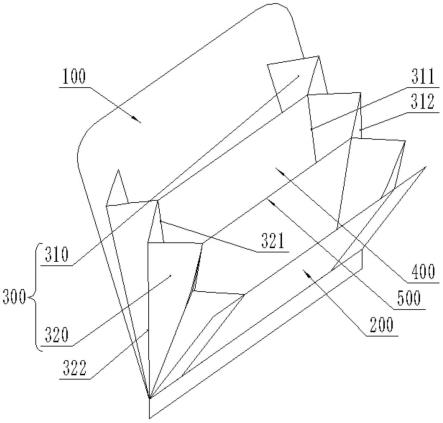

18.图1是本公开实施例提供了一种激光投影设备的结构示意图;

19.图2是本公开实施例提供了另一种激光投影设备的结构示意图;

20.图3是本公开实施例提供的一种电源控制芯片接收到的信号以及输出的信号的时序图;

21.图4是本公开实施例提供的一种第一转换电路的结构示意图;

22.图5是本公开实施例提供的一种第二转换电路的结构示意图;

23.图6是本公开实施例提供的一种第三转换电路的结构示意图;

24.图7是本公开实施例提供了再一种激光投影设备的结构示意图;

25.图8是本公开实施例提供的一种激光投影设备的控制方法的流程图;

26.图9是相关技术提供的一种激光投影设备的结构示意图;

27.图10是相关技术提供的一种激光投影设备的控制方法的流程图;

28.图11是相关技术提供的一种第一时序控制芯片接收到的信号以及输出的信号的时序图;

29.图12是本公开实施例提供了又一种激光投影设备的结构示意图;

30.图13是本公开实施例提供的一种电源控制芯片接收到的信号以及输出的信号的时序图;

31.图14是本公开实施例提供的镜片在开启状态和关闭状态的示意图;

32.图15是本公开实施例提供的镜片在初始状态的示意图;

33.图16是本公开实施例提供的另一种激光投影设备的控制方法的流程图;

34.图17是相关技术提供的另一种激光投影设备的控制方法的流程图;

35.图18是相关技术提供的一种第一时序控制芯片接收到的信号以及输出的信号的时序图;

36.图19是本公开实施例提供了一种激光投影设备的开机过程的流程图;

37.图20是本公开实施例提供了一种激光投影设备的待机过程的流程图。

具体实施方式

38.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

39.图1是本公开实施例提供了一种激光投影设备的结构示意图,如图1所示,该激光投影设备包括系统级芯片(system on chip,soc)10、电源电路20、电源控制芯片30、复位芯片40、光阀控制芯片50和电源转换电路60。该激光投影设备可以为小型化激光投影设备。

40.其中,该电源控制芯片30可以为可编程逻辑芯片。可选的,该电源控制芯片30可以为单片机、现场可编程门阵列(field programmable gate array,fpga)或者复杂可编程逻辑器件(complex programmable logic device,cpld)。该光阀控制芯片50可以为数字光处理芯片(digital light processing chip,dlpc)。

41.参考图1和图2,系统级芯片10分别与电源电路20和电源控制芯片30的第一输入端x1连接,该电源电路20还与复位芯片40连接。系统级芯片10用于响应于开机操作,控制电源电路20为复位芯片40供电,并向电源控制芯片30发送开机信号。

42.可选的,该开机操作可以是针对开机按钮的选中操作。其中该开机按钮可以位于激光投影设备,也可以位于用于控制激光投影设备的遥控器上。该开机信号可以为高电平信号。

43.参考图2,复位芯片40还与电源控制芯片30的第二输入端x2和光阀控制芯片50的第一输入端z1连接,该复位芯片40用于在上电后分别向电源控制芯片30和光阀控制芯片50发送有效电平的电源正常(power good,pwrgood)信号。其中,该有效电平可以为高电平,该有效电平的电源正常信号指的是高电平信号,示例的,该有效电平的电源正常信号指的是高电平信号的电压可以为3.3伏(volt,v)。

44.在本公开实施例中,该系统级芯片10通过控制电源电路20为复位芯片40供电,由此实现控制复位芯片40上电。该复位芯片40上可以设置有复位(reset)引脚,该复位引脚分别与电源控制芯片30的第二输入端x2和光阀控制芯片50的第一输入端z1连接。该电源控制芯片30的第二输入端x2和光阀控制芯片50的第一输入端z1均可以为pwrgood引脚,即均用于接收电源正常信号。

45.在电源电路20为复位芯片40供电后,即复位芯片40上电后,该复位芯片40的复位引脚可以输出有效电平的电源正常信号。

46.电源控制芯片30还分别与电源转换电路60和光阀控制芯片50连接,该电源转换电路60还与光阀控制芯片50连接。电源控制芯片30用于响应于开机信号和有效电平的电源正常信号,控制电源转换电路60依次向光阀控制芯片50发送多个有效电源信号,并用于向光阀控制芯片50发送有效电平的电源感应信号,以控制光阀控制芯片50上电。

47.其中,该多个有效电源信号均可以为高电平的电源信号,且该多个有效电源信号的电压可以不同。该有效电平的电源感应信号可以为高电平信号,示例的,该有效电平的电源感应信号的电压可以为3.3v。该电源感应信号可以为上电感应(power on sense,posense)信号。

48.电源控制芯片30可以响应于开机信号和电源正常信号,控制电源转换电路60依次向光阀控制芯片50发送多个有效电源信号。并在将多个有效电源信号均发送至光阀控制芯片50后,电源控制芯片30可以向该光阀控制芯片50发送有效电平的电源感应信号,由此实

现控制光阀控制芯片50上电。光阀控制芯片50在依次接收到有效电平的电源正常信号、多个有效电源信号以及有效电平的电源感应信号后,可以确定供电正常。之后,光阀控制芯片50在内部程序初始化完成后,可以控制光阀翻转,以实现投影图像的显示。

49.综上所述,本公开实施例提供了一种激光投影设备,激光投影设备中的系统级芯片可以响应于开机操作,控制复位芯片上电,并向电源控制芯片发送开机信号。复位芯片在上电后分别向电源控制芯片和光阀控制芯片发送有效电平的电源正常信号。由此电源控制芯片可以响应于该开机信号和电源正常信号,控制电源转换电路依次向光阀控制芯片发送多个有效电源信号,并向光阀控制芯片发送有效电平的电源感应信号,以控制光阀控制芯片上电。由于通过一个电源控制芯片和电源转换电路即可控制光阀控制芯片上电,因此简化了用于控制光阀控制芯片上电的电路,提高了激光投影设备内部器件的集成度,且降低了成本。

50.参考图1,该激光投影设备还可以包括主板100和显示板200。该系统级芯片10位于主板100上。该电源控制芯片30、复位芯片40、光阀控制芯片50和电源转换电路60均位于显示板200上。

51.在本公开实施例中,该电源控制芯片30用于响应于开机信号和电源正常信号,向电源转换电路60发送有效使能信号,该电源转换电路60用于响应于该有效使能信号依次向光阀控制芯片50发送多个有效电源信号,并向电源控制芯片30发送有效控制信号。该电源控制芯片30用于响应于有效控制信号向光阀控制芯片50发送电源感应信号。其中,有效使能信号和有效控制信号均可以为高电平信号。

52.示例的,该电源转换电路60可以依次向光阀控制芯片50发送四个有效电源信号。

53.参考图2,该电源转换电路60可以包括第一转换电路61、多个第二转换电路62和第三转换电路63。示例的,该多个第二转换电路62的个数可以为两个。

54.该电源控制芯片30的第一输出端y1与第一转换电路61的输入端连接,第一转换电路61的输出端分别与光阀控制芯片50的第二输入端z2和电源控制芯片30的第三输入端x3连接。

55.表1示出了在控制光阀控制芯片50上电过程中,电源控制芯片30所要接收的信号,以及输出的信号,该第一有效控制信号至第三有效控制信号均可以为高电平信号,多个有效电源信号可以包括第一有效电源信号pwr1至第三有效电源信号pwr3。参考表1、图2和图3,电源控制芯片30用于在接收到开机信号和电源正常信号的时长为第一时长t1后,向第一转换电路61发送有效使能信号en1。该第一转换电路61用于响应于该有效使能信号en1,向光阀控制芯片50的第二输入端z2发送第一有效电源信号pwr1,并向电源控制芯片30的第三输入端x3发送第一有效控制信号pg1。其中,该第一有效电源信号pwr1和第一有效控制信号pg1均可以为高电平信号。该第一时长t1可以为电源控制芯片30中预先存储的固定时长,示例的,该第一时长t1可以为10毫秒(ms)。该第一有效电源信号pwr1的电压可以为1.15v。

56.表1

[0057][0058]

该光阀控制芯片50的第二输入端z2接收的第一有效电源信号pwr1可以用于为光阀控制芯片中核心功能接口供电。例如该核心功能接口可以包括v-by-one接口和向光阀输出高速信号的接口。其中该高速信号可以为控制光阀翻转的控制信号。

[0059]

可选的,电源控制芯片30可以在其第一输入端x1接收到开机信号,以及其第二输入端x2接收到电源正常信号之后,启动定时器,并在该定时器的计时时长为第一时长t1后,将该定时器清0,并通过该第一输出端y1向第一转换电路61的输入端发送有效使能信号en1。

[0060]

电源控制芯片30可以具有第二输出端y2和多个第四输入端x4,光阀控制芯片50具有多个第三输入端z3,电源控制芯片30的第二输出端y2与多个第二转换电路62的输入端连接,该多个第二转换电路62的输出端分别与光阀控制芯片50的多个第三输入端z3和电源控制芯片30的多个第四输入端x4一一对应连接。

[0061]

示例的,参考图2,电源控制芯片30可以具有2个第四输入端x4,该多个第二转换电路62可以包括第一个第二转换电路62和第二个第二转换电路62。

[0062]

电源控制芯片30用于在接收到第一有效控制信号pg1的时长为第二时长t2后,向每个第二转换电路62发送有效使能信号en2。每个第二转换电路62用于响应于该有效使能信号en2,向对应的第三输入端z3发送一个第二有效电源信号pwr2,并向对应的第四输入端x4发送第二有效控制信号pg2。其中,该每个第二有效控制信号可以为高电平信号。该第二时长t2可以为电源控制芯片30中预先存储的固定时长,示例的,该第二时长t2可以为10ms。

[0063]

若电源控制芯片30可以具有2个第四输入端x4,该多个第二转换电路62可以包括第一个第二转换电路62和第二个第二转换电路62,则电源控制芯片30的第三输入端x3在接收到第一个有效控制信号pg1后可以再次启动定时器,在该定时器的计时时长为第二时长t2后,可以将该定时器清0,并分别向第一个第二转换电路62和第二个第二转换电路62发送有效使能信号en2。

[0064]

该第一个第二转换电路62用于响应于接收到的有效使能信号en2,向对应的第三输入端z3发送一个第二有效电源信号pwr2,并向电源控制芯片30的一个第四输入端x4发送一个第二有效控制信号pg2。该第二个第二转换电路62用于响应于接收到的有效使能信号en2,向对应的第三输入端z3发送另一个第二有效电源信号pwr2,并向电源控制芯片30的另一个第四输入端x4发送另一个第二有效控制信号pg2。示例的,该一个第二有效电源信号pwr2的电压可以为1.8v,该另一个第二有效电源信号pwr2的电压可以为3.3v。

[0065]

若光阀控制芯片50具有两个第三输入端z3,则该光阀控制芯片50的一个第三输入

端z2接收的第二有效电源信号pwr2可以用于为v-by-one接口和向光阀输出低速信号的接口供电。其中该低速信号可以为用于配置光阀的信号,例如配置光阀上的镜片的角度。该光阀控制芯片50的另一个第三输入端z2接收的第二有效电源信号pwr2可以用于为向光阀输出低速信号的接口和存储接口供电。其中该低速信号可以为控制光阀翻转的控制信号。其中,该存储接口可以为用于连接激光投影设备的程序存储组件的接口。

[0066]

电源控制芯片30的第三输出端y3与第三转换电路63的输入端连接,该第三转换电路63的输出端分别与光阀控制芯片50的第四输入端z4和电源控制芯片30的第五输入端x5连接,电源控制芯片30的第四输出端y4与光阀控制芯片50的第五输入端z5连接。

[0067]

该电源控制芯片30用于在接收到多个第二有效控制信号pg2的第三时长t3后,向第三转换电路63发送有效使能信号en3,该第三转换电路63用于响应于有效使能信号en3,向光阀控制芯片50发送第三有效电源信号pwr3,并向电源控制芯片30发送第三有效控制信号pg3。该电源控制芯片30用于在接收到第三有效控制信号pg3的第四时长t4后,向光阀控制芯片50发送有效电平的电源感应信号。

[0068]

其中,该光阀控制芯片50的第四输入端z4接收的第三有效电源信号pwr3可以用于为存储接口供电。第三有效控制信号pg3可以为高电平信号,该第三时长t3和第四时长t4均可以为电源控制芯片30中预先存储的固定时长,示例的,该第三时长t3可以为10ms,该第四时长t4可以为20ms。该第三有效电源信号pwr3的电压可以为1.21v。

[0069]

电源控制芯片30通过其多个第三输入端x3在接收到多个第二有效控制信号pg2后,可以再次启动定时器,在该定时器的计时时长为第三时长t3后,将该定时器清0,并通过其第三输出端y3向第三转换电路63发送有效使能信号en3。并且,该电源控制芯片30在通过其第五输入端x5接收到第三有效控制信号pg3后,可以再次启动该定时器,在该定时器的计时时长为第四时长t4后,将该定时器清0,并通过其第四输出端y4向光阀控制芯片50的第五输入端z5发送有效电平的电源感应信号。

[0070]

在本公开实施例中,该光阀控制芯片50的第五输入端z5也可以称为posense引脚,该引脚用于接收电源感应信号。上述第一有效控制信号pg1至第三有效控制信号pg3的电压可以为3.3v。

[0071]

参考图2,电源控制芯片30还具有第一电源端vc1和第一接地端g1。

[0072]

参考图4,第一转换电路61可以包括第一转换芯片d1、第一电容c1、第二电容c2、第三电容c3、第四电容c4、第一电阻r1、第一电感l1、第五电容c5、第六电容c6、第七电容c7、第二电阻r2、第三电阻r3和第八电容c8。

[0073]

其中,该第一转换芯片d1可以为直流(direct current,dc)/dc转换器。第一转换芯片d1具有使能端en、电源正常端pg、第二电源端vc2、升压端vbst、开关控制端sw和输出端反馈端fb。

[0074]

该第一转换芯片d1的使能端en与电源控制芯片30的第一输出端y1连接,即该第一转换芯片d1的使能端en为该第一转换电路61的输入端。第一转换芯片d1的电源正常端pg分别与电源控制芯片30的第三输入端x3和第一电阻r1的一端连接,即该第一转换芯片d1的电源正常端pg为该第一转换电路61的一个输出端。该第一电阻r1的另一端与电源端vd1连接。

[0075]

该第一转换芯片d1的第二电源端vc2与第一电容c1的一端、第二电容c2的一端和第三电容c3的一端连接,第一电容c1的另一端与第二接地端g2连接,第二电容c2的另一端

与第三接地端g3连接,第三电容c3的另一端与第四接地端g4连接。

[0076]

第一转换芯片d1的升压端vbst与第四电容c4的一端连接,第一转换芯片d1的开关控制端sw分别与第四电容c4的另一端和第一电感l1的一端连接。该第一电感l1的另一端分别与第五电容c5的一端、第六电容c6的一端、第七电容c7的一端、第二电阻r2的一端、第八电容c8的一端和光阀控制芯片50的第二输入端z2连接。也即是该第一电感l1的另一端为该第一转换电路61的另一个输出端。该第五电容c5的另一端、第六电容c6的另一端和第七电容c7的另一端均与第五接地端g5连接。

[0077]

第一转换芯片d1的输出端反馈端fb与第二电阻r2的另一端和第三电阻r3的一端连接,第三电阻r3的另一端与第六接地端g6连接。第八电容c8的另一端与第七接地端g7连接。

[0078]

参考图4,该第一转换芯片d1还具有第八接地端g8。

[0079]

参考图5,每个第二转换电路62可以包括第二转换芯片d2、第九电容c9、第十电容c10、第十一电容c11、第十二电容c12、第四电阻r4、第二电感l2、第十三电容c13、第十四电容c14、第十五电容c15、第五电阻r5、第六电阻r6和第十六电容c16。

[0080]

其中,该第二转换芯片d2可以为dc/dc转换器,第二转换芯片d2具有使能端en、电源正常端pg、第三电源端vc3、升压端vbst、开关控制端sw和输出端反馈端fb。

[0081]

该第二转换芯片d2的使能端en与电源控制芯片30的第二输出端y2连接,即该第二转换芯片d2的使能端en为该第二转换电路62的输入端。第二转换芯片d2的电源正常端pg分别与电源控制芯片30的第四输入端x4和第四电阻r4的一端连接,即该第二转换芯片d2的电源正常端pg为该第二转换电路62的一个输出端。该第四电阻的另一端与电源端vd2连接。

[0082]

该第三电源端vc3与第九电容c9的一端、第十电容c10的一端和第十一电容c11的一端连接,第九电容c9的另一端与第九接地端g9连接,第十电容c10的另一端与第十接地端g10连接,第十一电容c11的另一端与第十一接地端g11连接。

[0083]

第二转换芯片d2的升压端vbst与第十二电容c12的一端连接,第二转换芯片d2的开关控制端sw分别与第十二电容c12的另一端和第二电感l2的一端连接。该第二电感l2的另一端分别与第十三电容c13的一端、第十四电容c14的一端、第十五电容c15的一端、第五电阻r5的一端、第十六电容c16的一端和光阀控制芯片50的第三输入端z3连接。也即是该第二电感l2的另一端为该第二转换电路62的另一个输出端。该第十三电容c13的另一端、第十四电容c14的另一端和第十五电容c15的另一端均与第十二接地端g12连接。

[0084]

第二转换芯片d2的输出端反馈端fb与第五电阻r5的另一端和第六电阻r6的一端连接,第六电阻r6的另一端与第十三接地端g13连接,第十六电容c16的另一端与第十四接地端g14连接。参考图5,该第二转换芯片d2还具有第十五接地端g15。

[0085]

参考图6,每个第三转换电路63可以包括第三转换芯片d3、第十七电容c17、第十八电容c18、第十九电容c19、第二十电容c20、第七电阻r7、第三电感l3、第二十一电容c21、第二十二电容c22、第二十三电容c23、第八电阻r8、第九电阻r9和第二十四电容c24。

[0086]

其中,该第三转换芯片d3可以为dc/dc转换器,第三转换芯片d3具有使能端en、电源正常端pg、第三电源端vc3、升压端vbst、开关控制端sw和输出端反馈端fb。

[0087]

该第三转换芯片d3的使能端en与电源控制芯片30的第三输出端y3连接,即该第三转换芯片d3的使能端en为该第三转换电路63的输入端。第三转换芯片d3的电源正常端pg分

别与电源控制芯片30的第五输入端x5和第七电阻r7的一端连接,即该第三转换芯片d3的电源正常端pg为该第三转换电路63的一个输出端。该第七电阻的另一端与电源端vd3连接。

[0088]

该第四电源端vc4与第十七电容c17的一端、第十八电容c18的一端和第十九电容c19的一端连接,第十七电容c17的另一端与第十六接地端g16连接,第十八电容c18的另一端与第十七接地端g17连接,第十九电容c19的另一端与第十八接地端g18连接。第三转换芯片d3的升压端vbst与第二十电容c20的一端连接,第三转换芯片d3的开关控制端sw分别与第二十电容c20的另一端和第三电感l3的一端连接。该第三电感l3的另一端分别与第二十一电容c21的一端、第二十二电容c22的一端、第二十三电容c23的一端、第八电阻r8的一端、第二十四电容c24的一端和光阀控制芯片50的第四输入端z4连接。也即是该第三电感l3的另一端也为该第三转换电路63的另一个输出端。该第二十一电容c21的另一端、第二十二电容c22的另一端和第二十三电容c23的另一端均与第十九接地端g19连接。第三转换芯片d3的输出端反馈端fb与第八电阻r8的另一端和第九电阻r9的一端连接,第九电阻r9的另一端与第二十接地端g20连接,第二十四电容c24的另一端与第二十一接地端g21连接。参考图6,该第三转换芯片d3还具有第二十二接地端g22。

[0089]

在本公开实施例中,上述电源端vd1至电源端vd3均为vdd电源端。上述第一电源端vc1可以为vdd电源端,第二电源端vc2至第四电源端vc4均为vcc电源端。上述第一转换芯片d1至第三转换芯片d3的电源正常端pg均可以为pwrgood引脚。

[0090]

在本公开实施例中,参考图7,该电源电路20可以包括电源板21和分压电路22。该电源板21分别与系统级芯片10和分压电路22的输入端连接,该分压电阻22的输出端与复位芯片40连接。可选的,该分压电路22可以包括分压电阻。系统级芯片10可以响应于开机操作,向电源板21发送开机指令。该电源板21可以响应于该开机指令,向分压电路22发送第一电压。该分压电路22将该第一电压降低至第二电压传输至复位芯片40,由此实现该复位芯片40的上电。该复位芯片40在接收到该第二电压后,向电源控制芯片30和光阀控制芯片50发送有效电平的电源正常信号。示例的,该第一电压可以为12v,第二电压可以为3.3v。参考图7,该电源电路20还可以包括第一电源开关sw1,该第一电源开关sw1的控制端与系统级芯片10连接。该第一电源开关sw1的第一端与电源板21连接,该第一电源开关sw1的第二端分别与第一转换芯片d1的第二电源端vc2、每个第二转换芯片d2的第三电源端vc3和第三转换芯片d3的第四电源端vc4连接。该系统级芯片10可以响应于开机操作,向第一电源开关sw1的控制端输出有效使能信号,以使得第一电源开关sw1的第一端与第二端导通,由此实现控制电源板21为第一转换芯片d1、每个第二转换芯片d2和第三转换芯片d3供电。

[0091]

本公开实施例中,该激光投影设备还可以包括电源转换器,该电源转换器可以为dc/dc。该电源转换器分别与第一电源开关sw1的第二端和电源控制芯片30的第一电源端vc1连接。该电源转换器用于将电源板21发送第一电压转成目标电压传输至电源控制芯片30。示例的,该目标电压可以为3.3v。在第一电源开关sw1的第一端与第二端导通后,该电源板21还可以为电源控制芯片30供电。

[0092]

参考图2和图7,该激光投影设备还可以包括与光阀控制芯片50连接的光阀70,该光阀控制芯片50还与电源控制芯片30的第六输入端x6连接。光阀控制芯片50用于在上电后控制光阀70上电,并在光阀70上电成功后向电源控制芯片30的第六输入端x6发送上电成功信号,该上电成功信号用于指示光阀70上电成功。其中,该上电成功信号可以为高电平信

号。

[0093]

参考图7,该激光投影设备还可以包括分别与电源电路20、光阀控制芯片50和光阀70连接的光阀供电芯片80。该系统级芯片10还可以响应于开机操作,控制电源电路20为光阀供电芯片80供电。该光阀控制芯片50在上电后,可以向光阀供电芯片80发送有效使能信号,进而光阀供电芯片80可以在该有效使能信号的控制下,为光阀70供电。

[0094]

第一电源开关sw1的第二端还与光阀供电芯片80连接。在第一电源开关sw1的第一端与第二端导通后,该电源板21还可以为光阀供电芯片80供电。

[0095]

在本公开实施例中,光阀供电芯片80可以依次向光阀70发送多个有效电源信号、电压偏置(voltage bias,vbias)信号,电压复位(voltage reset,vrst)信号和电压补偿(voltage offset,vofs)信号,由此实现为光阀上电。其中,该多个有效电源信号的电压、电压偏置信号的电压,电压复位信号的电压和电压补偿信号的电压不同。示例的,该多个有效电源信号的个数可以为两个,该两个有效电源信号的电压可以分别为1.15v和1.8v。该电压偏置信号的电压可以为18v,该电压复位信号的电压可以为-14v,该电压补偿信号的电压可以为10v。

[0096]

参考图7,激光投影设备还可以包括插座q,该插座q分别与光阀供电芯片80和光阀70连接,且该插座q位于显示板200上。该光阀供电芯片80可以通过该插座q依次将多个有效电源信号、电压偏置信号,电压复位信号和电压补偿信号发送至光阀70。

[0097]

光阀控制芯片50在向光阀供电芯片80发送有效使能信号的预设时长后,可以向光阀70发送通信信号,若接收到光阀70发送的响应信号,则可以确定该光阀上电成功,进而光阀控制芯片50可以向电源控制芯片30的第六输入端x6发送上电成功信号。光阀控制芯片50若未接收到光阀70发送的响应信号,则可以确定该光阀70上电失败,进而光阀控制芯片50可以向电源控制芯片30的第六输入端x6发送上电失败信号。电源控制芯片30用于若通过第六输入端x6检测到光阀控制芯片50输出的上电失败信号,则可以重新执行上电流程,如再次控制电源转换电路60依次向光阀控制芯片50发送多个有效电源信号,并向光阀控制芯片50发送有效电平的电源感应信号,以再次控制光阀控制芯片50上电。其中,该上电失败信号用于指示光阀70上电失败。

[0098]

可选的,电源控制芯片30可以再次响应于开机信号和有效电平的电源正常信号向第一转换电路61发送有效使能信号。

[0099]

参考图8,本公开实施例中光阀控制芯片50的上电过程可以包括以下步骤:

[0100]

步骤801、系统级芯片响应于开机操作,控制电源电路为复位芯片供电,并向电源控制芯片发送开机信号。

[0101]

步骤802、电源控制芯片在接收到开机信号和电源正常信号的第一时长后,向第一转换电路发送有效使能信号。

[0102]

步骤803、第一转换电路响应于有效使能信号,向光阀控制芯片发送第一有效电源信号,并向电源控制芯片发送第一有效控制信号。

[0103]

步骤804、电源控制芯片在接收到第一有效控制信号的第二时长后,向每个第二转换电路发送有效使能信号。

[0104]

步骤805、每个第二转换电路响应于该有效使能信号,向对应的第三输入端发送一个第二有效电源信号,并向对应的第四输入端发送第二有效控制信号。

[0105]

步骤806、电源控制芯片在接收到多个第二有效控制信号的第三时长后,向第三转换电路发送有效使能信号。

[0106]

步骤807、第三转换电路响应于有效使能信号,向光阀控制芯片发送第三有效电源信号,并向电源控制芯片发送第三有效控制信号。

[0107]

步骤808、电源控制芯片在接收到第三有效控制信号的第四时长后,向光阀控制芯片发送有效电平的电源感应信号。

[0108]

步骤809、光阀控制芯片在上电后控制光阀上电,并在光阀上电成功后向电源控制芯片的第六输入端发送上电成功信号。

[0109]

步骤810、电源控制芯片若通过第六输入端检测到光阀控制芯片输出的上电失败信号,则重新执行上电流程。

[0110]

激光投影设备通常可以包括系统级芯片、复位芯片r、电源电路、多个时序控制芯片、多个逻辑器件、电源转换电路和光阀控制芯片。系统级芯片可以响应于开机操作,控制电源电路为复位芯片供电,并通过复位芯片控制多个时序控制芯片、多个逻辑器件和电源转换电路依次向光阀控制芯片发送有效电平的电源正常信号、多个有效电源信号以及有效电平的电源感应信号,由此控制光阀控制芯片上电。但是,由于需要通过多个时序控制芯片、多个逻辑器件和电源转换电路控制光阀控制芯片上电,导致控制光阀控制芯片上电的电路较为复杂。

[0111]

其中,参考图9,多个时序控制芯片可以包括第一时序控制芯片lm1和第二时序控制芯片lm2。示例的,该第一时序控制芯片lm1和第二时序控制芯片lm2均可以为lm3880芯片。在本公开实施例中,电源控制芯片中可以集成有图9所示的多个时序控制芯片和多个逻辑器件。多个逻辑器件可以包括第一逻辑与器件n1、第二逻辑与器件n2、第三逻辑与器件n3、第四逻辑与器件n4、第五逻辑与器件n5、第六逻辑与器件n6、第七逻辑与器件n7、第八逻辑与器件n8、第一逻辑或器件k1、第二逻辑或器件k2、第一逻辑非器件f1和第二逻辑非器件f2。

[0112]

系统级芯片与第一逻辑与器件n1的第一输入端连接,复位芯片分别与电源电路、第一逻辑与器件n1的第二输入端和光阀控制芯片连接。该系统级芯片用于响应于开机操作,控制电源电路为复位芯片供电,并向第一逻辑与器件发送开机信号。该复位芯片r1用于在上电后向第一逻辑与器件n1发送有效电平的电源正常信号。第一逻辑与器件n1的输出端分别与第一逻辑或器件k1的第一输入端、第二逻辑与器件n2的第一输入端和第一逻辑非器件f1的输入端连接。该第一逻辑与器件n1用于分别向第一逻辑或器件k1的第一输入端、第二逻辑与器件n2的第一输入端和第一逻辑非器件f1输出高电平信号。第一逻辑或器件k1的输出端与第一时序控制芯片lm1的使能端连接,第一逻辑或器件k1用于向第一时序控制芯片lm1的使能端输出有效使能信号。

[0113]

第一时序控制芯片lm1的第一输出端f11与第一转换电路的输入端连接,该第一时序控制芯片lm1的第二输出端f12与第二逻辑与器件n2的第二输入端和第三逻辑与器件n3的第一输入端连接,该第一时序控制芯片lm1的第三输出端f13与第四逻辑与器件n4的第一输入端连接。参考图11,该第一时序控制芯片lm1在接收到有效使能信号en1的时长为第一目标时长t1后,通过第一输出端f11向第一转换电路61的输入端输出有效使能信号en2,在接收到有效使能信号en1的时长为第二目标时长t2后,通过第二输出端f12向第二逻辑与器

件n2的第二输入端和第三逻辑与器件n3的第一输入端输出高电平信号f1,以及在接收到有效使能信号en1的时长为第三目标时长t3后,通过第三输出端f13向第四逻辑与器件n4的第一输入端输出高电平信号f2。示例的,第一目标时长可以为10ms,第二目标时长可以为20ms,该第三目标时长可以为30ms。

[0114]

该第一转换电路61的输出端分别与光阀控制芯片和第三逻辑与器件n3的第二输入端连接,该第三逻辑与器件n3的输出端与第一个第二转换电路62的输入端和第二个第二转换电路的输入端连接。第一个第二转换电路62的输出端与第五逻辑与器件n5的第一输入端连接,第二个第二转换电路62的输出端与第五逻辑与器件n5的第二输入端连接。该第一转换电路61用于响应于接收到的有效使能信号,向光阀控制芯片输出第一有效电源信号,并向第三逻辑与器件n3的第一输入端输出第一有效控制信号pg1。

[0115]

第三逻辑与器件n3用于分别向第一个第二转换电路62和第二个第二转换电路62输出有效使能信号。该第一个第二转换电路62用于响应于接收到的有效使能信号,向光阀控制芯片输出第二有效电源信号pwr2,并向第五逻辑与器件n5的第一输入端输出第二有效控制信号pg2。第二个第二转换电路62用于响应于接收到的有效使能信号,向第五逻辑与器件n5的第二输入端输出第二有效控制信号pg2。

[0116]

该第五逻辑与器件n5的输出端与第四逻辑与器件n4的第二输入端连接,该第五逻辑与器件n5用于向第四逻辑与器件n4的第二输入端输出高电平信号。

[0117]

第四逻辑与器件n4的输出端与第三转换电路的第四输入端连接,该第四逻辑与器件n4用于向第三转换电路输出有效使能信号。

[0118]

该第三转换电路的输出端与第六逻辑与器件n6的第一输入端连接,该第三转换电路用于响应于该接收到的有效使能信号,向第六逻辑与器件n6的第一输入端输出第三有效控制信号pg3。

[0119]

第二时序控制芯片lm2具有使能端en、第一输出端f21、第一输出端f22和第三输出端f23。第二逻辑与器件n2的输出端与第二时序控制芯片lm2的使能端en连接,第二逻辑与器件n2用于向第二时序控制芯片lm2的使能端en输出高电平信号。

[0120]

第二时序控制芯片lm2的第一输出端f21与第七逻辑与器件n7的第一输入端连接,该第二时序控制芯片lm2的第三输出端f23与第八逻辑与器件n8的第一输入端连接。

[0121]

第二时序控制芯片lm2用于通过其第一输出端f21,通过其第二输出端f22输出高电平信号,以及通过其第三输出端f23向第八逻辑与器件n8的第一输入端输出高电平信号。

[0122]

第二时序控制芯片lm2向第七逻辑与器件n7的第一输入端输出高电平信号时,第一时序控制芯片lm1接收到有效使能信号en1的时长为第四目标时长。示例的,第四目标时长可以为30ms。

[0123]

第二时序控制芯片lm2的第二输出端f22输出高电平信号时,第一时序控制芯片lm1接收到有效使能信号en1的时长为第五目标时长。示例的,第五目标时长可以为40ms。

[0124]

第二时序控制芯片lm2通过其第三输出端f23向第八逻辑与器件n8的第一输入端输出高电平信号时,第一时序控制芯片lm1接收到有效使能信号en1的时长为第六目标时长。示例的,第六目标时长为50ms。

[0125]

第七逻辑与器件n7的第二输入端与第一逻辑非器件f1的输出端连接,第七逻辑与器件n7的第二输入端用于接收第一逻辑非器件f1输出的低电平信号。

[0126]

第八逻辑与器件n8的第二输入端与第二逻辑非器件f2的输出端连接,该第二逻辑非器件f2的输入端与第一逻辑非器件f1的输出端连接,该第八逻辑与器件n8的第二输入端用于接收第二逻辑非器件f2输出的高电平信号。

[0127]

第七逻辑与器件n7的输出端与第二逻辑或器件k2的第一输入端连接,第八逻辑与器件n8的输出端与第二逻辑或器件k2的第二输入端连接,第二逻辑或器件k2的输出端与第六逻辑与器件n6的第二输入端连接,该第六逻辑与器件n6的输出端与光阀控制芯片连接。

[0128]

第七逻辑与器件n7用于向第二逻辑或器件k2的第一输入端输出低电平信号,第八逻辑与器件n8用于向第二逻辑或器件k2的第二输入端输出高电平信号,第二逻辑或器件k2用于向第六逻辑与器件n6的第二输入端输出高电平信号。

[0129]

第六逻辑与器件n6用于在其第一输入端接收到第四转换电路输出的第三有效控制信号pg4,以及其第二输入端接收到向第二逻辑或器件k2输出的高电平信号后,向光阀控制芯片输出有效电平的电源感应信号。

[0130]

参考图10,图9所示的电路控制光阀控制芯片的上电过程可以包括以下步骤:

[0131]

步骤1001、系统级芯片响应于开机操作,控制电源电路为复位芯片r1供电,并向第一逻辑与器件n1输出开机信号,以使复位芯片r1在上电后向第一逻辑与器件n1输出有效电平的电源正常信号。

[0132]

步骤1002、第一逻辑与器件n1向第一逻辑或器件k1、第二逻辑与器件n2的第一输入端和第一逻辑非器件f1输出高电平信号,以使第一逻辑或器件k1向第一时序控制芯片lm1的使能端输出有效使能信号。

[0133]

步骤1003、第一时序控制芯片lm1在第一目标时长后,向第一转换电路输出有效使能信号,以使能第一转换电路向光阀控制芯片输出第一有效电源信号,并向第三逻辑与器件n3输出第一有效控制信号。

[0134]

步骤1004、第一时序控制芯片lm1在第二目标时长后向第二逻辑与器件n2和第三逻辑与器件n3输出高电平信号。

[0135]

步骤1005、第三逻辑与器件n3向每个第二转换电路输出有效使能信号,以使能每个第二转换电路向光阀控制芯片输出一个第二有效电源信号,以及使能每个第二转换电路向第五逻辑与器件n5输出一个第二有效控制信号。

[0136]

步骤1006、第五逻辑与器件n5向第四逻辑与器件n4输出高电平信号。

[0137]

步骤1007、第一时序控制芯片lm1在第三目标时长后向第四逻辑与器件n4输出高电平信号。

[0138]

步骤1008、第四逻辑与器件n4向第三转换电路输出有效使能信号,以使能第三转换电路向第六逻辑与器件n6输出第三有效控制信号。

[0139]

步骤1009、第二逻辑与器件n2向第二时序控制芯片lm2的使能端输出高电平信号,以使能第二时序控制芯片lm2向第七逻辑与器件n7输出高电平信号,并向第八逻辑与器件n8输出高电平信号。

[0140]

步骤1010、第七逻辑与器件n7和第八逻辑与器件n8均向第二逻辑或器件k2输出高电平信号。

[0141]

步骤1011、第二逻辑或器件k2向第六逻辑与器件n6输出高电平信号,以使第六逻辑与器件n6在接收到第三有效控制信号和该高电平信号后,向光阀控制芯片输出有效电平

的电源感应信号。

[0142]

以下对光阀控制芯片50下电的过程进行说明:

[0143]

在本公开实施例中,系统级芯片10用于响应于待机操作,控制电源电路20停止为复位芯片40供电,并向电源控制芯片30发送待机信号。其中,该待机操作可以是针对待机按钮或这关机按钮的选中操作。其中该待机按钮和关机按钮可以位于激光投影设备,也可以位于用于控制激光投影设备的遥控器上。该待机信号可以为低电平信号。

[0144]

在本公开实施例中,系统级芯片10可以响应于待机操作,向电源板21发送待机指令。该电源板21可以响应于该待机指令,向分压电路22发送第三电压。该分压电路22将该第三电压降低至第四电压传输至复位芯片40,该复位芯片40在接收到该第四电压后下电。其中,第三电压小于第一电压,第四电压小于第二电压。示例的,该第三电压可以为9v。

[0145]

该电源控制芯片30用于在复位芯片40下电后通过第二输入端x2接收复位芯片40输出的无效电平的电源正常信号,响应于该待机信号和无效电平的电源正常信号,向光阀控制芯片50发送无效电平的电源感应信号,以及控制电源转换电路60依次向光阀控制芯片50发送多个无效电平的电源信号,以控制光阀控制芯片50下电。其中,无效电平指的是低电平。该无效电平的电源正常信号和无效电平的电源感应信号均可以为低电平信号。该多个无效电源信号可以为低电平的电源信号。示例的,该无效电平的电源正常信号、无效电平的电源感应信号、以及该多个无效电源信号的电压均可以为0v。

[0146]

系统级芯片10在控制电源电路20停止为复位芯片40供电后,该复位芯片40的复位引脚自动拉低,此时该复位芯片40向电源控制芯片30的第二输入端和向光阀控制芯片50的第一输入端z1均输出无效电平的电源正常信号。进而电源控制芯片30可以响应于该待机信号和该无效电平的电源正常信号,向光阀控制芯片50发送无效电平的电源感应信号。之后,电源控制芯片30可以控制电源转换电路60依次向光阀控制芯片50发送多个无效电平的电源信号,以控制光阀控制芯片50下电。

[0147]

综上所述,本公开实施例提供了一种激光投影设备,该激光投影设备中的系统级芯片可以响应于待机操作,控制电源电路停止为复位芯片供电,并向电源控制芯片发送待机信号。进而电源控制芯片可以响应于待机信号和复位芯片下电后输出的无效电平的电源正常信号,向光阀控制芯片发送无效电平的电源感应信号,以及控制电源转换电路依次向光阀控制芯片发送多个无效电平的电源信号,以控制光阀控制芯片下电。由于通过一个电源控制芯片和一个电源转换电路即可控制光阀控制芯片下电,相较于相关技术,简化了用于控制光阀控制芯片下电的电路,提高了激光投影设备内部器件的集成度,且降低了成本。随着激光投影设备往小型化、低成本方向发展,要求光学引擎也必须向小型化方向设计,其内部的板卡配合小型化的光学引擎往尺寸压缩、低成本的方向发展。本公开实施例提供的激光投影设备,通过一个电源控制芯片和一个电源转换电路即可控制光阀控制芯片上电和下这样成本更低、集成化度也高。

[0148]

参考图12和图13,电源控制芯片30用于在接收到待机信号和无效电平的电源正常信号的时长为第五时长t5后,向光阀控制芯片50发送无效电平的电源感应信号,并在接收到待机信号和电源正常信号的时长为第六时长t6后,向电源转换电路60发送无效使能信号。电源转换电路60用于响应于该无效使能信号依次向光阀控制芯片50发送多个无效电源信号。其中,第六时长t6大于第五时长t6,且该第五时长t5和第六时长t6均可以为电源控制

芯片30中预先存储的固定时长。示例的,第五时长t5可以为30ms,第六时长t6可以为40ms。该无效使能信号可以为低电平信号。表2示出了在控制光阀控制芯片50下电的过程中,电源控制芯片30所要接收的信号,以及输出的信号。该第一无效控制信号至第三无效控制信号均可以为低电平信号,多个无效电源信号可以包括第一无效电源信号pwr1至第三无效电源信号pwr3。参考表2、图12和图13,电源控制芯片30在接收到开机信号和电源正常信号后,可以启动定时器,并在定时器的计时时长为第五时长t5后,通过其第四输出端y4向光阀控制芯片50的第四输入端z4发送无效电平的电源感应信号。

[0149]

表2

[0150][0151]

在本公开实施例中,电源控制芯片30用于在接收到待机信号和电源正常信号的时长为第六时长t6后,向第三转换电路63发送无效使能信号en1。该第三转换电路63用于响应于该接收到的无效使能信号en1,向电源控制芯片30的第五输入端x5发送第一无效控制信号pg1,并向光阀控制芯片50发送第一无效电源信号pwr1。可选的,电源控制芯片30在接收到待机信号和无效电平的电源正常信号后,若定时器的计时时长为第六时长,则将定时器清0,并通过其第三输出端y3向第三转换电路63发送无效使能信号en1。

[0152]

电源控制芯片30用于在其第五输入端x5接收到第一无效控制信号pg1的时长为第七时长t7后,向每个第二转换电路62发送一个无效使能信号en2。每个第二转换电路62用于响应于该接收到的无效使能信号en2,向对应的第三输入端z3发送一个第二无效电源信号pwr2,并向对应的第四输入端x4发送第二无效控制信号pg2。其中,该第七时长t7可以为电源控制芯片30中预先存储的固定时长。示例的,该第七时长可以为10ms。

[0153]

可选的,电源控制芯片30在接收到第一无效控制信号pg1后,可以再次启动定时器,并在定时器的计时时长为第七时长t7后,将定时器清0,向对应的第三输入端z3发送一个第二无效电源信号pg2,以及向对应的第四输入端x4发送一个第二无效控制信号pg2。示例的,若电源控制芯片30可以具有2个第四输入端x4,该多个第二转换电路62可以包括第一个第二转换电路62和第二个第二转换电路62。

[0154]

电源控制芯片30的第五输入端x5在接收到第一无效控制信号pg1后可以再次启动定时器,在该定时器的计时时长为第七时长t7后,可以将该定时器清0,并分别向第一个第二转换电路62和第二个第二转换电路62发送无效能信号en2。该第一个第二转换电路62用于响应于接收到的无效能信号en2,向光阀控制芯片50的一个第三输入端z3发送一个第二无效电源信号pwr2,并向电源控制芯片30的一个第四输入端x4发送一个第二无效控制信号pg2。

[0155]

该第二个第二转换电路62用于响应于接收到的无效能信号en2,向光阀控制芯片

50的另一个第三输入端z3发送一个第二无效电源信号pwr2,并向电源控制芯片30的另一个第四输入端x4发送一个第二无效控制信号pg2。

[0156]

电源控制芯片30用于在其第四输入端x4接收到多个第二无效控制信号pg2的时长为第八时长t8后,向第一转换电路61发送无效使能信号en3。该第一转换电路61用于响应于该无效使能信号en3,向电源控制芯片30的第三输入端x3发送第三无效控制信号pg3,并向该光阀控制芯片50的第二输入端z2发送第三无效电源信号pwr3,以控制光阀控制芯片50下电。其中,该第八时长t8可以为电源控制芯片30中预先存储的固定时长。示例的,该第八时长t8可以为10ms。

[0157]

可选的,电源控制芯片30在其第四输入端x4接收到多个第二无效控制信号pg2后,可以再次启动定时器,在定时器的计时时长为第八时长后,通过其第第一输出端y1向第一转换电路61发送无效使能信号en3。上述第一无效控制信号pg1至第三无效控制信号pg3的电压均可以为0v。在本公开实施例中,光阀控制芯片50用于在接收到无效电平的电源正常信号后,可以控制光阀70下电。

[0158]

可选的,光阀70可以为数字微镜器件(digital micromirror device,dmd),该dmd中集成有多个镜片,每个镜片对应投影图像中的一个像素。该dmd中各个镜片的状态不同,从而可以将不同的像素的光线投影至不同位置,由此实现投影图像的显示。参考图14,每个镜片的状态可以包括开启状态和关闭状态,每个镜片在该两个状态下的偏转角度不同。其中,每个镜片在开启状态下将对应像素的光线投影投影屏幕,每个镜片在关闭状态下无需将对应像素的光线投影投影屏幕。光阀控制芯片50通过控制每个镜片处于开启状态或者关闭状态,以实现在投影屏幕上显示投影图像02。

[0159]

光阀控制芯片50在接收到无效电平的电源正常信号之后,先控制光阀70上的多个镜片处于静止状态,即停止控制该多个镜片翻转(此时在投影屏幕上显示的投影图像将保持不变),使得多个镜片保持当前的状态不变。由此避免相邻两个镜片发生碰撞,避免造成相邻两个镜片的镜面的出现机械损伤。其中,参考图14,每个镜片在静止状态下可以为开启状态或者关闭状态。可以理解的是,该在光阀控制芯片50的第五输入端z5接收到无效电平的电源感应信号之前,该光阀控制芯片50的第五输入端z5接收到的信号为有效电平的电源感应信号。

[0160]

光阀控制芯片50在控制多个镜片处于静止状态,且未接收到无效电平的电源感应信号之前,参考图15,光阀控制芯片50可以控制多个镜片均处于初始状态,在该初始状态下,该光阀70不再向投影屏幕投射投影图像。之后光阀控制芯片50再控制光阀断电。可选的,光阀控制芯片50可以向光阀供电芯片80发送无效使能信号,该光阀供电芯片80可以在该无效使能信号的控制下,停止为光阀70供电,由此实现光阀70下电。

[0161]

电源控制芯片30在接收到第一转换电路61发送的第三无效控制信号pg3后,若在指定时长后通过其第六输入端x6接收到光阀控制芯片50输出低电平信号,则可以确定光阀控制芯片50下电成功。其中,该指定时长可以为电源控制芯片30中预先存储的固定时长。

[0162]

电源控制芯片30在确定光阀控制芯片50下电成功后,可以向系统级芯片10发送指示信号,该指示信号用于指示光阀控制芯片50下电成功。该系统级芯片10可以响应于该指示信号,向第一电源开关sw1的控制端输出无效使能信号,以使得第一电源开关sw1的第一端与第二端断开,由此使得电源板21停止为第一转换芯片d1、每个第二转换芯片d2、第三转

换芯片d3、光阀供电芯片80和电源控制芯片30供电。可以理解的是,在电源板21发送的电压为9v时,电源转换器向电源控制芯片提供的电压仍可以为3.3v。

[0163]

参考图16,本公开实施例中光阀控制芯片50的下电过程可以包括以下步骤:

[0164]

步骤1601、系统级芯片响应于待机操作,控制电源电路停止为复位芯片供电,并向电源控制芯片发送待机信号。

[0165]

步骤1602、在复位芯片下电后,电源控制芯片在接收到复位芯片输出的无效电平的电源正常信号和待机信号的时长为第五时长后,向光阀控制芯片发送无效电平的电源感应信号。

[0166]

步骤1603、在复位芯片下电后,电源控制芯片在接收到复位芯片输出的无效电平的电源正常信号和待机信号的时长为第六时长后,向向第三转换电路发送无效使能信号。

[0167]

步骤1604、第三转换电路响应于该接收到的无效使能信号,向电源控制芯片发送第一无效控制信号,并向光阀控制芯片发送第一无效电源信号。

[0168]

步骤1605、电源控制芯片在接收到第一无效控制信号的时长为第七时长后,向每个第二转换电路发送无效使能信号。

[0169]

步骤1606、每个第二转换电路响应于接收到的无效使能信号,向对应的第三输入端发送一个第二无效电源信号,并向对应的第四输入端发送第二无效控制信号。

[0170]

步骤1607、电源控制芯片在接收到多个第二无效控制信号的时长为第八时长后,向第一转换电路发送无效使能信号。

[0171]

步骤1608、第一转换电路用于响应于无效使能信号,向电源控制芯片发送第三无效控制信号,并向该光阀控制芯片发送第三无效电源信号,以控制光阀控制芯片下电。

[0172]

参考图17,图9所示的电路控制光阀控制芯片50的下电过程可以包括以下步骤:

[0173]

步骤1701、系统级芯片响应于待机操作,控制电源电路停止为复位芯片r1供电,并向第一逻辑与器件n1发送待机信号,以使复位芯片r1在下电后向第一逻辑与器件n1输出无效电平的电源正常信号。

[0174]

系统级芯片可以响应于待机操作,向第一逻辑与器件n1的第一输入端发送待机信号,以使复位芯片r1在下电后向第一逻辑与器件n1的第二输入端输出无效电平的电源正常信号。

[0175]

步骤1702、第一逻辑与器件n1向第一逻辑或器件k1、第二逻辑与器件n2和第一逻辑非器件f1输出低电平信号,以使第二逻辑与器件n2向第二时序控制芯片lm2的使能端输出低电平信号,第一逻辑非器件f1向第七逻辑与器件n7输出高电平信号。

[0176]

第一逻辑与器件n1向第一逻辑或器件k1的第一输入端、第二逻辑与器件n2的第一输入端和第一逻辑非器件f1的输入端输出低电平信号。该第二逻辑与器件n2向第二时序控制芯片lm2的使能端输出低电平信号,该第一逻辑非器件f1向第七逻辑与器件n7的第二输入端输出高电平信号。

[0177]

步骤1703、第二时序控制芯片lm2在第七目标时长后向第八逻辑与器件n8输出低电平信号,并在第九目标时长后向第七逻辑与器件n7输出低电平信号。

[0178]

第二时序控制芯片lm2在其使能端接收到低电平信号的时长为第七目标时长后,通过其第三输出端f23向第八逻辑与器件n8的第一输入端输出低电平信号,并在其使能端接收到低电平信号的时长为第八目标时长后,通过其第二输出端f22输出低电平信号。第二

时序控制芯片lm2在其使能端接收到低电平信号的时长为第九目标时长后,向第七逻辑与器件n7的第一输入端输出低电平信号。并且,第二逻辑非器件k2在接收到第一逻辑非器件f1输出的高电平信号后,向第八逻辑与器件n8输出的低电平信号。

[0179]

步骤1704、第七逻辑与器件n7向第二逻辑或器件k2输出低电平信号。

[0180]

第七逻辑与器件n7在接收到第二时序控制芯片lm2输出的低电平信号后,向第二逻辑或器件k2的第一输入端输出低电平信号。

[0181]

步骤1705、第八逻辑与器件n8向第二逻辑或器件k2输出低电平信号。

[0182]

第八逻辑与器件n8在接收到第二时序控制芯片lm2输出的低电平信号,或者,第二逻辑非器件k2输出的低电平信号后,向第二逻辑或器件k2的第二输入端输出低电平信号。

[0183]

步骤1706、第二逻辑或器件k2向第六逻辑与器件n6输出低电平信号。

[0184]

第二逻辑或器件k2在接收到第七逻辑与器件n7和第八逻辑与器件n8输出的低电平信号后,向第六逻辑与器件n6的第二输入端输出低电平信号。

[0185]

步骤1707、第六逻辑与器件n6分别向第一逻辑或器件k1和光阀控制芯片输出无效电平的电源正常信号。

[0186]

第六逻辑与器件n6在接收到低电平信号后分别向第一逻辑或器件k1的第二和光阀控制芯片50输出无效电平的电源正常信号,以使第一逻辑或器件k1向第一时序控制芯片lm1的使能端en输出低电平信号。

[0187]

步骤1708、第一逻辑或器件k1向第一时序控制芯片lm1的使能端en输出低电平信号,以使能第一时序控制芯片lm1向第四逻辑与器件n4输出低电平信号。

[0188]

第一逻辑或器件k1在接收到第六逻辑与器件n6输出的无效电平的电源正常信号,以及第一逻辑与器件n1输出的低电平信号后,向第一时序控制芯片lm1的使能端输出低电平信号en3,以使能第一时序控制芯片lm1通过其第三输出端f13向第四逻辑与器件n4输出低电平信号f1。

[0189]

可以理解的是,第一时序控制芯片lm1向第四逻辑与器件n4输出低电平信号时,该第二时序控制芯片lm2的使能端接收到低电平信号的时长为第十目标时长t10。示例的,第十目标时长可以为40ms。参考图11,第一时序控制芯片lm1的使能端接收到低电平信号en3,至向第四逻辑与器件n4输出低电平信号时长可以为10ms。

[0190]

步骤1709、第四逻辑与器件n4向第三电源转换电路输出第一无效控制信号,以使能第一转换电路向光阀控制芯片输出第一无效电源信号,并向第六逻辑与器件n6输出第一无效控制信号。

[0191]

第四逻辑与器件n4向第三电源转换电路的输入端输出第一无效控制信号,以使能第一转换电路向光阀控制芯片输出第一无效电源信号pwr1,并向第六逻辑与器件n6的第一输入端输出第一无效控制信号pg1。

[0192]

步骤1710、第一时序控制芯片lm1分别向第三逻辑与器件n3和第二逻辑与器件n2输出低电平信号。

[0193]

参考图18,第一时序控制芯片lm1分别向第三逻辑与器件n3的第一输入端输出低电平信号和第二逻辑与器件n2的第二输入端输出低电平信号f2。且第一时序控制芯片lm1分别向第三逻辑与器件n3输出低电平信号f2和第二逻辑与器件n2输出低电平信号f2时,该第二时序控制芯片lm2的使能端en接收到低电平信号的时长为第十一目标时长t11。示例

的,第十一目标时长可以为50ms。

[0194]

参考图11,第一时序控制芯片lm1向第四逻辑与器件n4输出低电平信号时长,至向第三逻辑与器件n3和第二逻辑与器件n2输出低电平信号f2的时长可以为10ms。

[0195]

步骤1711、第三逻辑与器件n3向每个第二转换电路输出一个无效使能信号,以使能每个转换电路向第五逻辑与器件n5输出一个第二无效控制信号,并使能每个转换电路向光阀控制芯片输出一个第二无效电源信号。

[0196]

第三逻辑与器件n3向第一个第二转换电路输出一个无效使能信号,该第一个第二转换电路响应于该无效使能信号,向第五逻辑与器件n5的一个输入端输出一个第二无效控制信号,并向光阀控制芯片输出一个第二无效电源信号。

[0197]

步骤1712、第一时序控制芯片lm1向第一转换电路输出无效使能信号,以使能第一转换电路向光阀控制芯片输出第三无效电源信号。

[0198]

第一时序控制芯片lm1可以向第四逻辑与器件n4的第二输入端输出第三无效控制信号pg3,并向第一转换电路的使能端en输出无效使能信号en4,以使能第一转换电路向光阀控制芯片50输出第三无效电源信号pwr3。且第一时序控制芯片lm1向第一转换电路输出低电平信号时,该第二时序控制芯片lm2的使能端en接收到低电平信号的时长为第十二目标时长t12。示例的,第十二目标时长可以为60ms。参考图11,第一时序控制芯片lm1向第三逻辑与器件n3和第二逻辑与器件n2输出低电平信号f2,至向第一转换电路61的使能端en输出低电平信号en4的时长可以为10ms。

[0199]

参考图7,该激光投影设备还可以包括风扇模组90、开关模组91、温度检测模组92、人眼保护组件93、光源驱动组件94、光源95和第二电源开关sw2。若光源95为三色激光光源,即该光源95能够出射三种不同颜色的激光光束,则该激光投影设备还可以包括与系统级芯片10连接的扩散轮96。其中,该风扇模组90、温度检测模组92、人眼保护组件93和扩散轮96均位于主板100的外围,且未位于显示板200上,该光源驱动组件94位于显示板200上。系统级芯片10分别与开关模组91的控制端、温度检测模组92、人眼保护组件93、扩散轮96和第二电源开关sw2的控制端连接。该电源板21还与第二电源开关sw2的第一端和开关模组91的第一端连接,第二电源开关sw2的第二端与光源驱动组件连接,该开关模组91的第二端与风扇模组90连接。该光源驱动组件94还与光源95连接。

[0200]

参考图19,激光投影设备开机的过程可以包括以下步骤:

[0201]

步骤1901、系统级芯片上电。

[0202]

系统级芯片10可以包括唤醒电路和其他电路,在激光投影设备处于待机状态时,电源板保持为唤醒电路供电的状态不变。即在激光投影设备处于待机状态时,系统级芯片中除唤醒电路处于工作状态之外,系统级芯片中的其他电路均处于不工作状态。因此在待机状态下,该系统级芯片中的唤醒电路可以检测到针对激光投影设备的开机操作,并可以响应于该开机操作,唤醒系统级芯片中的其他电路,并控制电源板为其他电路供电,由此实现系统级芯片上电。

[0203]

步骤1902、系统级芯片上电后为温度检测模组、扩散轮和人眼保护组件供电,并控制风扇模组和光阀控制芯片上电。

[0204]

系统级芯片在上电后响应于开机操作,直接为温度检测模组、扩散轮和人眼保护组件供电,并控制电源电路为风扇模组和复位芯片供电,由此实现控制风扇模组和复位芯

片上电。

[0205]

该系统级芯片10可以响应于开机操作,向开关模组91的控制端输出有效电平的使能信号,以使得该开关模组91的第一端与第二端导通,由此控制电源板21为风扇模组90供电。

[0206]

若风扇模组90包括多个风扇,则该开关模组91包括与该多个风扇对应连接的多个开关电路。该每个开关电路的控制端与系统级芯片10连接,该每个开关电路的第一端与电源板21连接,该每个开关电路的第二端与对应的一个风扇连接。该系统级芯片10可以响应于开机操作,向每个开关电路的有效电平的使能信号,以将该开关电路的第一端和第二端导通,由此使得电源板21为与该开关电路连接的一个风扇供电。

[0207]

可选的,该系统级芯片10还可以向该扩散轮96输出第一控制信号,扩散轮96在第一控制信号的控制下转动。其中,该扩散轮96的转速的大小与该第一控制信号的占空比正相关。其中,该扩散轮96用于对该光源95出射的三种颜色的激光光束进行干涉,以调整三种颜色的激光光束的偏振方向。该第一控制信号可以为脉宽调制(pulse width modulation,pwm)信号。

[0208]

在本公开实施例中,系统级芯片10响应于开机操作,控制光阀控制芯片50上电的过程可以参考上述步骤801至步骤810,本公开实施例在此不再赘述。

[0209]

步骤1903、光阀控制芯片上电后向风扇模组输出第二控制信号。

[0210]

光阀控制芯片50上电后可以向风扇模组90输出第二控制信号,该风扇模组90在该第二控制信号的控制下转动,其中,该风扇模组90的转速的大小与该第二控制信号的占空比正相关。

[0211]

参考图7,该激光投影设备可以包括程序存储组件97,该程序存储组件97与光阀控制芯片50连接。该光阀控制芯片50在上电后,可以从该外接的程序存储组件97中读取程序进行初始化,并在初始化完成后向风扇模组90输出第二控制信号。

[0212]

步骤1904、系统级芯片在确定风扇模组和温度检测模组处于正常工作状态后,指示光阀控制芯片控制光阀上电。

[0213]

系统级芯片10检测风扇模组90和温度检测模组92是否处于正常工作状态。若风扇模组90,和/或,温度检测模组92处于正常工作状态,则系统级芯片10可以向光阀控制芯片50发送供电指令,其中该供电指令用于指示光阀控制芯片50控制光阀70上电。

[0214]

可选的,风扇模组90可以包括至少一个风扇,温度检测模组可以包括至少一个温度传感器。系统级芯片10可以获取风扇模组90中每个风扇的转速,以及温度检测模组92中每个温度检测器检测的温度。系统级芯片10若检测到风扇模组90中每个风扇的转速均处于转速阈值范围内,则可以确定风扇模组90处于正常工作状态。系统级芯片10若检测到风扇模组90中任一风扇的转速未于转速阈值范围内,则可以确定风扇模组90未处于正常工作状态。其中,系统级芯片10中可以预先存储有转速阈值范围。系统级芯片10若检测到温度检测模组92中每个温度检测器检测的温度均处于温度阈值范围内,则可以确定温度检测模组92处于正常工作状态。系统级芯片10若检测到温度检测模组92中任一温度检测器检测的温度未处于温度阈值范围内,则可以确定温度检测模组92未处于正常工作状态。其中,系统级芯片10中可以预先存储有温度阈值范围。

[0215]

可选的,光阀控制芯片50在控制光阀供电芯片80为光阀70供电后,可以向系统级

芯片10发送确认信号,该系统级芯片10在接收该确认信号后,可以确定光阀70上电成功。参考图6,该光阀控制芯片50可以通过i2c(inter integrated circuit)总线向系统级芯片10发送确认信号。

[0216]

系统级芯片10在为人眼保护组件93供电后,还可以基于人眼保护组件93检测的目标物反馈的信号确定是否需要开启人眼保护功能。其中,该目标物反馈的信号可以为目标物辐射的红外信号。

[0217]

步骤1905、系统级芯片在确定光阀上电后控制光源驱动组件上电,以驱动光源出射光束。

[0218]

系统级芯片10在确定光阀70上电成功后,控制电源板21为光源驱动组件94供电,以驱动光源95出射光束。可选的,该系统级芯片10可以响应于开机指令,向第二电源开关sw2的控制端输出有效电平的使能信号,以使得第二电源开关sw2的第一端与第二端导通,由此实现控制电源板21为光源驱动组件94供电。

[0219]

步骤1906、光阀控制芯片向光源驱动组件输出第三控制信号。

[0220]

在本公开实施例中,系统级芯片10在确定光阀70上电成功后,还可以向光阀控制芯片50发送投影图像。并且光阀控制芯片10在接收到投影图像后,可以向光源驱动组件94发送第三控制信号,该光源驱动组件94上电后在该第三控制信号的控制下,驱动光源95出射光束,其中,该第三控制信号可以包括使能信号和电流控制信号,该电流控制信号可以为pwm信号。

[0221]

可选的,系统级芯片10可以通过vx1信号的形式,并以60赫兹(hz)的频率向光阀控制芯片50发送每一帧投影图像,该投影图像的分辨率可以为4k。若光源为三色激光光源,则该第三控制信号可以包括与该投影图像的三种基色一一对应的使能信号,以及与该投影图像的三种基色一一对应的电流控制信号。光源驱动组件94可以基于每种基色的使能信号和电流控制信号,驱动出射该基色光束的光源出射光束。

[0222]

参考图7,激光投影设备还可以包括振镜98,该振镜98与光阀控制芯片50连接。在投影图像的分辨率大于光阀70的分辨率的情况下,该振镜98可以将多帧子图像偏移至投影屏幕的不同位置,以实现该多帧子图像的叠加显示,进而实现投影图像的显示,从而达到扩展光阀的分辨率的效果。

[0223]

光阀控制芯片50在接收到系统级芯片10发送的投影图像之后,若该投影图像的分辨率大于光阀的分辨率,则可以将该投影图像划分为多帧子图像。对于每帧子图像,该光阀控制芯片50可以控制光源驱动组件94驱动光源95出射光束,并在光源95出射的光束照射至光阀70的过程中,根据该帧子图像控制光阀70对照射至其表面的照明光束进行调制,并控制光阀70将调制得到的影像光束传输至振镜98。该振镜98用于将光阀传输的影像光束传输至投影镜头。该投影镜头用于将该振镜传输的影像光束投射至投影屏幕,由此实现将多帧子图像依次投影显示至投影屏幕上,进而实现通过低分辨率的光阀投影显示高分辨率的投影图像。

[0224]

在投影显示每帧子图像的过程中,光阀控制芯片50可以将对应一帧子图像的振镜驱动电流控制传输至振镜98,以驱动该振镜98偏振。其中,该不同帧子图像对应的振镜驱动电流方向不同,由此可以实现将多帧子图像投影至投影屏幕的不同位置,进而实现该多帧子图像的叠加显示。并且,在投影显示多帧子图像的过程中,该振镜驱动电流的电流方向可

以交替变化,且该振镜驱动电流的变化波形可以为正弦波。

[0225]

参考图7,该激光投影设备可以包括数字模拟转换器(digital to analog converter,dac)d,该数字模拟转换器d分别与光阀控制芯片50和振镜98连接,该数字模拟转换器d用于将光阀控制芯片50传输的振镜驱动电流由数字信号转换成模拟信号,并将转换后的模拟信号传输至振镜98。光阀控制芯片50还可以基于检测的振镜98的温度,通过i2c总线向振镜控制指令,该控制指令可以用于调整振镜的角度等。

[0226]

参考图7,系统级芯片10还可以通过通用串行总线(universal serial bus,usb)总线向光阀控制芯片50发送校正数据。该激光投影设备可以包括存储器r,该存储器r可以为带电可擦可编程只读存储器(electrically erasable programmable read only memory,eeprom),光阀控制芯片50可以通过i2c总线向该存储器r发送该校正数据,以使得该存储器r存储校正数据。该校正数据可以用于校正投影图像的投影位置或者投影形状。光阀控制芯片50可以基于该校正数据校正投影图像的投影位置或者投影形状。

[0227]

在本公开实施例中,参考图20,激光投影设备的待机过程可以包括以下步骤:

[0228]

步骤2001、系统级芯片响应于待机操作,控制光阀控制芯片和光阀下电。

[0229]

控制光阀控制芯片下电的过程可以参考上述步骤1601至步骤1608,控制光阀下电的过程也可以参考前述内容,本公开实施例在此不再赘述。

[0230]

步骤2002、系统级芯片控制光源驱动组件下电,以关闭光源。

[0231]

参考图7,该系统级芯片10可以响应于待机操作,向第二电源开关sw2的控制端输出无效电平的使能信号,以使得第二电源开关sw2的第一端与第二端断开,由此实现控制电源板21停止为光源驱动组件94供电,以使得光源95停止出射光束,即关闭光源95。

[0232]

步骤2003、系统级芯片在确定光阀下电成功后控制风扇、温度检测模组、人眼保护组件和扩散轮下电。

[0233]

参考图7,系统级芯片10在确定光阀下电成功后,可以向开关模组91的控制端输出无效电平的使能信号,以使得该开关模组91的第一端与第二端断开,由此实现控制电源板21停止为风扇模组90供电。

[0234]

若风扇模组90包括多个风扇,则该系统级芯片10在确定光阀下电成功后,可以向每个开关电路发送无效电平的使能信号,以将该开关电路的第一端和第二端断开,由此使得电源板21停止为与该开关电路连接的一个风扇供电。

[0235]

步骤2004、系统级芯片进入待机状态。

[0236]

系统级芯片中的唤醒电路可以控制电源板停止为其他电路供电,由此使得系统级芯片进入待机状态。在本公开实施例中,有效使能信号的电压可以为3.3v,无效使能信号的电压可以为0v。

[0237]

在本公开实施例中,术语“第一”、“第二”、“第三”、“第四”、“第五”、“第六”、“第七”、“第八”、“第九”、“第十”、“第十一”、“第十二”、“第十三”、“第十四”、“第十五”、“第十六”、“第十七”、“第十八”、“第十九”、“第二十”、“第二十一”以及“第二十二”仅用于描述目的,而不能理解为指示或暗示相对重要性。本公开实施例中术语“多个”的含义是指两个或两个以上。

[0238]

以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。