mipi rffe地址分配方法和mipi rffe设备

技术领域

1.本技术涉及针对mipi rffe地址分配的方法和对应的mipi rffe设备。

背景技术:

2.mipi(移动工业处理器接口联盟)射频前端控制接口mipi rffe,是广泛用于射频前端系统控制的标准化接口并且例如用于移动电话中。mipi rffe系统可以包括与总线实例耦合的多达15个从设备和多达4个主设备,包括功率放大器、低噪声放大器、滤波器和开关。与总线实例耦合的组件各自需要唯一的地址,被称为usid,用于经由总线实例进行通信。

3.usid可以由某个射频设备的制造商设置。但是,如果要为单个总线实例部署的两个设备配置了相同的usid,例如,当具有相同usid的两个相同类型的不同设备被使用时,或者如果两个不同的设备碰巧具有相同的usid,这可能会导致问题。

4.解决该问题的一个方法是使用多个地址引脚来设置地址,单独熔断芯片来设置特定地址或者制造具有不同地址的相同设备。所有这些方法都增加了设备成本,这是不期望的。

技术实现要素:

5.提供了如权利要求1所限定的设备和如权利要求14所限定的方法。从属权利要求限定了进一步的实施例。

6.根据一个实施例,提供了用于mipi rffe设备的地址分配的方法,方法包括:

7.利用基于mipi rffe设备所接收的mipi信号的时序,检测mipi rffe设备的配置端子处的电压,以及

8.基于所检测的电压,设置mipi rffe设备的地址。

9.根据另一实施例,提供了包括感测电路装置的mipi rffe设备,感测电路装置被配置为:

10.利用基于mipi rffe设备所接收的mipi rffe信号的时序,确定mipi设备的配置端子处的电压,

11.基于所检测的电压,设置mipi rffe设备的地址。

12.以上发明内容仅是对一些实施例的简要概述并且不应被解释为限制。

附图说明

13.图1是根据一个实施例的设备的框图。

14.图2是图示了根据一些实施例的方法的流程图。

15.图3是图示了示例mipi rffe信号的格式的示意图。

16.图4是图示了mipi rffe系统在启动时的信号的图。

17.图5至图7是图示了根据各种实施例的感测时序的图。

18.图8是根据一个实施例的mipi rffe设备的电路图。

具体实施方式

19.在下文中,将参考附图来详细描述各种实施例。这些实施例仅作为示例给出并且不应被解释为限制。例如,虽然实施例可以被描述为包括多个特征(例如,组件、元素、动作、事件、步骤等),但在其他实施例中,这些特征中的一些可以被省略和/或可以被备选特征替换。除了明确示出和描述的特征之外,还可以提供另外的特征。例如,本文讨论的实施例涉及针对mipi rffe设备的地址分配。除了所描述的地址分配之外,mipi rffe设备可以以常规方式实现,例如用于在地址分配之后进行通信并用于执行通常使用mipi设备执行的各种功能,例如在mipi rffe设备的情况下的功率放大器、低噪声放大器、天线调谐器、滤波器、开关或任何其他射频设备。

20.来自不同实施例的特征可以被组合来形成另外的实施例。除非另有说明,否则关于实施例中的一个所描述的变化或修改也可以被应用于其他实施例。

21.除非另有说明,否则本文所述的连接或耦合涉及电连接或耦合。只要连接或耦合的一般功能(例如,提供某种信息、传输电压和/或电流等)基本上保持不变,这样的连接或耦合可以例如通过添加组件或通过移除组件被修改。

22.图1是示出根据一个实施例的mipi设备10的框图。mipi设备10的组件可以被集成在单个芯片上,或者可以例如被提供在同一封装件中包括的不同芯片中。

23.mipi设备10包括被配置为接收供电电压vio的第一端子13a、被配置为接收vss(或接地)的第五端子13e(vio是相对于vss的供电电压)、被配置为接收mipi rffe时钟信号sclk的第二端子13b以及被配置为接收mipi rffe数据信号sdata的第三端子13c。信号sdata、sclk是本文中使用的mipi rffe信号的示例。

24.供电电压vio为设备10的组件供电。时钟信号sclk和数据信号sdata用于与设备10的mipi核11进行mipi数据通信。mipi核11可以经由端子13c接收和发射数据信号,例如接收由时钟信号sclk计时的命令并执行使用设备10的任何功能,例如如上所述的功能,诸如放大器功能、调谐功能、切换功能等。这可以以任何常规方式实现。虽然mipi核11被耦合到三个端子13a-13c,但是根据功能,可以在设备10中提供更多端子,例如与用于调谐的天线待耦合的端子、与mipi核11的内部开关耦合的端子、用于接收信号和输出放大信号的端子等。

25.此外,设备10包括第四端子13d,第四端子13d被用于在mipi rffe设备10启动时进行地址配置。电压vsense在实施例中被施加到第四端子13d并且由感测电路装置12检测来确定待使用的设备10地址(usid)。在实施例中,如以下更详细解释的,vsense可以采取多于两个的不同级别,例如四个不同级别,以允许经由单个端子(即,第四端子13d)设置四个不同的地址。

26.与端子13d有关的外部寄生电容cpar和内部寄生电容cpad可能会影响vsense在感测电路装置12处达到足够稳定的状态以允许可靠感测的程度。直到vsense足够稳定的时间也可能与供电电压vio在启动时上升的速度相关。另一方面,在启动时,根据mipi rffe标准,在供电电压vio已经达到启动时的预定义阈值之后120ns,设备10应能够接收mipi rffe信号,使得需要快速设置设备10的地址。如下所述的实施例允许在设备启动时可靠地检测和测量vsense。

27.在实施例中,用于检测电压vsense的时序基于mipi rffe信号,例如在启动之后在端子13c处所接收的第一mipi rffe信号和/或在端子sclk处所接收的时钟信号sclk。对于该时序,mipi核11可以将关于mipi rffe信号(在端子13b和/或13c处)的信息提供给感测电路装置12,使得感测电路装置12可以基于其感测时序。

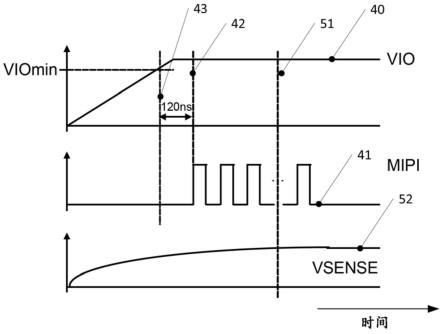

28.例如,用于检测vsense的感测时段的开始、用于检测vsense的感测时段的结束中一者或两者均可以基于mipi rffe信号。“感测时段的开始”可以指代感测电路装置12的内部节点被充电到用于检测vsense的阈值电压,而内部感测noe被充电到vsense的时间点。例如在内部感测节点处的电压与阈值电压进行比较,然后基于该比较来确定待设置的地址的情况下,感测时段的结束可以指代发生实际检测的时间点。以下将进一步讨论根据实施例的基于由mipi rffe设备10或其他设备所接收的mipi rffe信号的这种时序的各种示例。

29.图2是根据一个实施例的用于向mipi rffe设备的地址分配的方法的流程图,方法可以例如在图10的设备中实现,但也可以独立于图10的设备来实现。为了避免重复,将参考以上对图1的描述来描述图2的方法。

30.在20处,方法包括利用基于所接收的mipi rffe信号的感测时序,检测配置端子处的电压,如图1中的端子13d处的vsense。

31.在21处,方法包括基于所检测的电压,例如基于vsense的电压电平,针对与图1的设备10类似的mipi rffe设备设置地址。例如,在21处,基于所检测的vsense,可以从多于两个地址(例如,四个地址)的组中选择地址。

32.接下来,将参考图3至图7来描述根据各种实施例的基于mipi rffe信号的感测时序来检测vsense。图3是可以由例如设备10在第三端子13c上接收的示例mipi rffe信号。图3中的每个框可以表示一位数据。第一位被标记为ssc,可以在总线的数据线上发送并且在13c处接收,并且指示命令将作为sdata与时钟信号sclk被一起发送。之后,暂停之后是地址位sa《3》至sa《0》、代码位、七个数据位和奇偶校验位。

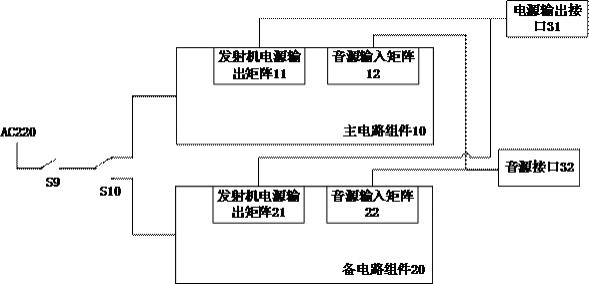

33.图4图示了mipi rffe设备在启动时的信号。曲线40图示了供电电压vio。在启动时,电压vio上升,直到由线43表示的时间点达到预定义最小阈值viomin。在至少120ns之后的时间点处,如垂直线42所示,根据曲线41的mipi rffe信号可以开始,其中曲线41图示了mipi rffe时钟信号sclk交替0和1值,其可以与图3所示的数据信号被同时发送。换言之,在由线42表示的时间点处,mipi rffe数据信号的第一位(如图3所示)ssc可能出现。

34.现在将参考图5至图7来解释根据不同实施例的基于如曲线41所示的包括sclk的mipi rffe信号的感测时序。如图5至图7所示的元素(已参考图4解释的)具有相同的附图标记并且将不再描述。除了图4的曲线40和41之外,图5至图7中的每一个将如图1的第四端子13d的配置端子处的电压vsense图示为曲线52。可以看出,在启动时,vsense上升并且随着时间呈现基本固定的值,这与外部施加到端子13d的电压相关。稍后将参考图8解释这样的电压的示例。电压vsense达到基本稳定电平所花费的时间除其他外取决于被耦合到端子的电容(例如图1的cpar和cpad),并且实现方式还可能与其他因素(例如供电电压vio上升的速度)相关。

35.图5图示了在实施例中可用的第一感测时序。在图5中,用于检测电压vsense的感测时段开始于mipi rffe信号的开始,例如图3的ssc位,在图5的示例中对应于由线42标记的时间。感测时段在mipi rffe时钟信号sclk的预定义时钟处结束。换言之,感测时段在

mipi rffe时钟信号的第n时钟处结束。n可以基于实现方式来选择。例如,在一些mipi rffe实现方式中,待分配地址的设备(例如设备10)必须在第一mipi rffe信号之后分配其地址,使得如果它被命令寻址(例如,如果位sa《3》至sa《0》寻址相应设备),它可以执行命令发送。在一些实现方式中,最短的mipi rffe信号可以包括12个时钟信号时段。在这种情况下,n被选择为小于12,例如n=8,这样可以保证在需要地址时完成地址分配。在图5中,这由垂直线51表示,即,感测时段从与mipi rffe信号开始相对应的线42表示的时间开始,并且在垂直线51表示的第n时钟处结束。可以看出,在由垂直线51指示的时间处,根据曲线42的vsense已大致达到其稳定值,这允许可靠的感测。

36.因此,在图5的实施例中,感测时段以mipi rffe信号的特征(在该情况下,是mipi rffe数据信号的第一位ssc或第一时钟)开始,并以mipi rffe数据信号的特征结束(在该情况下,mipi rffe时钟信号的第n时钟)。代替以ssc位开始,在其他实施例中,感测时段也可以以不同的特征(例如mipi rffe时钟信号的第二时钟)开始。

37.可用于实施例的第二感测时序在图6中示出。如图5中,感测时段在mipi rffe信号的开始处开始,对应于垂直线42。在开始之后,如垂直线60所示,感测在由箭头61指示的预定义延迟之后停止。同样在该情况下,vio几乎稳定并且vsense几乎达到其稳定值。在以上示例中,由箭头61指示的预定义延迟被选择为小于12个时钟周期,使得在该情况下,地址也在mipi rffe命令结束之前被分配。

38.在图6中,感测时段以mipi rffe信号的特征(在图6的示例中为开始)开始,并且在该特征之后的预定义时间结束。同样在此处,代替ssc位,可以使用另一特征,例如第二时钟。

39.在一些实施例中可用的第三感测时序如图7所示。此处,如垂直线70所示,感测时段的开始可以是vio上升期间的某个时间,例如当vio达到某个阈值时。在一些实施例中,开始可能与vio到达vio

min

(即,垂直线43)重合。换言之,在该情况下,感测的开始与mipi rffe信号不相关。如图5的情况并且在图7中也利用如图5所示的垂直线51标记,然后在mipi rffe信号的第n时钟处感测结束。感测时段的结束确保vsense已接近稳定值。

40.在图7中,感测时间根据斜率开始,但是结束于mipi rffe信号的特征,在该示例中为第n时钟。

41.在实现方式中,以上讨论的基于图5至图7中的mipi rffe信号的感测时序确保了待针对地址分配而感测的电压vsense基本稳定,并且vio也已达到基本上稳定的值。在实现方式中,与在vio上升期间的某个点开始感测(类似于图7中的线70)然后在此之后的预定义延迟结束的方法相比,这允许更可靠的感测,因为然后感测的开始和结束两者与vio的斜率相关,并且与电压vio上升的速度相关,vsense和vio的稳定值在感测期间可能无法达到,这可能导致感测不准确。

42.图8是图示了根据一个实施例的用于地址分配的感测电路装置和不同电压vsense的应用的电路图。感测电路装置可以例如被用作图1的感测电路装置12。

43.图8中的线82将用于施加电压vsense的片外电路83和包括感测电路装置的片上电路84分开,感测电路装置可以被包括在于图1的设备10类似的设备中。

44.图8的实施例支持四个不同地址的设置。为了实现这一点,可以与图1的第四端子13d相对应的配置节点811可以被直接耦合到供电电压vio来设置第一地址,可以经由电阻

器re被连接到vio来设置第二地址,可以被浮置(float)来设置第三地址或者可以被耦合到接地vss来设置第四地址。在其他实施例中,配置节点811的多于四个或少于四个的不同耦合可以被用于生成待被感测的电压vsense。在又一实施例中,用于设置地址的电压可以从独立于vio和vss的电压源被直接施加到配置节点811。

45.图8的片上部分包括esd保护电路81,保护芯片免受配置节点811处的静电放电(esd)事件的影响。可以使用任何常规的esd保护电路装置,例如二极管或其他电路元件,当它们在配置节点811处的电压时导通,从而将电压分流到接地vss或正供电电压vio(与电压的符号相关)。这样的高电压例如可能是由于esd事件。

46.例如由于esd保护电路中使用的二极管或其他元件的电容,esd保护电路81也可能对电容cpad有贡献。

47.除了可能提供寄生电容之外,esd保护电路81基本上不影响所示设备在正常操作中的行为,即,在esd或其他高压元件外部。

48.在图8的设备中,在导通时,一旦vio足够高(例如,一旦vio达到图4所示的值vio

min

),晶体管85a、85b就被导通,以在相应源极端子和漏极端子(在场效应晶体管的情况下)或集电极和发射极端子(在双极晶体管或绝缘栅双极晶体管的情况下)之间导通。这将内部感测节点85经由电阻器86a连接到vio并且经由电阻器86b连接到vss。这样,内部感测节点87利用电压vsense充电。在其他实施例中,待被感测的电压可以被直接施加到内部感测节点87。电阻器86a、86b被选择为允许足够快的充电,使得vsense在感测时段结束时基本稳定在内部感测节点87处。值与所允许或预期的寄生电容cpar相关。cpar越高,通过电阻器86a、86b的电流就需要越大,因此必须选择电阻器86a、86b的较小值。示例值是小于5pf的cpar和小于10μa的电流,但这与实现方式相关。

49.此时,晶体管88a、88b仍然被关断。

50.随着感测时段的开始(例如,如图5和图6中的线42所示的ssd位或图7中的线70所示的斜率中的时间点),晶体管88a、88b被导通。这通过由电阻器89a、89b、89c和89d形成的电阻分压器生成阈值电压vthu、vthm和vthl。这些阈值电压被选择为使得它们如上所述在配置节点811处的四个不同的可能输入电压之间(vio、vss、浮置或经由电阻器re的vio)。在从ssd位开始的感测时段的情况下,ssd位可以触发计数器813,计数器然后输出信号th_en,使得晶体管88a、88b导通。在图7的情况下,代替信号ssd,计数器可以由超过预定义阈值的vio启动。

51.内部感测节点87处的电压被提供给比较器810a、810b和810c的第一输入。比较器810a、810b和810c的第二输入被分别提供有阈值电压vthu、vthm和vthl。在感测时段结束时(例如在图5和图7的情况下在第n时钟信号处或在预定义的延迟61之后),比较器810a、810b、810c被启用来执行内部感测节点87处的电压和相应阈值电压vthu、vthm和vthl的比较并且将结果输出到解码/锁存电路812。在使用第n时钟的情况下,计数器810基于sckl从ssd(或超过阈值的vio)开始计数并且在达到第n时钟之后,将比较器使能信号输出到comp_en来使能比较器810a、810b、810c。在如图6所示的模拟延迟的情况下,可以使用由ssd触发的模拟延迟电路或mipi rffe信号的另一特征来代替计数器。

52.解码/锁存电路812接收来自比较器810a、810b和810c的输出并且输出id值,在这种情况下为2位值,指示待被使用的四个地址中的一个地址。当内部感测节点87处的电压超

过vthu时,id的第一值被输出,如果电压在vthu和vthm之间(例如对应于经由re施加的vio),则id的第二值被输出,当内部感测节点87处的电压在vthm和vthl之间(例如配置节点811被浮置)时,id的第三值被输出,并且当电压低于vthl(例如对应于与vss耦合的配置节点811)时,id的第四值被输出。在实施例中,该值被锁存,即,无论配置节点811处的任何改变如何,它都保持输出。基于信号id,则在这种情况下,四个预定义地址中的一个被用于图1的mipi rffe设备10。在该地址确定过程之后,感测电路装置被关断,例如晶体管85a、85b、88a和88b以及比较器810a、810b、810c被关断。因此,在实施例中,在设置地址之后,除了可能的小泄漏电流之外,感测电路装置不会对设备的电流消耗做出贡献。

53.图8中具有三个并行比较器的配置仅是示例配置,并且可以使用能够在内部感测节点87处感测vsense的任何配置,例如交错比较器配置、多级比较器等。因此,图8所示的具体电路不应被解释为以任何方式进行限制。

54.一些实施例由以下示例限定:

55.示例1.一种用于mipi rffe设备的地址分配的方法,包括:

56.利用基于所述mipi rffe设备所接收的mipi rffe信号的时序,检测所述mipi rffe设备的配置端子处的电压,以及

57.基于所检测的电压,设置所述mipi rffe设备的所述地址。

58.示例2.根据示例1所述的方法,其中利用基于所述mipi rffe信号的时序检测所述电压包括开始用于基于所述mipi rffe信号的特征检测所述电压的感测时段。

59.示例3.根据示例2所述的方法,其中所述特征是所述mipi rffe信号的ssc位。

60.示例4.根据示例2或3所述的方法,其中所述感测时段基于所述mipi rffe信号的另一特征而结束。

61.示例5.根据示例4所述的方法,其中所述另一特征是mipi rffe时钟信号的第n时钟。

62.示例6.根据示例5所述的方法,其中n小于mipi rffe信号的最小长度。

63.示例7.根据示例3或4所述的方法,其中所述感测时段在所述特征之后的预定义时间结束。

64.示例8.根据示例1或2所述的方法,其中利用基于所述mipi rffe信号的时序检测所述电压包括在感测时段中检测所述电压,其中所述感测时段在所述mipi rffe信号的特征处结束。

65.示例9.根据示例8所述的方法,其中所述特征是所述mipi rffe信号的第n时钟周期。

66.示例10.根据示例9所述的方法,其中n小于mipi rffe信号的最小长度。

67.示例11.根据示例8至10中任一项所述的方法,其中所述感测时段的开始基于在所述mipi rffe设备启动时供电电压上升。

68.示例12.根据示例2至11中任一项所述的方法,其中所述方法包括在所述感测时段开始时,激活比较器阈值,并且启用被配置为在所述感测时段结束时将所述电压与所述比较器阈值进行比较的比较器布置,其中基于所检测的电压设置所述地址包括基于所述比较器布置的一个或多个输出来设置所述地址。

69.示例13.根据示例1至12中任一项所述的方法,其中所述mipi rffe信号是在所述

mipi rffe设备启动之后的第一mipi rffe信号。

70.示例14.一种包括感测电路装置的mipi rffe设备,所述感测电路装置被配置为:

71.利用基于所述mipi rffe设备所接收的mipi rffe信号的时序,检测所述mipi rffe设备的配置端子处的电压,以及

72.基于所检测的电压,设置所述mipi rffe设备的所述地址。

73.示例15.根据示例14所述的设备,其中所述设备被配置为执行根据示例1至13中任一项所述的方法。

74.示例16.根据示例14或15所述的设备,其中所述感测电路装置被配置为针对利用基于所述mipi rffe信号的时序来检测所述电压,开始用于基于所述mipi rffe的特征来检测所述电压的感测时段。

75.示例17.根据示例16所述的设备,其中所述特征是所述mipi rffe信号的ssc位。

76.示例18.根据示例16或17所述的设备,其中所述感测电路装置被配置为基于所述mipi rffe信号的另一特征来结束所述感测时段。

77.示例19.根据示例18所述的设备,其中所述另一特征是mipi rffe时钟信号的第n时钟。

78.示例20.根据示例19所述的设备,其中n小于mipi rffe信号的最小长度。

79.示例21.根据示例16或17所述的设备,其中所述感测电路装置被配置为在所述特征之后的预定义时间结束所述感测时段。

80.示例22.根据示例14至16中的任一项所述的设备,其中所述感测电路装置被配置为针对利用基于所述mipi rffe信号的时序检测所述电压,在感测时段中检测所述电压,其中所述感测时段在所述mipi rffe信号的特征处结束。

81.示例23.根据示例22所述的设备,其中所述特征是所述mipi rffe信号的第n时钟周期。

82.示例24.根据示例23所述的设备,其中n小于mipi rffe信号的最小长度。

83.示例25.根据示例22至24中任一项所述的设备,其中所述感测电路装置被配置为基于在所述mipi rffe设备启动时供电电压上升来开始所述感测时段。

84.示例26.根据示例16至25中任一项所述的设备,其中所述感测电路装置包括比较器布置,所述比较器布置被配置为将所述电压与多个比较器阈值进行比较,其中所述感测电路装置被配置为在所述感测时段开始时激活所述比较器阈值,并且在所述感测时段结束时启用所述比较器布置,并且基于所述比较器布置的一个或多个输出来设置所述地址。

85.示例27.根据示例14至26中任一项所述的设备,其中所述mipi rffe信号是在所述mipi rffe设备启动之后的第一mipi rffe信号。

86.尽管本文中已图示和描述了特定实施例,但是本领域普通技术人员将理解,在不脱离本发明范围的情况下,可以利用各种备选和/或等效实现方式来代替所示和描述的特定实施例。本技术旨在涵盖本文讨论的特定实施例的任何修改或变化。因此,本发明旨在仅由权利要求及其等同物来限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。