蒙哥马利乘法器的快速预计算

相关申请的交叉引用

1.本技术涉及同一日期提交的名称为“efficient montgomery multiplier”、代理人案卷号为1058-2082的美国专利申请,其公开内容通过引用而并入于此。

技术领域

2.本技术总体上涉及蒙哥马利算法,尤其涉及蒙哥马利预计算值的计算以及蒙哥马利乘法器和相关电路的实现。

背景技术:

3.在密码学中,广泛地使用诸如大整数的模乘和取幂等的运算。已经提出了用于快速实现这类乘法和取幂的若干方法。广泛使用的一种这类方法由peter lawrence montgomery在1985年提出,并且例如由kork等人在“analyzing and comparing montgomery multiplication algorithms”(ieee micro第16卷第3期,1996年6月,第26-33页)中描述,其中作者讨论了若干蒙哥马利乘法算法并且详细分析了所述方法的空间和时间要求。

4.在“modified montgomery modular multiplication and rsa exponentiation techniques”(iee proceedings on computation digital techniques第151卷第6期,2004年11月),mclvor等人提出了改进的蒙哥马利乘法以及使用进位保留加法器(csa)来进行大字长加法的相关rivest-shamir-adleman(rsa)取幂算法和电路架构。所提出的方法基于在rsa取幂的上下文内对模乘的解的重新制定,并且提出了两种算法变体,一种基于5-2csa,另一种基于4-2csa加复用器。

技术实现要素:

5.这里描述的本发明的实施方式提供了用于将两个被乘数相乘再按预定义数取模的蒙哥马利乘法设备(mma)。mma包括预计算电路和蒙哥马利乘法电路。预计算电路被配置为通过进行一系列迭代来计算蒙哥马利预计算值。在给定迭代中,预计算电路被配置为通过对先前迭代中所计算出的中间值进行逐位运算来修改一个或多个中间值。蒙哥马利乘法电路被配置为通过使用预计算电路所计算出的蒙哥马利预计算值进行多个蒙哥马利归约运算来将两个被乘数相乘,再按预定义数取模。

6.在一些实施方式中,蒙哥马利预计算值是至少二至蒙哥马利被乘数的位数的两倍的幂。

7.在一些实施方式中,预计算电路被配置为在给定迭代中通过对(i)先前迭代中所计算出的逐位和、(ii)先前迭代中所计算出的逐位进位的两倍、以及(iii)模校正数进行逐位和与逐位进位运算来修改逐位和与逐位进位。在示例实施方式中,预计算电路被配置为基于一系列迭代中的最后迭代之后的逐位和与逐位进位的两倍之和来计算蒙哥马利预计算值。在另一实施方式中,预计算电路被配置为基于最后迭代中所计算出的逐位和与逐位

进位的两倍之和来计算模校正数。

8.在又一实施方式中,预计算电路被配置为基于先前迭代中所计算出的逐位和与逐位进位之和与预定义数之间的差来计算给定迭代中的模校正数。在另一实施方式中,预计算电路被配置为基于先前迭代中所计算出的逐位进位和逐位和之和的最高有效位的子集、以及预定义数的最高有效位的子集来计算给定迭代中的模校正数。

9.在所公开的实施方式中,预计算电路被配置为基于先前迭代中所计算出的逐位进位和逐位和之和的位的子集、以及预定义数的位的子集来计算给定迭代中的模校正数。在实施方式中,预计算电路被配置为将模校正数设置为预定义数乘以-1、-2或0。在实施方式中,预计算电路包括进位保留加法器(csa),该进位保留加法器被配置为在给定迭代中计算(i)先前迭代中所计算出的逐位和的两倍、(ii)先前迭代中所计算出的逐位进位的两倍、以及(iii)被设置为预定义数乘以-1、-2或0的模校正数的逐位和与逐位进位。

10.在一些实施方式中,预计算电路包括三输入进位保留加法器(csa),该三输入进位保留加法器被配置为在给定迭代中计算(i)先前迭代中所计算出的逐位和的两倍、(ii)先前迭代中所计算出的逐位进位的两倍、以及(iii)被设置为预定义数乘以-1、-2或0的模校正数的逐位和与逐位进位。在其它实施方式中,预计算电路包括四输入进位保留加法器(csa),该四输入进位保留加法器被配置为在给定迭代中计算(i)先前迭代中所计算出的逐位和的两倍、(ii)先前迭代中所计算出的逐位进位的两倍、(iii)被设置为预定义数乘以-1或0的第一模校正数、以及(iv)被设置为预定义数乘以-2或0的第二模校正数的逐位和与逐位进位。

11.在一些实施方式中,预计算电路和蒙哥马利乘法电路被包括在网络装置中,并且被配置为进行网络装置的加密操作。

12.根据本发明的实施方式,另外提供了用于将两个被乘数相乘再按预定义数取模的方法。该方法包括使用预计算电路、通过进行一系列迭代来计算蒙哥马利预计算值,该一系列迭代包括在给定迭代中通过对先前迭代中所计算出的中间值进行逐位运算来修改一个或多个中间值。使用蒙哥马利乘法电路,通过使用预计算电路所计算出的蒙哥马利预计算值进行多个蒙哥马利归约运算来将两个被乘数相乘,再按预定义数取模。

13.根据本发明的实施方式,还提供了用于将两个被乘数相乘再按预定义数取模的集成蒙哥马利计算引擎(imce)。imce包括进位保留加法器(csa)电路和控制电路。csa电路具有多个输入,并且具有包括和输出和进位输出的输出。控制电路耦合至csa电路的输入和输出,并且被配置为在至少(i)计算蒙哥马利预计算值的第一设置和(ii)计算两个被乘数的蒙哥马利乘法的第二设置中操作csa电路。

14.在一些实施方式中,控制电路被配置为对csa电路的和输出和进位输出进行逻辑移位、并且将移位后的和输出和移位后的进位输出耦合到csa电路的相应输入。在示例实施方式中,控制电路被配置为在第一设置中对csa电路的和输出和进位输出进行逻辑左移位、并且在第二设置中对csa电路的和输出和进位输出进行逻辑右移位。

15.在实施方式中,在第一设置中,控制电路被配置为将csa电路的输入中的两个设置为取决于预定义数的恒定值。在另一实施方式中,在第一设置中,控制电路被配置为根据csa电路的和输出和进位输出的最高有效位以及两个被乘数来将csa电路的输入设置为预定义数或零。在又一实施方式中,在第二设置中,控制电路被配置为根据被乘数中的一个被

乘数来将csa电路的输入设置为零或被乘数中的另一被乘数。在所公开的实施方式中,在第二设置中,控制电路被配置为根据和输出、进位输出的最低有效位以及两个被乘数来将csa电路的输入设置为零或预定义数。

16.在一些实施方式中,控制电路被配置为进一步在第三设置中操作csa电路,该第三设置计算预定义指数对预定义底数的取幂、再按预定义数取模。在实施方式中,控制电路被配置为通过按照根据指数定义的序列应用第一设置和第二设置来在第三设置中操作csa电路。

17.在一些实施方式中,csa和控制电路被包括在网络装置中,并且被配置为进行网络装置的加密操作。

18.根据本发明的实施方式,还提供了用于将两个被乘数相乘再按预定义数取模的方法。该方法包括操作进位保留加法器(csa)电路,该csa电路具有多个输入并且具有包括和输出和进位输出的输出。使用耦合至csa电路的输入和输出的控制电路,csa电路被控制为在至少(i)计算蒙哥马利预计算值的第一设置和(ii)计算两个被乘数的蒙哥马利乘法的第二设置中操作。

19.根据以下结合附图对实施方式的详细描述,将更充分地理解本发明,其中在附图中:

附图说明

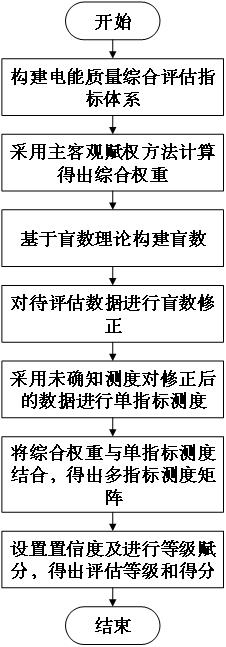

20.图1是示意性地图示根据本发明的实施方式的蒙哥马利乘法设备(mma)的框图;

21.图2是示意性地图示根据本发明的实施方式的图1的mma中的蒙哥马利预计算电路(mpc)的框图;

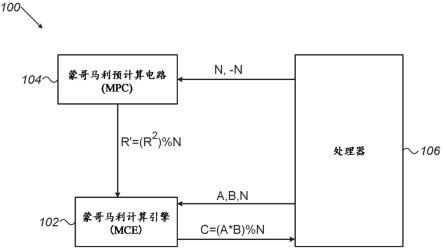

22.图3是示意性地图示根据本发明的实施方式的用于蒙哥马利预计算的方法的流程图;

23.图4是示意性地图示根据本发明的实施方式的具有集成在蒙哥马利计算引擎中的预计算电路的mma的框图;

24.图5是示意性地图示根据本发明的实施方式的集成蒙哥马利计算引擎(imce)的框图;

25.图6是示意性地图示根据本发明的实施方式的用于蒙哥马利4096位

×

4096位乘法的方法的流程图;以及

26.图7是示意性地图示根据本发明的实施方式的用于取幂的方法的流程图。

具体实施方式

概述

27.公钥密码系统可以用于提供数据机密性、作者认证和数据完整性。一些公钥密码系统(例如,rivest

–

shamir

–

adleman(rsa))依赖于大数的取幂,这需要重复的模乘。为了提高安全性,操作数在长度上的大小通常远超过1000位,这增加了取幂运算的计算负荷。

28.用于减少模乘的计算负荷的典型算法是(例如,在上文引用的kork等人的文章中描述的)蒙哥马利算法。蒙哥马利乘法算法用一系列加法和除以2的幂来代替试除以模数,并且是如今rsa密码系统中所使用的最常见算法。

29.蒙哥马利算法可以在硬件或软件中实现。通常,硬件实现基于重复运算,这些重复运算之前是预计算一个或多个值,并且之后可以是进位传播操作和最终模校正。预计算值可以是例如(2

2n

)%r,其中n是蒙哥马利操作数的位数,“%”表示模运算,并且r即除数是预选数(r《2n)。

30.这里描述的本发明的实施方式提供用于计算蒙哥马利预计算值的高效方法和设备。在一些公开的实施方式中,蒙哥马利乘法设备(mma)被配置为将两个被乘数相乘再按预定义数取模。在一些实施方式中,mma包括预计算电路和蒙哥马利乘法电路。预计算电路被配置为通过进行一系列迭代来计算蒙哥马利预计算值。在给定迭代中,预计算电路通过对先前迭代中所计算出的中间值进行逐位运算来修改一个或多个中间值。在实施方式中,在给定迭代中,预计算电路通过对(i)先前迭代中所计算出的逐位和、(ii)先前迭代中所计算出的逐位进位的两倍、以及(iii)模校正数进行逐位和与逐位进位运算来修改逐位和与逐位进位。蒙哥马利乘法电路被配置为通过使用预计算电路所计算出的蒙哥马利预计算值进行多个蒙哥马利归约运算来将两个被乘数相乘,再按除数取模。

31.在一些实施方式中,将另外两位添加到预计算和/或蒙哥马利乘法的操作数,以避免最终模校正步骤;因此,对于4096位算术,使用4098位操作数。添加两位还防止中间值的溢出。

32.这里提出的根据本发明的其它实施方式提供了集成蒙哥马利计算引擎(imce),其中预计算电路嵌入在蒙哥马利乘法电路中;在实施方式中,在预计算和蒙哥马利乘法期间使用相同的逐位和与逐位进位电路。

33.在一些实施方式中,imce包括csa和控制电路。控制电路被配置为在多个设置中管理csa的操作;在第一设置中,控制电路控制csa以进行蒙哥马利预计算计算;在第二设置中,控制电路控制csa以进行蒙哥马利乘法,并且在第三设置中,控制电路控制csa以使用蒙哥马利乘法的序列来计算取幂。在实施方式中,控制电路包括被配置为控制csa的环回输入的第一电路以及可将csa(通过第一电路)配置为计算取幂的第二电路。

34.在下文描述的示例实施方式中,蒙哥马利操作数的位数是4098;然而,所公开的技术不限于4098位;可以在替代实施方式中使用任何其它合适的位数。

35.所公开的mma和imce可以嵌入在各种主机系统中并且在各种用例中使用。一般来说,涉及蒙哥马利乘法的任何系统可以从这里描述的技术中受益。示例主机系统包括各种网络装置,诸如网络适配器(例如,以太网网络接口控制器(nic)、infiniband主机通道适配器(hca)、数据处理单元(dpu)或“智能nic”、支持网络的图形处理单元(gpu))、网络交换机和路由器以及加速器等。

36.在一个示例用例中,所公开的mma和/或imce嵌入在网络装置中并且用于网络装置的安全引导过程,例如用于签名的认证。在另一示例用例中,所公开的mma和/或imce嵌入在网络适配器中并且用于使诸如公钥操作等的加密操作加速。系统描述

37.图1是示意性地图示根据本发明的实施方式的蒙哥马利乘法设备(mma)100的框图。mma 100计算数对的乘积再按大素数n取模,并且包括蒙哥马利计算引擎(mce)102、蒙哥马利预计算单元(mpc)104和处理器106。这里,mce 102也称为蒙哥马利乘法电路。根据可应用的主机系统和用例,处理器106可以包括或者可以嵌入在例如cpu、gpu、片上系统(soc)、

控制器、数字信号处理器(dsp)或任何其它合适类型的处理器中。

38.mce 102被配置为从处理器106接收乘法自变量a、b和除数n以及从mpc 104接收预计算值2r%n,并将乘积(a*b)%n输出到处理器106。mce 102可以是执行合适软件程序的处理器、或硬件蒙哥马利乘法器(例如,参见thampi和jose的“montgomery multiplier for faster cryptosystems”,procedia technology 25(2016),第392-398页)。在一些实施方式中,mce 102包括计算基于蒙哥马利乘法的指数(例如,参见以上引用的mclvor等人的文章)的附加电路。

39.mpc 104被配置为从处理器106接收n和-n。n和-n通常以n 2位表示,其中n是蒙哥马利乘法中所使用的位数(-n可以由“二进制补码”表示来表示:-n=~n 1(n逆 1))。

40.然后,mpc 104计算预计算值(2

2n

)%n,并将结果发送至mce 102。在实施方式中,mpc包括三个或四个输入进位保留加法器(csa),并在接近n(位数)的循环数中完成计算。

41.处理器106被配置为向mce 102和mpc 104发送操作数(被乘数),并从mce 102接收乘法结果。在一些实施方式中,例如,如果mpc 104包括处理器,则可能不需要处理器106。

42.mma 100的配置是仅为了概念清楚而描绘的示例配置。可以在本发明的替代实施方式中使用其它合适的配置。例如,在一些实施方式中,单个mpc被配置为预计算多个mce的值。在另一示例中,mpc 104被配置为通过求n的二进制补码来计算-n;因此,处理器106不向mpc 104发送-n。

43.在一些实施方式中,处理器106和/或mpc 104包括通用处理器,该通用处理器在软件中被编程以执行这里描述的功能。软件可以例如以电子形式、通过网络或从主机下载到处理器,或者软件可以可替代地或另外提供和/或存储在诸如磁存储器、光存储器或电子存储器等的非暂时性有形介质上。

44.图2是示意性地图示根据本发明的实施方式的蒙哥马利预计算电路(mpc)104的框图。mpc包括四输入进位保留加法器(csa)200,该csa 200被配置为对四个输入(指定为in[0]到in[3])求和。-n(n是模除数)的值被(例如,从处理器106,图1)输入到mpc。并且被应用到与门202的r_0输入和与门204的r_1输入。与门202和204被配置成在使能时将-n输入(分别)传送到csa的输入in[0]和in[1],否则传送值“0”。(与门202和204的使能输入分别称为en_0和en_1。)

[0045]

应当注意,当en_0和en_1都关闭(例如,在逻辑0)时,csa 200在输入in[0]和in[1]接收组合值“0”;当en_0、en_1中的一个开启时,csa接收组合值

“‑

n”,并且当en_0、en_1都开启时,csa接收组合值

“‑

2n”。

[0046]

两个寄存器(r_c寄存器206和r_s寄存器208)被配置成分别存储csa 200的进位输出与和输出。存储在r_c 206中的数据可以通过移位器210路由回到csa 200的in[3]输入,而存储在r_s 208中的数据可以通过移位器212路由回到in[2]输入。移位器210和212被配置为通过将数据左移一个位置(最右边的输出位被设置为逻辑0)来乘以2。

[0047]

mpc 104还包括控制单元214,该控制单元214被配置为驱动与门202和204的输入en_0和en_1。如以下(参考图3)所述,在实施方式中,只有n和r_sc中的几个更高有效位(例如,五个最高有效位)被输入到控制单元214。

[0048]

在实施方式中,mpc 104所执行的预计算处理包括csa 200生成预计算值的和与进位表示的进位保留阶段、以及和与进位(分别存储在r_s 208和r_c 206中)相加以产生预计

算值p=2

2n

%n的进位传播阶段。根据图2中图示的示例实施方式,mc 104包括全加器216,该全加器216被配置为将存储在r_s 208和r_c 206中的值相加,以便产生预计算值p。在示例实施方式中,全加器216包括64位,并且可以在64个循环中进行4096位加法(如以下将描述的,在csa中可能需要另外两位,因此,全加器216可能需要65个循环来执行4098位加法)。

[0049]

总之,mpc 104在迭代进位保留阶段再是迭代进位传播阶段中计算p=2

2n

%n。在进位保留阶段中,4输入csa通过将0、-n或-2n的值以及前一次迭代的左移进位和保留结果相加来迭代地计算p。在进位传播阶段中,全加器迭代地对进位保留阶段的进位与和进行求和,以产生p。

[0050]

如将理解的,mpc 104的配置是仅为了概念清楚而描绘的示例配置。可以在本发明的替代实施方式中使用其它合适的配置。例如,可以使用三输入csa而不是四输入csa,其中与门202、204被复用器代替,该复用器被配置为将0、-n或-2n输出到代替in[0]和in[1]的单个csa输入。在实施方式中,可以不需要移位器210和/或212;作为替代,r_s和r_c可以以移位的方式连线到in[2]和in[3](例如,r_s[0]连线到in[2][1],r_s[1]连线到in[2][2],等等)。保留最终减法级

[0051]

根据原始蒙哥马利论文及其早期实现,蒙哥马利乘法之后是最终步骤,在该最终步骤中,进行对结果c的模校正:if(c》n)c=c-n。

[0052]

该操作相对昂贵,因为它需要全进位传播。另外,通过外部测量蒙哥马利乘法循环的数量,试图找到密钥的黑客可以推论是否需要模校正,从而缩小可能的密钥值的范围。然而,在walter的一篇题为“montgomery exponentiation needs no final subtractions”的文章(electronics letters,第35卷第21期,1999)中,作者教导了在蒙哥马利乘法中的位数增加2的情况下可以如何避免最终模校正。下表描述了原始蒙哥马利算法和沃尔特建议之间的差异:

[0053]

因此,在一些实施方式中,mpc 104计算指数大于2n的预计算值,例如计算r=2

2(n 2)

。

[0054]

图3是示意性地图示根据本发明的实施方式的用于蒙哥马利预计算的方法的流程图300。流程由mpc 104(图1)执行。流程图以初始化进位保留加法步骤302开始,其中mpc将初始值设置为包括r_0、r_1、r_s和r_c(所有都在上文中参考图2进行了描述)的寄存器以及被配置为对迭代进行计数的计数器中所存储的参数。步骤302包括:将r0和r1初始化为-n的n 3位表示;将r_s初始化为2n的n 1位表示,将r_c初始化为0的n 1位表示,并将计数器初始化为4096 4。

[0055]

然后,mpc进入进位保留加法步骤304,其中mpc:i)在s_n的五个最高有效位所表示的数大于n的五个最高有效位所表示的数的情况下将en_0设置为1(en_0=1将向in[0]输出-n,而en_0=0将输出0);ii)如在s_n的六个最高有效位所表示的数大于n的五个最高有效位所表示的数的情况下将en_1设置为1(en_1=1将向in[1]输出-n,而en_1=0将输出0);iii)断言r_s的值在in[2]中左移1;iv)断言r_c的值在in[3]中左移1;v)将r_s设置为等于in[0]、in[1]、in[2]和in[3]中的和(无进位);vi)将r_c设置为等于in[0]、in[1]、in[2]和in[3]中的进位;以及vii)使计数器递减。

[0056]

(进位保留加法步骤304由下式数学定义:sum_sc[5:0]=r_s[n:n-4] r_c[n:n-4]en_0=(n[4095:4095

–

3]《sum_sc[5:0]);in0=(en_0)?-4096:0en_1=(n[4095:4095

–

3]《sum_sc[5:1]);in1=(en_1)?-4096:0in2=r_s《《1

in3=r_c《《1r_c,r_s=csa(in0,in1,in2,in3)counter=counter-1.)

[0057]

在步骤304之后,mpc进入确认csa完成步骤306并确认计数器是否已达到零值。如果是,则进位保留加法阶段结束;预计算值p=2

2n

%n的和与进位分别存储在r_s和r_c中,然后mpc将进入初始化进位传播加法步骤308。如果在步骤306中未完成进位保留加法,则mpc将重新进入步骤304,以执行下一个csa迭代。

[0058]

在步骤308中,mpc将计数器初始化为65。根据图3图示的示例实施方式,全加器216(图2)包括64位;因此,进位传播加法需要64 1次迭代(64*64=4096;需要额外的迭代,因为n略大于4096)。

[0059]

在步骤308之后,mpc进入进位传播加法步骤310,其中(通过将来自前一次迭代的进位、来自r_s的64位组和来自r_c的64位组相加来)计算输出p,并且使计数器递减。来自r_s和r_c的所选位组在连续迭代中向左移位(例如,在第一次迭代中选择位63:0,在下一次迭代中选择位127:64,等等)。

[0060]

接着,mpc进入确认进位传播加法完成(cpa完成)步骤312,并确认计数器是否已达到零值。如果是,则完成预计算流程图,并且将预计算值存储在p中。如果在步骤312中没有完成进位传播加法,则mpc重新进入步骤310,以进行下一次cpa迭代。

[0061]

如将理解的,图3中图示的流程图300是仅为了概念清楚而描绘的示例。可在本发明的替代实施方式中使用其它合适的流程图。例如,计数器可以向上计数而不是向下计数(相应地修改确认完成步骤)。在一些实施方式中,计数器可以在确认完成步骤之后递增(或递减)。预计算小数

[0062]

在一些实施方式中,用于预计算操作的位数可以小于mpc的宽度(例如,n《4096)。由于在上述的方法和电路中,响应于操作数的高阶位而执行下一个循环,因此增加了两个预备步骤:a.操作数(通过mpc、mce或处理器)左移位,直到msb=1为止;b.算法循环数减少了a)的移位计数。

[0063]

在预计算算法完成后,结果(通过mpc、mce或处理器)右移位以恢复原始位大小。具有预计算电路的集成蒙哥马利乘法器

[0064]

上述的预计算电路类似于蒙哥马利乘法电路。在一些实施方式中,预计算集成在蒙哥马利乘法电路内,从而增加了少量逻辑。

[0065]

图4是示意性地图示根据本发明的实施方式的具有集成在蒙哥马利计算引擎中的预计算电路的mma 400的框图。与mma 100(图1)相同,mma 400计算数对的乘积再按大素数n取模,但与mma 100不同,mma 400包括集成蒙哥马利计算引擎(imce)402,该imce 402被配置为从处理器404接收自变量a、b和除数n,并将乘积(a*b)%n输出到处理器404。处理器404被配置为向imce 402发送操作数(被乘数)并从imce接收乘法结果。在一些实施方式中,例如,如果imce 402包括处理器,则可能不需要处理器404。

[0066]

与mma 100中相同,在一些实施方式中,处理器404和/或imce 402包括通用处理器,该通用处理器在软件中被编程以执行这里描述的功能。软件可以例如以电子形式、通过

网络或从主机下载到处理器,或者软件可以可替代地或另外提供和/或存储在诸如磁存储器、光存储器或电子存储器等的非暂时性有形介质上。

[0067]

图5是示意性地图示根据本发明的实施方式的集成蒙哥马利计算引擎(imce)402的框图。在示例实施方式中,乘法是4096位

×

4096位(然而,如上面引用的沃尔特参考中所解释的,我们使用4096 2=4098位来保留最后模运算)。如将理解的,icme 402是mpc 104(图2)的超集;icme 402的一些子单元与mpc 104的对应子单元相同(并保留相同的子单元编号);其它子单元是对应的mpc 104子单元的超集。另外,imce 402包括三个新的子单元——控制器518(不同于控制单元214,图2)、以及两个寄存器——gpr0寄存器514和gpr1寄存器516。

[0068]

4输入csa 200对输入in[0]到in[3]进行进位保留相加。和输出和进位输出分别耦合到r_s寄存器208和r_c寄存器206。输入in[0]和in[1]分别耦合到与门202和204。与门202被配置为在信号en_0处于逻辑1时向in[0]输出r_0寄存器502的值,否则输出零,而与门204被配置为在信号en_1处于逻辑1时向in[1]输出r_1寄存器504的值,否则输出零。

[0069]

左/右移位器512被配置为使r_s 208的输出向左或向右移位,并将移位器值发送至csa 200的in[2];以类似的方式,左/右移位器510被配置为使r_c 206的输出向左或向右移位,并将移位器值发送至csa 200的in[3]。如将理解的,左/右移位器512和510是移位器212、210(图2)的超集,其被配置为仅向左移位。在一些实施方式中,cpa 216对来自r_s 208和r_c 206的位组(例如,64位组)进行进位传播相加,以将4098位进位和表示减少至4098位二进制表示;在实施方式中,gppr0 514和/或gpr1 516例如以64位组有序地加载cpa 216的输出。

[0070]

控制器518被配置为通过发送针对包括en_0、en_1的子单元的有序控制信号模式;左/右移位器512和510的移位方向控制;寄存器r_0 502、r_1 504、gpr0 514、gpr1 516的加载控制;并且通过初始化寄存器r_s 208、r_c 206的控制来管理imce 402的操作。控制器可以(例如,由处理器404,图4)配置成以下至少两个设置中的一个设置:第一设置,其中控制器管理与门202、204和移位器510、512,使得csa将计算蒙哥马利预计算值;以及第二设置,其中控制器管理与门和移位器,使得csa将计算蒙哥马利乘法。在一些实施方式中,控制器可以配置成第三设置,其中csa通过使蒙哥马利预计算设置和多次出现的蒙哥马利乘法设置级联来计算取幂(例如rsa取幂)。

[0071]

在下文中,我们将控制器518、与门202、与门204、移位器510和移位器512的聚合统称为控制电路。

[0072]

因此,根据图5中图示的示例实施方式并且如上所述,imce 402被配置为进行蒙哥马利预计算和蒙哥马利乘法(并且特别地进行蒙哥马利预计算、然后是蒙哥马利乘法)。

[0073]

如将理解的,在图5中图示并在上文中描述的imce 104的配置是为了概念清楚而描绘的示例配置。可以在本发明的替代实施方式中使用其它合适的配置。例如,在一些实施方式中,不存在cpa,并且所有操作都以和与进位表示法完成(除了可通过cpa或例如通过软件转换为二进制格式的最终取幂结果)。

[0074]

图6是示意性地图示根据本发明的实施方式的用于蒙哥马利4096位

×

4096位乘法的方法的流程图600。在图6中图示的示例实施方式中。两个被乘数扩展到4098位,以保留(如上所述的)最终模级。流程由控制电路518执行,该控制电路518控制imce 402(图5)的各

个子单元。流程图以初始化csa寄存器步骤602开始,其中控制电路将n(模数)的值加载到r0 502,将a(第一被乘数)的值加载到r1 504;将b(第二被乘数)加载到gpr1 514,并将零加载到r_s 208和r_c 206寄存器。在实施方式中,控制器在65个循环内以64位组加载4098位值。在一些实施方式中,控制器直接或通过总线从处理器(例如,处理器404,图4)接收一些或所有值。

[0075]

接着,控制电路进入初始化计数器步骤604,并以值“4098”(要执行的蒙哥马利归约的数量)加载内部计数器(未示出)。然后,控制电路进入蒙哥马利迭代步骤606,其中控制电路:i)将与门202(图5)的en0输入设置为s[0] c[0]*gpr1[0]*r1[0](位运算);ii)将与门204的en1输入设置为gpr1[0];iii)如果en_0处于逻辑1,则将r0复制到4098位in[0];否则设置in[0]=0;iv)如果en_1处于逻辑1,则将r1复制到4098位in[1];否则设置in[1]=0;v)将4098位in[2]值设置为r_s右移1;vi)将4098位in[3]值设置为r_c右移1;vii)使in[0]、in[1]、in[2]、in[3]逐位相加(保留r_s中的逐位和与r_c中的逐位进位);以及viii)使计数器递减。

[0076]

然后,控制电路进入确认计数器大于零步骤608并确认计数器值是否仍然大于零。如果是,则蒙哥马利乘法循环尚未完成,并且控制电路重新进入步骤606以执行下一次蒙哥马利迭代。如果在步骤608中计数器不大于零,则控制电路将进入初始化进位传播加法步骤610,其中控制电路将计数器设置为65,然后进入进位传播加法(cpa)步骤612。

[0077]

cpa步骤612(与图3中的步骤310相同)是64位加法,其将64r_s位组与相应的64r_c位组相加并使计数器递减。在确认cpa完成步骤614中,控制电路确认计数器是否已达到零,如果计数器仍大于零,则重新进入步骤612。当在步骤614中计数器已达到零时,流程图结束。

[0078]

如将理解的,在图6中图示并在上文中描述的流程图600是仅为了概念清楚而描绘的示例。可以在本发明的替代实施方式中使用其它合适的流程图。例如,在实施方式中,计数器可以向上计数,然后与迭代次数进行比较。在一些实施方式中,在确认计数器完成之后对计数器进行修改。rsa指数计算

[0079]

rsa算法包括大数的取幂。在上面引用的mclvor等人的文章中,作者描述了使用蒙哥马利乘法器来进行取幂。取幂形式上定义为m=c

d mod(n)。d(即指数)可以存储在控制电路518中,或者从处理器(例如,处理器204,图4)读取。

[0080]

图7是示意性地图示根据本发明的实施方式的用于取幂的方法的流程图700。流程图由控制电路518(图5)执行。取幂流程图包括预计算流程图300(图3)的执行和蒙哥马利乘法流程图600(图6)的多次执行。在下文中,我们形式上将计算k=(2

2k

)%n的蒙哥马利预计算称为precompute(k,n);并且将蒙哥马利乘法m=(a*b)%n称为montgomery(a,b,n)。

[0081]

流程图700以预计算步骤702开始,其中控制电路通过执行预计算流程(例如,流程图300(图3))来计算预计算值k=precompute(k,n)。接着,在计算初始gpr0步骤704中,控制

电路执行蒙哥马利乘法流程(例如,流程600,图6)以计算montgomery(k,c,n),并将结果存储在gpr0中。然后,在计算初始gpr1步骤706中,控制电路执行另一蒙哥马利乘法流程以计算montgomery(k,1,n),并将结果存储在gpr1中。现在,在设置计数器4098中,控制电路将计数器的值设置为4098,即取幂中的迭代次数。

[0082]

在步骤708之后,控制电路开始4098次取幂迭代的序列。gpr0将在第i次迭代之后存储c

2i

的值,而gpr1将存储c

d[i-1:0]

的累积取幂结果。在计算下一gpr0步骤710中,控制电路计算montgomery(gpr0,gpr0,n),对gpr0的先前值求平方。接着,在确认di步骤712中,控制电路确认d的第i位是否为逻辑1。如果是,则控制电路将进入更新gpr1步骤714,其中控制电路将执行蒙哥马利乘法(例如,流程图600)以计算montgomery(gpr0,gpr1,n),将结果存储在gpr1中并进入使计数器递减步骤716(如果在步骤712中,d[i]不是逻辑1,则控制电路绕过步骤714)。

[0083]

在步骤716中,控制电路使计数器递减,然后在确认计数器为0步骤718中确认计数器是否已达到0。如果是,则取幂流程结束,并且gpr1存储m即取幂结果。如果在步骤718中计数器尚未达到零,则控制电路重新进入步骤710以进行下一次取幂迭代。

[0084]

如将理解的,在图7中图示并在上文中描述的流程图700是仅为了概念清楚而描绘的示例。可以在本发明的替代实施方式中使用其它合适的流程图。例如,在实施方式中,为了防止测量取幂时间以估计逻辑1指数位的数量的安全攻击,总是执行步骤714的蒙哥马利乘法,并且(在步骤712中确认的)指数的位d[i]的值确定是否将用乘法结果来更新gpr1。在一些实施方式中,计数器在步骤708中清零,在步骤716中向上计数,并在步骤718中与4098进行比较。在实施方式中,计数器在与终值比较之后递增。小数的蒙哥马利计算

[0085]

在上述的蒙哥马利乘法方法和电路中,响应于操作数的低阶位而执行下一个循环,因此,当要乘的数的位数小于imce的宽度(例如,n《4096)时,算法良好地工作。操作数应加载到寄存器的lsb部分,并且逻辑0位应加载到未使用的ms部分。

[0086]

蒙哥马利乘法设备(mma)100和400的配置(包括蒙哥马利预计算电路(mpc)104和集成蒙哥马利计算引擎(imce)402)、上述的流程图300、600和700的方法是仅为了概念清楚而示出的示例配置和方法。在替代实施方式中可以使用任何其它合适的配置和流程图。蒙哥马利乘法设备(mma)100和400的不同元件(包括蒙哥马利预计算电路104和集成蒙哥马利计算引擎402)可以使用合适的硬件实现,诸如在一个或多个专用集成电路(asic)或现场可编程门阵列(fpga)中实现。

[0087]

尽管这里描述的实施方式主要指蒙哥马利乘法、蒙哥马利预计算和基于蒙哥马利的取幂,但这里描述的方法和系统也可用于其它应用,诸如快速除法。

[0088]

因此,将理解,通过示例的方式引用上述实施方式,并且本发明不限于上文中已经具体示出和描述的实施方式。相反,本发明的范围包括上文中描述的各种特征的组合和子组合以及本领域技术人员在阅读前述描述时可能想到并且在现有技术中未公开的变化和修改。在本专利申请中通过引用并入的文献将被认为是申请的组成部分,除非在这些并入文献中以与本说明书中明确或隐含地做出的定义相冲突的方式定义任何术语的程度上,仅应考虑本说明书中的定义。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。