1.本说明涉及放大器电路,例如多级运算跨导放大器(简称ota)类型的全差分放大器电路。

2.一个或多个实施例可以被应用于适于检测电容传感器中电荷变化的电荷放大器电路。

背景技术:

3.诸如ota的放大器电路适用于各种电子应用。

4.现有ota电路的缺点在于存在多个可能的稳定偏置点。无论用于ota的输入差分对的晶体管种类(例如,pmo或nmo)如何,都可能存在这样的缺点。

5.例如,当输入和输出共模节点处于同一恒定值时(例如,nmos输入差分对的vcm

in

=vcm

out

=0,或pmos输入差分对的vcm

in

=vcm

out

=vdd),存在不希望的稳定偏置点值。例如,经由反馈电路分支,尤其是电阻反馈分支,将这种不期望的偏置点值从输出传送到ota的输入节点。

6.因此,ota的启动级可以是相关的,以抵消在不希望的偏置条件下锁存放大器的任何风险。

7.即使有足够的启动级,多级ota在正常运行期间的虚拟接地扰动仍可能导致放大器级意外关闭。

技术实现要素:

8.一个或多个实施例的技术优点有助于克服上述缺点。

9.根据一个或多个实施例,可以通过具有下文更详细阐述的特征的电路来实现这种技术优势。多级放大器电路的启动电路可以是此类电路的示例。

10.一个或多个实施例可以涉及对应的多级放大器电路。

11.一个或多个实施例可以涉及对应的方法。用于ota的启动方法可以是此类电路的示例。

12.一个或多个实施例可以抵消由于过程电压温度(简单地说,pvt)电路变化而导致的性能劣化。

13.一个或多个实施例可以有助于提高电路对非理想性的鲁棒性,例如噪声和失配,否则可能降低准确度。

14.一个或多个实施例可使用相对简单的布置提供对现有解决方案的有效改进。

15.一个或多个实施例有助于在不损失性能的情况下提供启动网络。

16.一个或多个实施例可有助于提供紧凑、节省面积的解决方案。

17.在至少一个实施例中,提供了一种用于多级放大器电路的启动电路,该多级放大器电路具有至少包括第一差分级的差分级级联。启动电路包括输入节点对和至少两个输出节点,其被配置为耦合到多级放大器电路。启动差分级包括差分晶体管对,该差分晶体管对

具有耦合到该对输入节点的相应控制端子,并且该差分晶体管对的每个晶体管在该至少两个输出节点的相应输出节点和共用源极端子之间具有相应的电流路径。启动差分级被配置为感测多级放大器电路的第一差分级处的共模压降。电流镜电路装置包括以电流镜布置的多个晶体管,这些晶体管耦合到差分晶体管对的共用端子,并且耦合到至少两个输出节点的两个输出节点。至少两个输出节点被配置为至少耦合到多级放大器电路的第一差分级。电流镜电路装置被配置为在启动差分级的共用源极处执行电流变化的电流镜像,并且作为结果补偿在多级放大器电路的第一差分级处感测的共模压降。

18.在至少一个实施例中,提供了一种多级放大器,其包括第一输入节点对和第一输出节点对。差分级的级联至少包括耦合到该第一输入节点对的第一差分级和耦合到该第一输出节点对的第二差分级。启动电路至少耦合到第一差分输入级。启动电路包括耦合到第一差分级的第二输入节点对和至少两个第二输出节点。启动差分级包括在启动电路中,并且包括第一差分晶体管对,其具有耦合到该对第二输入节点的相应控制端子,第一差分晶体管对的每个晶体管在至少两个第二输出节点的相应第二输出节点和共用源极端子之间具有相应的电流路径。启动差分级被配置为感测多级放大器电路的第一差分级处的共模压降。所述启动电路还包括电流镜电路装置,所述电流镜电路装置包括以电流镜布置的多个晶体管,多个晶体管耦合到所述第一差分晶体管对的共用端子,并且耦合到所述至少两个第二输出节点的两个第二输出节点。电流镜电路装置被配置为在启动差分级的共用源极处执行电流变化的电流镜像,并且在第一差分级补偿感测到的共模压降。

19.在至少一个实施例中,提供了一种多级放大器电路的操作方法,其包括:经由多级放大器电路的启动差分级,感测在多级放大器电路的差分级级联的第一差分级处的共模压降,所述第一差分级耦合到第一输入节点对,所述多级放大器电路进一步包括耦合到第一输出节点对的第二差分级,所述启动差分级包括第一差分晶体管对,所述第一差分晶体管对具有耦合到第二输入节点对的相应控制端子,所述第一差分晶体管对中的每个晶体管在相应的第二输出节点与共用源极端子之间具有相应的电流路径;在启动差分级的共用源极处执行电流变化的电流镜像;以及作为电流镜像的结果,补偿在多级放大器电路的第一差分级处感测到的共模压降。

附图说明

20.现在将参考附图,仅通过非限制性示例来描述一个或多个实施例,其中:

21.图1是电荷放大器的示例图;

22.图2是运算跨导放大器的示例电路图;

23.图3是电荷放大器的示例图,其在虚拟接地上具有复位开关;

24.图4是具有启动电路部分的运算跨导放大器的示例性电路图;

25.图5是启动电路部分的一个或多个实施例的示例性电路图;

26.图6是级联放大器的示例电路图;以及

27.图7是图5的备选实施例的示例性电路图。

具体实施方式

28.在接下来的描述中,说明了一个或多个具体细节,旨在提供对本描述的实施例的

示例的深入理解。可以在没有一个或多个特定细节的情况下,或者使用其他方法、组件、材料等来获得实施例。在其他情况下,未详细说明或描述已知结构、材料或操作,以便不会模糊实施例的某些方面。

29.在本描述的框架中对“实施例”或“一个实施例”的引用旨在指示在至少一个实施例中包含关于该实施例描述的特定配置、结构或特征。因此,在本说明书的一个或多个要点中可能出现的诸如“在一个实施例中”或“在一实施例中”之类的短语不一定指同一个实施例。

30.此外,特定构象、结构或特征可以在一个或多个实施例中以任何适当方式组合。

31.在本文所附的附图中,类似的部件或元件用类似的附图标记/数字表示,为了简洁起见,将不重复相应的描述。

32.本文使用的参考文献仅为方便而提供,因此不限定保护范围或实施例的范围。

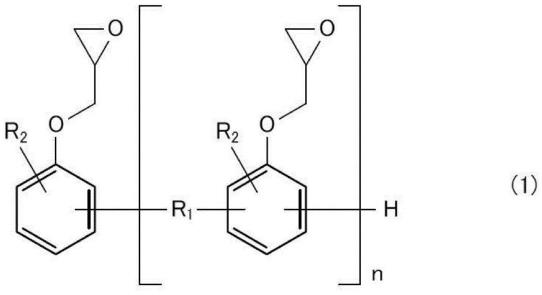

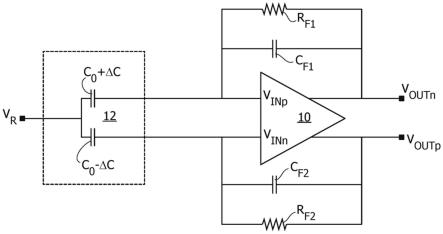

33.图1显示了电荷放大器电路10的示例图,该电路可以包括:

34.偏置节点vr,其被配置为以本身已知的方式耦合到一些电压源;

35.电容传感器12,其耦合至基准节点vr,并且具有差分可变电容,其值为c0

±

δc;以及

36.运算跨导放大器(ota)10,其可以具有:

37.非反相输入节点v

inp

,连接到传感器12并且经由包括第一rc网络r

f1

、c

f1

的第一反馈支路耦合到第一输出节点v

outn

;以及

38.反向输入节点v

inn

连接到传感器12并且经由包括第二rc网络r

f2

、c

f2

的第二反馈支路耦合到第二输出节点v

outp

。

39.如图1所示,ota 10的输入vcm

in

、输出vcm

out

共模电压电平可以表示为:

[0040][0041][0042]

由于反馈rc网络r

f1

、c

f1

、r

f2

、c

f2

的存在,可能需要具有相同的输入和输出共模电压电平,即

[0043]

vcm

in

=vcm

out

=vcm。

[0044]

如图2和图3所示,如图1所示的ota 10的电路图可以包括电子晶体管的多级布置。

[0045]

为了简单起见,本文参考包括两个(差分)级的多级布置来讨论实施例,否则应理解,这样的级的数量纯粹是示例性的,而不是限制性的,因为一个或多个实施例在概念上可以包括任意数量的级。

[0046]

为了简单起见,以下主要针对使用nmos晶体管作为差分对实现的ota电路讨论一个或多个实施例,否则应理解,这种类型的晶体管技术纯粹是示例性的而不是限制性的。一个或多个实施例可以使用pmos或任何其他种类的晶体管技术。

[0047]

如图2所示,两级ota电路10包括例如nmos晶体管的布置,该电路布置包括:

[0048]

ota 10的差分输入节点对v

inp

、v

inn

;

[0049]

第一差分级,包括第一差分晶体管对m1、m2,其在相应的漏极端子和共用源极端子vtail

之间具有相应的电流路径,ota 10的输入节点耦合到第一差分晶体管对m1、m2的相应控制节点v

inp

、v

inn

;

[0050]

在多个电流发生器处,例如,至少三个电流发生器m0、m7、m8,包括被配置为在第一差分晶体管对m1、m2的共用源极端子v

tail

处镜像“尾”电流的晶体管;

[0051]

第二差分级,包括第二差分晶体管对m5、m6,其相应的控制节点v

1p

、v

1n

耦合到第一差分晶体管对m1、m2的相应漏极端子,晶体管m5、m6在耦合到偏置电压vdd的相应漏极节点与相应输出节点v

outp

、v

outn

之间具有相应的信道路径;晶体管m5、m6的相应输出节点v

outp

、v

outn

经由相应的反馈电容器cc耦合到其相应的控制节点v

1p

、v

1n

;

[0052]

两个有源负载级m3、m4耦合至第一差分晶体管对m1、m2的漏极端子,即耦合至第二差分晶体管对m5、m6的控制端子v

1p

、v

1n

,以及耦合至参考/偏置电压vdd;每个有源负载级m3、m4包括相应的第一晶体管对m

3a

、m

4a

和第二晶体管m

3b

、m

4b

,其中:i)第一晶体管m

3a

、m

4a

的控制端子连接到相应有源级m3、m4的控制节点v

ctrl

,以及ii)相应的第二晶体管m

3b

,m

4b

耦合到偏置节点vdd,并且被配置为作为参考电流的电流发生器工作;以及

[0053]

输出共模反馈(ocmfb)级20耦合到两个有源负载级m3、m4的控制端子v

ctrl

,ocmfb级20配置为促进通过设计选择的偏置点的稳定性,例如,参考共模电压电平vcm=vcm0。

[0054]

在一个或多个实施例中,以本领域技术人员已知的方式,如图2所示的有源负载m3、m4的布置可以促进共模反馈回路的补偿和ota电路的第二输出级上的电流节省。

[0055]

除了选定的稳定共模电压电平vcm0外,图2的电路还可以具有第二寄生稳定共模电压电平,例如vcm=0伏。这可以是由于节点v

1p

和v

1n

(当输入节点接地时,即v

inp

=v

inn

=0伏)被有源负载m3、m4(其控制节点不由ocmfb网络20驱动)的第二晶体管m

3b

、m

4b“上拉”到偏置电压电平vdd。因此,输出节点也可以接地,即v

outp

=v

outn

=0伏,寄生值因此成为共模电压电平。如前所述,如图1所示,该寄生偏置点可以经由反馈支路,尤其是经由反馈电阻r

f1

和r

f2

传输到ota的输入节点,反馈电阻r

f1

和r

f2

引入正共模反馈并且在vcm

in

=vcm

out

=0volts状态中锁存电路。

[0056]

抵消将ota锁存在寄生稳定点上的风险的方法涉及引入包括复位阶段的启动阶段,以便迫使ota 10的输入节点v

inp

、v

inn

达到所选择的共模电压电平,例如vcm=vcm0。如图3所示,这可能涉及提供共模节点vcm的ota电路10,并且在此类共模节点vcm与ota 10的输入节点之间耦合一对开关s1、s2,这些开关被配置为由来自启动阶段逻辑的复位信号rst驱动(在图中不可见)。

[0057]

在各种应用中,尤其是在微机电系统(mems)中,通常情况下,在正常操作期间,共模激励仍然可以在ota的虚拟接地上发生,该事件可能导致放大器10关闭。

[0058]

解决这些问题的第一种方法可以涉及引入启动电路40,如图4所示。在所考虑的示例中,启动电路40可以包括启动晶体管对m

9a

、m

9b

,例如,使用nmos技术,启动晶体管具有耦合在它们之间并且耦合到偏置节点v

biasn

的相应的控制端子,启动晶体管对m

9a

、m

9b

共用源极具有耦合到第二差分对m5、m6的相应控制端子v

1p

、v

1n

的相应漏极端子与第一差分晶体管对m1、m2的共用源极端子v

tail

之间的、穿过启动晶体管的相应电流路径。

[0059]

如图4所示,启动电路40的设计使得启动晶体管m

9a

、m

9b

:

[0060]

在第一(例如)关断状态下,当ota 10的输入节点v

inp

、v

inn

在所选择的偏置点处被偏置时,例如vcm=vcm0;以及

[0061]

在第二(例如)接通状态下,当共模扰动导致ota 10的输入节点v

inp

、v

inn

处的电压降时,使得当第一差分对m1、m2的共用源极节点v

tail“跟随”该电压降时,电流在启动电路晶体管m

9a

、m

9b

中流动,该电流充当第二差分晶体管对m5、m6的控制端子v

1p

、v

1n

的“下拉”,平衡通过有源负载m3、m4的相应第二晶体管m

3b

、m

4b

的“上拉”。

[0062]

可选地,除了启动电路40之外,还可以存在ocmfb电路20(尽管在图4中不可见)。在这种情况下,启动电路40根据偏置电流的哪一部分由驱动有源负载级m3、m4的第一晶体管m

3a

、m

4a

的ocmfb电路20控制而有效。例如,由ocmfb电路20管理的低电流可以导致ota 10的输出分支上的更容易稳定和更低电流,同时对启动电路40构成约束,尤其是在高传导性方面,以抵消有源负载级m3、m4的第二晶体管m

3b

、m

4b

的上拉效应。这些限制可能会带来启动电路面积占用方面的成本,这可能占输入差分对m1、m2尺寸的50%到100%。当从任何给定的输入共模变化恢复正确的偏置点时,在任何pvt情况下保持启动电路40足够高的传导性也可能导致启动电路40开启,从而对级10的输入跨导产生负面影响。例如,这可能导致ota 10的性能在带宽和噪声方面的后续降低。

[0063]

如图5所示,一种改进的启动电路50,例如,在nmos技术中,可以用来代替电路40,包括:

[0064]

启动差分级m

su1

、m

su2

,具有输入节点对v

sup

、v

sun

和输出节点对v

1p

、v

1n

,其被配置为耦合到ota 10的第二差分晶体管对m5,m6的控制端子v

1p

、v

1n

,启动差分级包括差分晶体管对m

su1

、m

su2

,差分晶体管对对m

su1

、m

su2

具有连接到启动差分级的输入节点v

sup

、v

sun

的相应控制端子,晶体管m

su1

、m

su2

的差分对具有在启动差分级的输出节点的相应漏极节点和共用源极节点之间的相应电流路径;

[0065]

另一对晶体管m

su4

、m

su5

,具有耦合到偏置节点v

biassu

的相应控制端子,并且晶体管具有在启动差分电路的输出节点v

1p

、v

1n

与ota 10第一级的第一晶体管对m1、m2的共用源极节点v

tail

之间的、穿过该晶体管的相应电流路径;以及

[0066]

电流镜晶体管m

su3

,将启动差分对的共用源极节点与另一对晶体管m

su4

、m

su5

的控制端子耦合。

[0067]

如图5所示,当ota 10的输入节点v

inn

、v

inp

处存在共模压降时,晶体管m5、m6的第二差分对的控制端子v

1p

、v

1n“上拉”到更高的电压电平,导致电流流过启动差分晶体管m

su1

和m

su2

;这会增加它们相应的偏置电压v

gs

,从而改变控制端子v

inp

、v

inn

电压和共用源极端子处的电压电平二者。结果,共模扰动期间的这种变化作为电流注入二极管m

su3

(例如,使用电流再利用方法),并且由此经由额外晶体管m

su4

和m

su5

镜像回第二差分晶体管对m5、m6的控制端子v

1p

和v

1n

,重新平衡其输入共模变化。这指示启动网络50的整体下拉效率增加。

[0068]

在如图5所示的一个或多个实施例中,可以使用在m

su3

与m

su4

、m

su5

对之间的镜像比来作为自由参数来优化晶体管的尺寸。

[0069]

通过在其控制端子v

1p

、v

1n

以及源端子v

tail

上应用“下拉”效应来重新平衡晶体管m5、m6的第二差分对,有助于在针对任何pvt情况下以理论上相同的方式操作启动电路50。此外,与图4中的解决方案相比,在使用较少的(电路)面积时,这是可能的。

[0070]

如前所述,图2所示的ota电路10可以用任何晶体管技术实现。如图6所示,这包括已知的共源共栅技术,其中:

[0071]

第一差分级m1、m2使用馈入相应的共基极级m1s、m2s的相应的共发射极级m

nc1

、m

nc2

的一对共源共栅布置来实现,其中相应的差分共源共栅节点v

cn1

、v

cn2

插置在相应的共基极级与相应的共发射极级之间;并且

[0072]

在两个有源负载m3、m4中,第一晶体管m

3a

、m

4a

使用馈入相应的共基极级m

3as

、m

4as

的相应的共源共栅级m

pc1

、m

pc2

的一对共源共栅布置来实现,其中相应的共源共栅节点v

cp1

、v

cp2

插置在相应的共基极级与相应的共源共栅布置对之间。

[0073]

图7是适用于与ota 10的共源共栅实现(见图6)结合使用的备选启动电路70的电路图。

[0074]

如图7所示,共源共栅启动电路70可以包括:

[0075]

启动差分级m

su1

、m

su2

,具有输入节点对v

sup

、v

sun

和输出节点对v

cp1

、v

cp2

,输出节点对v

cp1

、v

cp2

被配置为耦合到ota 10的有源负载m3、m4的第一晶体管的共源共栅节点的控制端子v

1p

、v

1n

,启动差分级包括差分晶体管对m

su1

、m

su2

,差分晶体管对m

su1

、m

su2

的相应的控制端子连接到启动差分级的输入节点v

sup

、v

sun

,差分晶体管m

su1

、m

su2

的差分对具有在启动差分级的输出节点处的相应的漏极节点与共用源极节点之间的、穿过该晶体管的相应的电流路径;

[0076]

另一对晶体管m

su4

、m

su5

,具有耦合到偏置节点v

biassu

的相应的控制端子,并且具有在差分共源共栅节点v

cp1

、v

cp2

与ota 10的第一级的第一差分晶体管对m1、m2的共用源极节点v

tail

之间的、穿过该晶体管的相应的电流路径;以及

[0077]

将启动差分对m

su1

、m

su2

的共用源极节点与另一对晶体管m

su4

、m

su5

的控制端子耦合的电流镜晶体管m

su3

。

[0078]

否则应理解的是,本说明书附图中例示的各种单独实施方案不一定旨在以附图中例示的相同组合采用。因此,一个或多个实施例可以针对附图中例示的组合单独和/或以不同的组合采用这些(非强制性的)选项。

[0079]

在不损害基本原则的情况下,细节和实施例可能会在不脱离保护范围的情况下,就仅以示例的方式描述的内容而言,发生甚至显著的变化。

[0080]

一种用于多级放大器电路(10)的启动电路(50;70)可总结为包括:至少包括第一差分级(m1,m2)的差分级级联,启动电路(50;70)包括:输入节点对(v

sup

,v

sun

)和配置为耦合到所述多级放大器电路(10)的至少两个输出节点(v

1p

,v

1n

;v

cp1

,v

cp2

,v

cn1

,v

cn2

),启动差分级,包括差分晶体管对(m

su1

,m

su2

),其相应的控制端子耦合到电路(50;70)的所述输入节点对(v

sup

,v

sun

),所述差分晶体管对(m

su1

,m

su2

)中的每个晶体管(m

su1

)具有在所述至少两个输出节点(v

1p

,v

1n

;v

cp1

,v

cp2

,v

cn1

,v

cn2

)中的相应输出节点(v

1p

,v

1n

;v

cp1

,v

cp2

,v

cn1

,v

cn2

)与共用源极端子之间的、穿过晶体管的相应的电流路径,启动差分级被配置为感测(m

su1

,m

su2

)所述多级放大器电路(10)的所述第一差分级(m1,m2)处的共模压降,电流镜电路装置(m

su3

、m

su4

、m

su5

)包括以电流镜布置的多个晶体管,这些晶体管耦合到所述第一差分晶体管对(m

su1

、m

su2

)的所述共用端子,并且在所述至少两个输出节点(v

1p

,v

1n

;v

cp1

,v

cp2

,v

cn1

,v

cn2

)中具有两个输出节点(v

1p

、v

1n

;v

cn1

、v

cn2

),其中,至少两个输出节点(v

1p

,v

1n

;v

cn1

,v

cn2

)被配置为至少耦合到所述多级放大器电路(10)的所述第一差分级(m1,m2),其中,所述电流镜电路装置(m

su3

、m

su4

、m

su5

)被配置为在所述启动差分级的共用源极处执行电流变化的电流镜像,从而补偿所述多级放大器电路(10)的所述第一差分级(m1、m2)处的所述感测共模压降。

[0081]

所述至少两个输出节点(v

1p

,v

1n

;v

cp1

,v

cp2

,v

cn1

,v

cn2

)可以包括两个输出节点(v

1p

,v

1n

),其中所述电流镜电路装置(m

su3

,m

su4

,m

su5

)的所述两个输出节点分别耦合到第一差分晶

体管对(m

su1

,m

su2

)的所述输出节点中的相应输出节点。

[0082]

电流镜电路装置(m

su3

、m

su4

、m

su5

)可以具有电流镜像参数,其根据电流镜电路装置(m

su3

、m

su4

、m

su5

)中的多个晶体管中的晶体管的相应大小比而变化。

[0083]

一种多级放大器(10)可概括为包括输入节点对(v

inp

,v

inn

)和输出节点对(v

outp

,v

outn

),差分级(m1,m2,m5,m6)的级联包括耦合到所述输入节点对(v

inp

,v

inn

)的至少一个第一差分级(m1,m2)和耦合到所述输出节点对(v

outp

,v

outn

)的另一差分级(m5,m6),以及根据示例1至3中任一项所述的启动电路(50;70),启动电路(50;70)至少耦合到第一差分输入级(m1,m2)。

[0084]

所述第一差分级(m1,m2)可包括第一差分晶体管对,其中第一晶体管(m1)和第二晶体管(m2)各自在相应的输出漏极端子和共用源极端子(v

tail

)之间具有相应的电流路径,其中所述启动电路(50;70)可以具有第一输出节点和第二输出节点(v

1p

,v

1n

),第一输出节点(v

1p

)耦合到所述第一差分级(m1,m2)的第一差分晶体管对的所述第一晶体管(m1)的第一输出漏极端子,第二输出节点(v

1n

)耦合到所述第一差分级(m1,m2)的所述第一差分晶体管对的第二晶体管(m2)的第二输出漏极端子。

[0085]

所述第一差分级(m1,m2)可以包括第一差分晶体管对,每个晶体管具有在相应的输出漏极端子与共用源极端子(v

tail

)之间的、穿过该晶体管的相应的电流路径,多级放大器还可以包括耦合在第一差分级(m1,m2)的所述输出漏极端子与至少一个额外差分级的输入节点之间的有源负载级(m3,m4),每个有源负载级(m3,m4)包括耦合在它们之间的开关(m

3a

,m

4a

)和电流发生器(m

3b

,m

4b

),所述启动电路(50;70)可进一步耦合至所述额外差分级(m5,m6)和所述有源负载级(m3,m4)中的至少一项。

[0086]

第一差分级(m1,m2)可以包括相应的共发射极级(mnc1,mnc2)的一对共源共栅布置,该共源共栅布置馈入相应的共基极级(m1s,m2s),其中差分共源共栅节点(v

cn1

,v

cn2

)被插置在其间,其中,所述有源负载级(m3,m4)的所述开关(m

3a

,m

4a

)可以使用一对共源共栅布置来实现,该共源共栅布置的一对共用源极发射极级(m

pc1

,m

pc2

)馈入到相应的共基极级(m

3as

,m

4a

s)中,其中相应的共源共栅节点(v

cp1

,v

cp2

)插置在其之间,其中所述启动电路(50,70)可以具有耦合到所述有源负载级(m3,m4)的所述开关(m

3a

,m

4a

)的所述共源共栅节点(vcp1,vcp2)的第一输出节点对(v

cp1

,v

cp2

),以及耦合到所述第一差分级(m1,m2)的所述差分共源共栅节点(v

cn1

,v

cn2

)的第二对输出节点(v

cn1

,v

cn2

)。

[0087]

所述有源负载级(m3,m4)可具有至少一个控制端子(vctrl),其被配置为在所述有源负载级(m3,m4)中驱动所述开关(m

3a

,m4a),并且其中所述多级放大器包括耦合到有源负载级(m3,m4)的控制端子(v

ctrl

)的输出共模反馈级(20)ocmfb。

[0088]

一种多级放大器电路的操作方法可总结为:经由配置为感测的所述启动差分级,感测(m

su1

,m

su2

)所述多级放大器电路(10)的所述第一差分级(m1,m2)处的共模压降,在所述启动差分级的所述共用源极处执行电流变化的电流镜像(m

su3

、m

su4

、m

su5

),并作为所述电流镜像(m

su3

、m

su4

、m

su5

)的结果补偿(v

1p

、v

1n

;v

cp1

、v

cp2

、v

cn1

、v

cn2

)所述多级放大器电路(10)的所述第一差分级(m1,m2)处的所述感测共模压降。

[0089]

可以组合上述各种实施例以提供进一步的实施例。可以根据上述详细描述对实施例进行这些和其他改变。一般而言,在以下权利要求中,所使用的术语不应被解释为将权利要求局限于说明书和权利要求中公开的特定实施例,而应被解释为包括所有可能的实施例

以及这些权利要求所享有的全部等同物范围。因此,权利要求不受本公开的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。