一种dcs系统

技术领域

1.本实用新型涉及dcs集散控制系统领域。

背景技术:

2.现有dcs(distributed control system,分散控制系统)的io(input/output,输入输出)单元中使用mcu(micro controller unit,微控制单元)加cpld(complex programmable logic device,复杂可编程器件)的组合做数据处理,其核芯处理芯片mcu采用的是arm7内核,自带hdlc(high-level data link control,高级数据链路控制)同步通信接口,使得现有dcs中的dpu(data processing unit,处理器分散处理单元)控制器与io单元之间的通讯也主要采用hdlc协议。

3.但目前低端的mcu通常没有hdlc同步通信接口,因此在选用此种muc时,无法无法替换支持hdlc协议的mcu;并且现有dcs采用的hdlc通讯速率慢,已经不能满足大型项目高数据吞吐量的要求。

技术实现要素:

4.本实用新型的目的是为了克服现有dcs中无法采用不支持hdlc协议的mcu的问题,提供了一种dcs系统。

5.本实用新型的一种dcs系统,包括dpu控制器、多个数据输入输出链路和io单元;

6.dpu控制器的多个数据输入输出端通过can fd总线与多个数据输入输入链路一一对应地电气连接;

7.每条数据输入输出链路均包括总线分支适配单元、至少一个通用底座板和总线分支终端单元;且每条数据输入输出链路中,总线分支适配单元、至少一个通用底座板和一个总线分支终端单元依次通过两路can fd总线电气连接;

8.每个通用底座板对应至少一个io单元,且每个io单元的两路数据输入输出均通过两路can fd总线与对应的通用底座板电气连接,从而将该io单元电气连接到对应的数据输入输出链路上;且dpu控制器设置为主机,io单元均设置为dpu控制器的从机。

9.进一步地,io单元包括数据处理单元和数据通道单元;

10.数据处理单元包括mcu控制器和can fd总线收发器;

11.数据通道单元包括多路数据通道,且每路数据通道均包括端口保护单元、模数转换单元adc和电气隔离单元;

12.adc的模拟信号输入端通过端口保护单元与dcs模拟信号采集装置的模拟信号输出端电气连接,adc的数字信号输出端通过电气隔离单元与mcu控制器对应的数字信号输入端电气连接;

13.mcu控制器的串行信号输出端与can fd总线收发器的串行信号输入端电气连接,can fd总线收发器的总线数据信号输出端作为对应io单元的数据输入输出与对应的通用底座板电气连接。

14.本实用新型的有益效果是:

15.本实用新型采用一种基于can fd(can with flexible data rate,带灵活数据速率的can)总线通信的io单元,可以替换现有dcs中带有hdlc协议的mcu,从而以can fd总线协议替换hdlc协议,使得dcs中的mcu选择面更加广,且数据传输速率增加。

附图说明

16.图1为本实用新型的一种dcs系统的结构示意图;

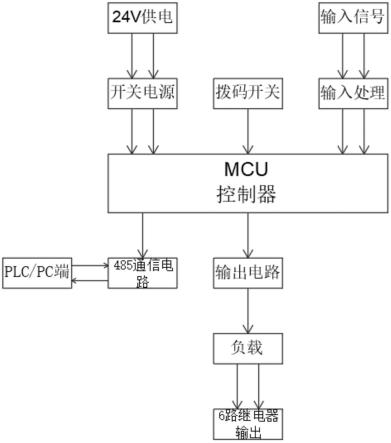

17.图2为本实用新型的一种dcs系统中io单元的结构示意图。

具体实施方式

18.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

19.需要说明的是,在不冲突的情况下,本实用新型中的实施例及实施例中的特征可以相互组合。

20.下面结合附图和具体实施例对本实用新型作进一步说明,但不作为本实用新型的限定。

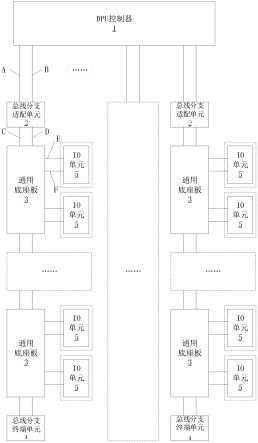

21.具体实施方式一,本实施方式的一种dcs系统,包括dpu控制器1、多个数据输入输出链路和io单元5;

22.dpu控制器1的多个数据输入输出端通过can fd总线与多个数据输入输入链路一一对应地电气连接;

23.每条数据输入输出链路均包括总线分支适配单元2、至少一个通用底座板3和总线分支终端单元4;且每条数据输入输出链路中,总线分支适配单元2、至少一个通用底座板3和一个总线分支终端单元4依次通过两路can fd总线电气连接;

24.每个通用底座板3对应至少一个io单元5,且每个io单元5的两路数据输入输出均通过两路can fd总线与对应的通用底座板3电气连接,从而将该io单元5电气连接到对应的数据输入输出链路上;且dpu控制器1设置为主机,io单元5均设置为dpu控制器1的从机。

25.具体地,如图1所示,本dcs系统设备包括dpu控制器1、总线分支适配单元2、通用底座板3、io单元5、总线分支终端单元4。dpu控制器1设有六个链路,每个链路通过两路can fd总线a和can fd总线b连通本链路上的总线分支适配单元2和通用底座板3最终在链路末端用总线分支终端单元4做终端匹配;每个通用底座板3可以插两块io单元5,分别通过两路can fd总线3和can fd总线4将io单元5连接到can fd总线网络。

26.最佳实施例,本实施例是对实施方式一的进一步说明,本实施例中,io单元5包括数据处理单元和数据通道单元;

27.数据处理单元包括mcu控制器5-1和can fd总线收发器5-2;

28.数据通道单元包括多路数据通道,且每路数据通道均包括端口保护单元5-3、模数转换单元adc5-4和电气隔离单元5-5;

29.adc5-4的模拟信号输入端通过端口保护单元5-3与dcs模拟信号采集装置的模拟

2将串行信号转成can fd总线信号与通用底座板3相连,最终实现与dpu控制器1的数据交互传输。

42.最佳实施例,本实施例是对实施方式一的进一步说明,本实施例中,dpu控制器1与总线分支适配单元2之间的can fd总线的传输介质为以太网线,且接口为rj45接口;

43.总线分支适配单元2与通用底座板3之间的can fd总线通过db25连接器电气连接,通用底座板3与总线分支终端单元4之间的can fd总线通过db25连接器电气连接;

44.通用底座板3与io单元5之间的can fd总线使用背板连接器连接。

45.具体地,其中dpu控制器1与总线分支适配单元2之间的can fd总线a和can fd总线b使用以太网线做为传输介质,dpu控制器1和总线分支适配单元2的can fd总线a和b接口为rj45;总线分支适配单元2与通用底座板3之间的can fd总线c和can fd总线d和通用底座板3与总线分支终端单元4之间的can fd总线均使用db25连接器进行连接;通用底座板3与io单元5之间的can fd总线e和can fd总线f使用48针背板连接器连接。即通用底座板3是作为对应多个io单元5的底座,并提供相应的连接器。

46.基于can fd总线通信的io单元5是低成本、高性能系统接口模块,模块具备冗余通讯功能,通讯总线遵从can fd协议。

47.采用can fd extendedframe,bitrate=500kbit/s,data bitrate=2mbit/s。

48.基于can fd的总线通讯机制应用在dcs系统中做了如下规定:

49.①

、通讯总线采用主从式结构:dpu控制器为主机,其它所有io单元5对dpu都是从机;数据线在不通讯时,不允许占用。

50.②

、dpu控制器对io单元5发送指令,模块在接收到指令0.5ms内必须应答,否则dpu控制器将认为通讯超时错误。

51.③

、从机io单元5在数据发送结束后100us内必须释放数据总线。

52.④

、对一个从机io单元5的通讯时间(从主机占用数据总线到从机发送数据完)不超过2ms。

53.⑤

、can fd对数据场的长度作了扩充,dlc最大支持64个字节,在dlc小于等于8时与原can总线是一样的,大于8时则有一个非线性的增长,最大的数据场长度可达64字节,当实际数据的长度不等于dlc的可选长度时,取大于实际数据长度且最接近dlc许可长度的数值,无效数据用0填充。

54.⑥

、id格式约定

55.优先级发送角色预留io单元5addr控制数据cmd4bits2bits2bits8bits8bits

56.扩展帧id总共29bits,为沿用原有模块地址及板卡类型体系,减小代码开发工作量,同时充分利用can fd的仲裁机制,将id的前4bits作为独立的优先级区域,预留位2bits置0,发送角色为io单元5时=1,为dpu控制器时=0;

57.⑦

、优先级规则如下:

58.[0059][0060]

新dcs系统采用了can fd总线进行数据通信传输,由于can fd是can的升级版,速率可变,最高速率可达到5mbps,最大数据长度为64byte,相对hdlc的通信速率750kbps,实现了通信速率的大幅提升。

[0061]

虽然在本文中参照了特定的实施方式来描述本实用新型,但是应该理解的是,这些实施例仅仅是本实用新型的原理和应用的示例。因此应该理解的是,可以对示例性的实施例进行许多修改,并且可以设计出其他的布置,只要不偏离所附权利要求所限定的本实用新型的精神和范围。应该理解的是,可以通过不同于原始权利要求所描述的方式来结合不同的从属权利要求和本文中的特征。还可以理解的是,结合单独实施例所描述的特征可以使用在其他实施例中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。