一种ai智能模组的可靠性设计方法

技术领域

1.本发明涉及ai智能领域,特别涉及一种ai智能模组的可靠性设计方法。

背景技术:

2.ai技术发展已进入高速时代,行业内纷纷探索利用人工智能技术为其行业赋能;因此,我们需要一款能够将高性能、高可靠性的ai芯片集成到设备上的ai智能模组,从而提供智能化的解决方案,更高效可靠地加速各种基于深度学习的算法框架搭建以实现行业快速智能化升级。

技术实现要素:

3.本发明目的是:提供一种ai智能模组的可靠性设计方法,从不同层面来提高ai智能模组的可靠性。

4.本发明的技术方案是:一种ai智能模组的可靠性设计方法,所述ai智能模组包括智能处理单元及其连接的内存单元、电源单元、以太网接口单元、pcie接口单元、温度监测单元、电流监测单元;其中,智能处理单元采用arm npu架构的智能芯片,内部集成主处理器单元cpu、神经网络单元npu、视频编解码单元vpu以及图片编解码单元jpu;ai智能模组的可靠性设计方法包括三类,第一类是基于硬件电路限流保护的方法,第二类是基于软件程序上注更新的方法,第三类是基于软看门狗、重启指令的方法;ai智能模组的程序分为固件程序、应用程序两部分,其中,固件程序包括preboot预启动程序、uboot引导程序、linux内核以及rootfs文件系统;应用程序包括神经网络模型、算法库、可执行程序及相应的脚本程序;程序上注更新过程分为两个阶段,第一阶段将固件程序和应用程序上注到三片norflash中,norflash空间可以分为两部分,第一部分存储系统固件程序,第二部分存储应用程序;第二阶段从三片norflash中通过“三取二”逻辑判断后加载其中的固件程序和应用程序,开始执行。

5.优选的,第一阶段程序上注流程包括:(1)上位机发送指令切换至“上注状态”;(2)上位机将上注数据分为若干个数据段,每段固定大小,分段进行上注,每次上注一个段时,fpga要自动先把该段擦除,然后再进行接收、解包并同时写入到三片norflash中;(3)每当接收完一个数据段时进行crc16校验,校验正确时则将bitmap相应的bit位置1;(4)上位机发送完上注数据时,发送请求bitmap遥测指令,fpga下传对应的bitmap遥测,上位机判断每个数据段上注校验的正确性,并重传错误的段;(5)当所有数据段上注成功后,上位机发送“结束上注指令”,fpga跳出norflash的烧写模式,第一阶段完成。

6.优选的,第二阶段程序上注流程包括:(1)上位机发送指令切换至“运行状态”,智能芯片启动模式切换到spi启动模式;(2)fpga控制智能芯片上电启动,智能芯片通过fpga的模拟spi接口读取norflash中的第一部分存储空间中的系统固件程序,在读取时进行三取二逻辑判断,通过对比三块nor flash中每一bit的数据是否相同,取至少两块相同的数据;(3)智能芯片启动过程中自动挂载norflash中的第二部分存储空间,此空间可根据应用需求划分成不同的分区,分别用于存储神经网络模型、算法库、可执行程序等内容。

7.优选的,程序上注更新过程还包括通过fpga来模拟spi设备:fpga将norflash第一部分模拟成一个spi flash来替代智能模组上原本的spi flash;智能芯片通过fpga模拟的spi接口读取系统固件,完成系统的加载及启动。

8.优选的,程序上注更新过程还包括通过fpga来模拟sdio设备:fpga将norflash第二部分存储空间模拟成一个sd device来替代智能模组上原本的emmc设备。 sd fakex模块和norflash共同组成一个虚拟的sd卡;其中,norflash仅仅负责提供数据的存储;sd fakex是一个verilog模块,负责对sd总线的命令进行解析和响应,并在sd host请求数据时,从norflash中读取数据并传给sd host,即fpga通过sdio将数据传给智能芯片,完成应用程序的上注更新。

9.优选的,可靠性设计还包括限流保护设计,采用2路关键电流监测来进行限流控制,2路关键电流包括1路智能芯片总输入5v电流和1路ddr 1.1v电流;2路关键电流通过外部主控fpga adc进行监测;通过后续试验,测量出智能芯片出现单粒子锁定时2路关键电流的阈值,并在主控fpga程序中按照试验得出的电流阈值进行限流控制,当超出设定的阈值时迅速切断输入电源,保护ai智能模组不受损坏;首先,主控fpga判断智能芯片的总输入电流,如果总输入电流大于阈值,则主控fpga控制ai智能模组断电重启;如果总输入电流小于阈值,则进一步判断第二路电流是否大于阈值,如果第二路电流大于阈值,则主控fpga控制ai智能模组断电重启,如果电流均小于阈值,则认为智能芯片未出现单粒子锁定现象。

10.优选的,可靠性设计还包括重启指令:在指令设计时单独设计重启指令,通过指令控制ai智能模组的加断电,外部fpga根据需要对ai智能模组进行加断电。

11.优选的,可靠性设计还包括软看门狗,ai智能模组周期性向fpga发送状态标志信息,使得fpga能够及时获取智能芯片状态信息,如设定时间未接收到智能芯片状态标志信息,则对ai智能模组进行重启操作。本发明的优点是:1.本发明的ai智能模组的可靠性设计方法,ai智能模组主要由智能处理单元、lpddr4x内存单元、电源单元、以太网单元、温度监测单元以及电流监测单元组成。ai智能模组可以通过千兆网和pcie高速接口进行数据传输,可进行图像增强、图像分类、图像目标检测、图像跟踪等智能处理,并通过串口或其它接口将处理结果返回给其他模块,加速各种基于深度学习的算法框架搭建以实现行业快速智能化升级。

12.2.本发明的ai智能模组的可靠性设计方法,整体的程序上注更新分为两个阶段,第一阶段主要完成上注数据从上位机到norflash的写入,并且将norflash存储空间划分为第一部分的系统固件空间和第二部分的应用程序存储空间。第二阶段主要完成ai芯片从norflash中读取相应的系统固件程序与应用程序。

13.3.本发明的ai智能模组的可靠性设计方法,还针对模拟spi设备、模拟sdio设备、限流保护、重启指令、软看门狗等分别进行可靠性设计,全面提升ai智能模组的高可靠性。

附图说明

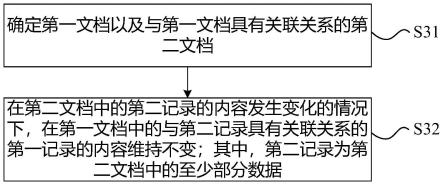

14.下面结合附图及实施例对本发明作进一步描述:图1为本发明的ai智能模组的功能框图;图2为电源单元的功能框图;图3为电源单元上电顺序控制图;图4为本发明可靠性设计方法的程序上注整体架构图;图5为第一阶段上注过程图;图6为模拟spi设备的原理图;图7为模拟sdio设备的原理图;图8为电流监测原理示意图;图9为电流监测流程图。

具体实施方式

15.如图1所示,本发明方案应用于ai智能模组设计方案中,ai智能模组主要由智能处理单元、内存单元、电源单元、以太网单元、pcie单元、温度监测单元以及电流监测单元组成。

16.ai智能模组可以通过千兆网和pcie高速接口,ai智能模组可以通过千兆网和pcie高速接口进行数据传输,可进行图像增强、图像分类、图像目标检测、图像跟踪等智能处理,并通过串口或其它接口将处理结果返回给其他模块ai智能模组其对外提供2路pcie接口,2路sgmii接口,10路gpio接口,2路spi接口,2路i2c接口,4路uart串口,2路sdio接口。

17.智能芯片作为智能处理单元的核心,该芯片采用arm npu架构,芯片内部集成主处理器单元cpu,神经网络单元npu,视频编解码单元vpu以及图片编解码单元jpu。

18.智能芯片支持2通道64bit ecc lpddr4内存,并支持多种容量,可满足各类推理场景的计算和存储需求。同时还具有丰富的外围接口,pcie、uart、spi,sdio、emmc、gpio等接口。

19.内存单元采用两片镁光的4gb(1g*32bit)的lpddr4x颗粒进行数据位扩展级联,总容量为8gb,内存颗粒型号为mt53d1024m32d4dt-053 ait:d。

20.ai智能模组采用一路dc5v电源输入,再经过dc-dc,ldo直流降压变换成不同电压给各芯片供电。使用到的电源变换模块和芯片主要采用高可靠的dc-dc和ldo芯片,主要包含三种电源芯片:dc-dc芯片rshf2000lrh(2片)、rss0508hrh(1片),ldo芯片rsw1101hrh(5片)。此外,模组采用升宇的时序控制芯片rss5004crh(2片)控制电源芯片的上电顺序,电源框图如图2所示。

21.由于模组需要多路的电源供应,且需要不同的上电顺序,因此需要增加一个上电控制时序的电路。模组多路电源需要按照一定的时序上电,虽然整个模组的电源支路有30多个分支,但通过统计一共需要10组的电源需要按顺序启动,其它的各路在各自不同的主

电源分支下,跟随主电源分支一起启动。具体的启动时序如图3所示。

22.模组电源使能驱动的时序控制,采用抗辐射的可编程的时序控制芯片来完成,选择了一款时序控制芯片rss5004crh。

23.延迟时间可以通过一个外部电阻来设定,延迟时间的调节范围可达 2ms~20ms。电源检测端口与内部高精度的参考电压比较,可实现对点电源电压的精确监控,保证延迟时间的精度。该产品同时提供多种错误检测功能:上电掉电顺序检测、误掉电检测、上电失效检测、输入错误检测、输出错误检测、外部触发错误检测。 检测到错误信号后,关闭电源系统,保护后级电路,提高系统的可靠性。

24.vdd的电压输入范围为3-16v,是内部线性稳压器的输入端。 vcc5是线性稳压器的输出端,为内部电路提供供电。vcc欠压锁定阈值为 2.8v,供电超过2.8v后内部600mv基准电压及其他模块均开启;当供电低于 2.8v时,芯片将关闭内部时钟和参考电压,所有的enx输出被拉低,直到 vcc5 低于1.2v。

25.rss5004crh lcc18 封装体积较小,便于减少pcb板面积。根据模组的电源启动时序分支要求,模组设计了1套时序控制方案,采用2片rss5004crh级联,形成多达8组的时序控制电路。

26.ai智能模组通过phy芯片88e1512将rgmii接口转换成sgmii接口,使得智能处理器能与外部板卡使用千兆网通信,模组通过sgmii接口接收图像数据进行智能计算,将处理结果返回给外部板卡。

27.88e1512是一款支持10m/100m/1000m的以太网收发器,其采用标准制造的数字cmos工艺采用56 pin 8mm x 8mm的qfn封装。该芯片内部集成一个开关稳压器产生需要使用的电源,具有超低功耗。88e1512在rgmii端支持lvcmos i/o标准。

28.ai智能模组集成了温度检测单元实时监测模组温度,防止模组因温度过高发生工作异常。

29.温度监测芯片采用高可靠性芯片tmp461-sp,该芯片是一款具有内置本地温度传感器的抗辐射、高精度、低功耗温度传感器,其温度精度表示为12位宽,分辨率为 0.0625

°

c,采用8脚的cfp封装,芯片尺寸为7.1mm x 6.2mm。采用两线串行接口smbus协议进行数据通信。

30.接口具体描述如表1所示,表1

ꢀꢀ

ai对外接口

本发明的ai智能模组的可靠性设计方法,包括以下内容。

31.s1、整体过程如图4所示,为程序上注更新整体架构图,ai智能模组的程序分为固件程序、应用程序两部分,其中,固件程序包括preboot预启动程序、uboot引导程序、linux内核以及rootfs文件系统;应用程序包括神经网络模型、算法库、可执行程序及相应的脚本程序;其中,上注过程可以分为两个阶段,第一阶段将上注数据上位机(包含固件和应用)上注到三片norflash中, norflash主要分为两个部分,第一部分存储系统固件程序,第二部分存储模型、算法库、应用程序;第二阶段从三片norflash中通过“三取二”逻辑判断后加载其中的固件程序和应用程序,开始执行。

32.如图5所示,第一阶段详细过程如下:上注时上位机程序将待上注的数据文件分为若干个数据段,每段为固定大小,每个数据段分为若干个数据包进行上注,数据包的最大数据量由传输协议决定,fpga对每个数据段进行校验并记录检验结果下传,针对错误数据段设计了重传机制,最大限度节省链路资源,程序上注完整流程如下:(1)上位机发送指令切换至“上注状态”;(2)上位机将上注数据分为若干个数据段,每段固定大小,分段进行上注,每次上注一个段时,fpga要自动先把该段擦除,然后再进行接收、解包并同时写入到三片norflash中;(3)每当接收完一个数据段时进行crc16校验,校验正确时则将bitmap相应的bit位置1;(4)上位机发送完上注数据时,发送请求bitmap遥测指令,fpga下传对应的bitmap遥测,上位机判断每个数据段上注校验的正确性,并重传错误的段;(5)当所有数据段上注成功后,上位机发送“结束上注指令”,fpga跳出norflash的烧写模式,第一阶段完成。

33.第二阶段详细过程如下:(1)上位机发送指令切换至“运行状态”,智能芯片启动模式切换到spi启动;

(2)fpga控制智能芯片上电启动,智能芯片通过fpga的模拟spi接口读取norflash中的第一部分存储空间中的系统固件程序,在读取前进行三取二逻辑判断,通过对比三块nor flash中每一bit的数据是否相同,取至少两块相同的数据;(3)智能芯片启动过程中自动挂载norflash中的第二部分存储空间,此空间可根据应用需求划分成不同的分区,分别用于存储神经网络模型、算法库、应用程序等内容。

34.s2、模拟spi设备程序上注更新过程还包括通过fpga来模拟spi设备,fpga将norflash第一部分模拟成一个spi flash来替代智能芯片原本的spi flash。智能芯片通过fpga模拟的spi接口读取系统固件,完成系统的加载及启动。

35.如图6所示,左侧spi host为智能芯片,spi fakex是一个verilog模块,用来将norflash的bpi接口转成spi接口连接在智能芯片上,fpga fakex norflash的第一部分组成spi device取代智能芯片上原本spi flash的功能,实现智能芯片直接从fpga norflash中读取并加载固件程序。

36.s3、模拟sdio设备程序上注过程还包括通过fpga来模拟sdio设备。系统启动完成后,需要将存有应用程序的sd卡挂载到相应目录下,本项目采用fpga norflash来模拟sd卡。模拟sd卡和普通sd卡一样,能够在系统下被识别,从而将存在nor flash中的应用及应用驱动搬到系统目录下。

37.如图7所示,fpga将norflash第二部分模拟成一个sd device,左侧sd host是sd卡主机,往往是读卡器、嵌入式微处理器等。右侧的sd fakex和norflash共同组成一个虚拟的sd卡。其中,nor flash仅仅负责提供数据的存储;sd fakex是一个verilog模块,负责对sd总线的命令进行解析和响应,并在sd-host请求数据时,从nor flash中读取数据并传给sd host,即fpga通过sdio将数据传给智能芯片,完成应用程序上注更新。

38.s4、限流保护为防止ai智能模组在特殊环境中发生闩锁,对芯片的电源电压进行监测、当发现电流异常变大时立即对模组断电防止芯片损坏、达到保护ai智能模组的目的。电流监测如图8所示:采用2路关键电流监测方法,2路关键电流包括1路智能芯片总输入5v电流和1路ddr 1.1v电流;一方面如果选择监测所有支路电流的话,需要的采样器件电路较多,占用较多的电路板面积,导致ai智能模组尺寸变大,同时采集通道过多也会给fpga监测电路带来困难;另一方面其余支路的电流较小,测量准确度难以保证,阈值难以确定,很小的波动可能会导致测量值大于阈值,造成智能芯片一直断电重启。所以,最终选择监测2路关键电流来进行限流控制。

39.2路关键电流可通过外部主控fpga adc进行监测。通过后续单粒子试验,测量出智能芯片出现单粒子锁定时2路关键电流的阈值,并在主控fpga程序中按照试验得出的电流阈值进行限流控制,当超出设定的阈值时迅速切断输入电源,保护ai智能模组不受损坏。主控fpga限流控制逻辑如图9所示。

40.首先,主控fpga判断智能芯片的总输入电流,如果总输入电流大于阈值,则主控fpga控制智能芯片断电重启;如果总输入电流小于阈值,则进一步判断第二路电流是否大

于阈值,如果电流大于阈值,则主控fpga控制智能芯片断电重启,如果电流均小于阈值,则认为智能芯片未出现单粒子锁定现象。

41.s5、重启指令为避免ai智能模组的发生意外情况,在指令设计时单独设计重启指令,可通过指令控制ai智能模组的加断电,外部fpga可根据需要对ai智能模组进行加断电。

42.s6、软看门狗ai智能模组周期性向fpga发送状态标志信息,使得fpga能够及时获取智能芯片状态信息,如长时间未接收到智能芯片状态标志信息,则对ai智能模组进行重启操作。

43.上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明主要技术方案的精神实质所做的修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。