1.本发明涉及一种栅极驱动电路以及显示面板,特别涉及一种能够减少所占用空间的栅极驱动电路以及显示面板。

背景技术:

2.一般而言,显示面板中的栅极驱动电路输出发光信号来驱动像素。同时,发光信号会配合重置信号来一起使像素发光或不发光。然而,目前用来产生重置信号的电路与栅极驱动电路分别受控于不同的控制信号。因此当设置多个像素来平衡变异的发光效率时,也需要设置多个控制电路来对应控制重置信号以及发光信号,而使显示面板的可配置电路空间变少且不利于零边框设计的显示面板。

技术实现要素:

3.本发明实施例提供一种栅极驱动电路,能够增加可配置于显示面板上的电路空间。

4.本发明实施例的栅极驱动电路具有多级移位暂存电路。第n级的移位暂存电路包括发光信号产生电路、发光信号控制电路、重置信号产生电路以及重置信号控制电路。发光信号产生电路具有第一节点输出发光信号至像素阵列。在第一发光阶段至第二发光阶段的期间内,发光信号产生电路致能发光信号。发光信号控制电路耦接于第一节点。在第一重置阶段至第二重置阶段的期间内,发光信号控制电路维持发光信号的电压电平为禁能的电压电平。重置信号产生电路耦接于第一节点。在第一重置阶段期间内,重置信号产生电路反应于发光信号来产生被致能的重置信号。重置信号控制电路耦接于发光信号控制电路以及重置信号产生电路。在第二重置阶段期间内,重置信号控制电路反应于发光信号来使重置信号被禁能。

5.本发明实施例另提供一种显示面板。显示面板包括像素阵列以及上述实施例的栅极驱动电路。栅极驱动电路耦接于像素阵列。

6.基于上述,本发明实施例的栅极驱动电路及显示面板是依据发光信号来产生重置信号。如此一来,用来产生发光信号的电路以及用来产生重置信号的电路被整合在一起,栅极驱动电路及显示面板不需要另外设置控制电路来产生重置信号,以减少栅极驱动电路本身所占用的电路空间而增加显示面板上可配置的电路空间。

7.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合说明书附图作详细说明如下。

附图说明

8.图1a是依据本发明一实施例所示出的显示面板的方框图。

9.图1b是依据本发明图1a实施例所示出的第n级的移位暂存电路的方框图。

10.图2是依据本发明图1b实施例所示出的第n级的移位暂存电路的电路图。

11.图3是依据本发明图2实施例所示出的第n级的移位暂存电路的动作示意图。

12.图4a至图4d是依据本发明图3实施例所示出的第n级的移位暂存电路的动作示意图。

13.图5是依据本发明另一实施例所示出的显示面板的方框图。

14.附图标记说明:

15.100、500:显示面板

16.110、210:发光信号产生电路

17.120、220:发光信号控制电路

18.130、230:重置信号产生电路

19.140、240:重置信号控制电路

20.c1、c2:电容器

21.ck:时钟信号

22.em(n 1):后级发光信号

23.em(n-1):前级发光信号

24.em(1)、em(2)、em(n):发光信号

25.gc:栅极驱动电路

26.gc_1、gc_2、gc_n:移位暂存电路

27.nd1、nd2、nd3、nd4:节点

28.p(n):第一控制信号

29.p(n 1):后级第一控制信号

30.p(n-1):前级第一控制信号

31.pem1、pem2、prt1、prt2:期间

32.pxl:像素阵列

33.pxl_1、pxl_2:子像素阵列

34.q(n):第二控制信号

35.r:电阻器

36.rst(1)、rst(2)、rst(n):重置信号

37.t1、t2、t3、t4、t5、t6、t7、t8、t9、t10、t11、t12、t13:晶体管

38.vgh1、vph:禁能电压电平

39.vgl、vgh:电压信号

40.vgl1、vgl2、vpl:致能电压电平

具体实施方式

41.本发明的部分实施例接下来将会配合附图来详细描述,以下的描述所引用的元件符号,当不同附图出现相同的元件符号将视为相同或相似的元件。这些实施例只是本发明的一部分,并未公开所有本发明的可实施方式。更确切的说,这些实施例只是本发明的专利申请范围中的范例。

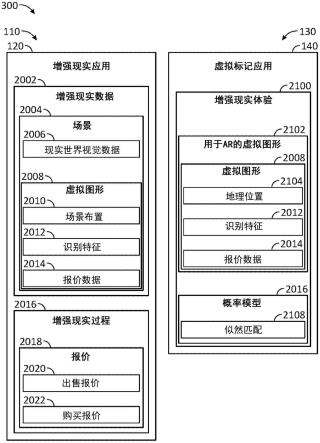

42.请参考图1a,图1a是依据本发明一实施例所示出的显示面板的方框图。在本实施例中,显示面板100包括像素阵列pxl以及栅极驱动电路gc。栅极驱动电路gc具有多级移位

暂存电路gc_1、gc_2、

…

、gc_n。多级移位暂存电路gc_1~gc_n按序耦接在一起。每一级的移位暂存电路gc_1~gc_n耦接于像素阵列pxl。具体来说,第1级的移位暂存电路gc_1输出第1级的发光信号em(1)以及重置信号rst(1)至像素阵列pxl中的第一像素列。第2级的移位暂存电路gc_2输出第2级的发光信号em(2)以及重置信号rst(2)至像素阵列pxl中的第二像素列,以此类推。第n级的移位暂存电路gc_n输出第n级的发光信号em(n)以及重置信号rst(n)至像素阵列pxl中对应的像素列。

43.在本实施例中,每一级的移位暂存电路gc_1~gc_n可具有相同的电路架构。

44.请一并参考图1b,图1b是依据本发明图1a实施例所示出的第n级的移位暂存电路的方框图。在本实施例中,第n级的移位暂存电路gc_n包括发光信号产生电路110、发光信号控制电路120、重置信号产生电路130以及重置信号控制电路140。发光信号产生电路110具有节点nd1。发光信号产生电路110的节点nd1输出发光信号em(n)至像素阵列pxl。在本实施例中,发光信号产生电路110用以在对应的发光阶段的期间中,致能发光信号em(n)以驱动像素阵列pxl。

45.发光信号控制电路120耦接于节点nd1。在本实施例中,在重置阶段的期间内,发光信号控制电路120使发光信号em(n)维持为禁能的电压电平。

46.重置信号产生电路130耦接于节点nd1。重置信号产生电路130具有输出端以输出重置信号rst(n)至像素阵列pxl。在本实施例中,在重置阶段期间的前期,重置信号产生电路130反应于发光信号em(n)来产生被致能的重置信号rst(n)以重置像素阵列pxl。

47.重置信号控制电路140耦接于发光信号控制电路120。重置信号控制电路140耦接于重置信号产生电路130的输出端。重置信号控制电路140具有输入端以接收发光信号em(n)。在本实施例中,在重置阶段期间的后期,重置信号控制电路140反应于发光信号em(n)来使重置信号rst(n)被禁能以停止重置像素阵列pxl。

48.在本实施例中,发光阶段发生在重置阶段之前。

49.在此值得一提的是,重置信号产生电路130以及重置信号控制电路140是依据发光信号em(n)来致能或禁能重置信号rst(n)。如此一来,第n级的移位暂存电路gc_n不需要设置额外的电路来产生重置信号rst(n)。因此,用来产生发光信号em(n)的电路以及用来产生重置信号rst(n)的电路被整合在相同的第n级的移位暂存电路gc_n中,以减少第n级的移位暂存电路gc_n所占用的电路空间而使显示面板100上可配置的电路空间被提升以利于设计零边框的显示面板100。

50.请参考图2,图2是依据本发明图1b实施例所示出的第n级的移位暂存电路的电路图。在本实施例中,第n级的移位暂存电路gc_n包括发光信号产生电路210、发光信号控制电路220、重置信号产生电路230以及重置信号控制电路240。

51.在本实施例中,重置信号产生电路230包括晶体管t1、t2以及电容器c1。晶体管t1的控制端耦接于节点nd1。晶体管t1受控于节点nd1上的信号(即,发光信号em(n))来进行开关操作。晶体管t1的第一端接收前级第一控制信号p(n-1)。晶体管t1的第二端与重置信号控制电路240耦接于节点nd2。晶体管t2的控制端耦接于节点nd2。晶体管t2受控于节点nd2上的信号来进行开关操作。晶体管t2的第一端接收时钟信号ck。晶体管t2的第二端输出重置信号rst(n)。电容器c1的第一端耦接于节点nd2。电容器c1的第二端耦接于晶体管t2的第二端。在本实施例中,电容器c1的第二端与晶体管t2的第二端作为重置信号产生电路230的

输出端以输出重置信号rst(n)。

52.在本实施例中,重置信号控制电路240包括晶体管t3、t4以及t5。晶体管t3的控制端接收后级第一控制信号p(n 1)。晶体管t3的第一端耦接于节点nd2。晶体管t3的第二端接收电压信号vgh。在本实施例中,电压信号vgh可以称为第一电压信号vgh。晶体管t4的控制端耦接于晶体管t3的控制端。晶体管t3、t4一同受控于后级第一控制信号p(n 1)来进行开关操作。晶体管t4的第一端耦接于晶体管t2的第二端以及电容器c1的第二端(即,重置信号产生电路230的输出端)。晶体管t4的第二端接收电压信号vgh。晶体管t5的控制端接收发光信号em(n)。晶体管t5受控于发光信号em(n)来进行开关操作。在本实施例中,晶体管t5的控制端作为重置信号控制电路240的输入端。晶体管t5的第一端耦接于晶体管t2的第二端以及电容器c1的第二端。晶体管t5的第二端接收电压信号vgh。

53.在本实施例中,发光信号产生电路210包括晶体管t6、t7以及电容器c2。晶体管t6的控制端接收时钟信号ck。晶体管t6受控于时钟信号ck来进行开关操作。晶体管t6的第一端接收前级发光信号em(n-1)。晶体管t6的第二端耦接于节点nd3。电容器c2的第一端接收后级发光信号em(n 1)。电容器c2的第二端耦接于节点nd3。晶体管t7的控制端耦接于节点nd3。晶体管t7受控于节点nd3上的信号(即,第二控制信号q(n))来进行开关操作。晶体管t7的第一端接收电压信号vgl。在本实施例中,电压信号vgl可以称为第二电压信号vgl。晶体管t7的第二端耦接于节点nd1。在本实施例中,晶体管t7的第二端作为发光信号产生电路210的输出端以输出发光信号em(n)。

54.在本实施例中,发光信号控制电路220包括晶体管t8、t9、t10、t11、t12、t13以及电阻器r。晶体管t8的控制端耦接于晶体管t8的第一端。晶体管t8的控制端及第一端接收时钟信号ck。晶体管t8耦接成二极管的组态,并接收时钟信号ck。晶体管t9的控制端接收前级发光信号em(n-1)。晶体管t9受控于前级发光信号em(n-1)来进行开关操作。晶体管t9的第一端耦接于晶体管t8的第二端。晶体管t9的第二端接收电压信号vgh。晶体管t10的控制端耦接于晶体管t8的第二端以及晶体管t9的第一端。晶体管t10的第一端耦接于晶体管t8的控制端以及第一端。晶体管t10的第二端耦接于电阻器r的第一端。电阻器r的第二端耦接于节点nd4。晶体管t11的控制端接收第二控制信号q(n)。晶体管t11受控于第二控制信号q(n)来进行开关操作。晶体管t11的第一端耦接于节点nd4。晶体管t11的第二端接收电压信号vgh。晶体管t12的控制端耦接于节点nd4。晶体管t12的第一端耦接于节点nd3。晶体管t12的第二端接收电压信号vgh。晶体管t13的控制端耦接于晶体管t12的控制端(即,节点nd4)。晶体管t12、t13一同受控于节点nd4上的信号(即,第一控制信号p(n))来进行开关操作。晶体管t13的第一端耦接于节点nd1。晶体管t13的第二端接收电压信号vgh。

55.在本实施例中,电压信号vgh、vgl为不同的定电压信号。在本实施例中,电压信号vgh具有被禁能的电压电平以禁能晶体管t1~t13中任一者。电压信号vgl具有被致能的电压电平以致能晶体管t1~t13中任一者。电压信号vgh可具有相对高的电压电平,电压信号vgl则可具有相对低的电压电平。

56.请参考图3以及图4a至图4d,图3是依据本发明图2实施例所示出的第n级的移位暂存电路的动作示意图。图4a至图4d是依据本发明图3实施例所示出的第n级的移位暂存电路的动作示意图。在图3中,横轴为第n级的移位暂存电路gc_n的操作时间,纵轴为电压值。

57.关于第n级的移位暂存电路gc_n在第一发光阶段的期间pem1内的操作细节,请同

时参照图3以及图4a。在第一发光阶段期间pem1内,发光信号em(n)具有致能电压电平vgl2。在本实施例中,致能电压电平vgl2如以下公式(1)所示:

58.vgl2=vgl1 2

×

|vth|

……

公式(1)

59.在公式(1)中,vgl1表示为电压信号vgl的电压电平(即,致能电压电平vgl1)。vth表示为晶体管t1~t13中任一者的阈值电压电平。在本实施例中,电压信号vgh具有禁能电压电平vgh1。

60.被致能的发光信号em(n)导通晶体管t1、t5。被导通的晶体管t1输出前级第一控制信号p(n-1)至晶体管t2的控制端。前级第一控制信号p(n-1)具有禁能电压电平vph。被禁能的前级第一控制信号p(n-1)关断晶体管t2。后级第一控制信号p(n 1)具有致能电压电平vpl。被致能的后级第一控制信号p(n 1)导通晶体管t3、t4。被导通的晶体管t3、t4分别将电容器c1两端上的信号拉至电压信号vgh(即,禁能电压电平vgh1)以使重置信号rst(n)被禁能。

61.在另一方面,在第一发光阶段的期间pem1内,前级发光信号em(n-1)具有致能电压电平vgl1。被致能的前级发光信号em(n-1)导通晶体管t9。被导通的晶体管t9将晶体管t10的控制端上的信号拉至电压信号vgh(即,禁能电压电平vgh1)以关断晶体管t10。时钟信号ck具有致能电压电平vgl1。时钟信号ck可使晶体管t6、t8被导通。被导通的晶体管t6将节点nd3上的第二控制信号q(n)拉至被致能的前级发光信号em(n-1)(即,致能电压电平vgl1)以导通晶体管t7。被致能的第二控制信号q(n)导通晶体管t11。被导通的晶体管t11将节点nd4上的第一控制信号p(n)拉至电压信号vgh(即,禁能电压电平vgh1)以关断晶体管t12、t13。被导通的晶体管t7将发光信号em(n)拉至电压信号vgl(即,致能电压电平vgl1)而输出被致能的发光信号em(n)。

62.关于第n级的移位暂存电路gc_n在第二发光阶段的期间pem2内的操作细节,请同时参照图3以及图4b。在第二发光阶段pem2的期间内,后级第一控制信号p(n 1)具有禁能电压电平vph。被禁能的后级第一控制信号p(n 1)关断晶体管t3、t4。发光信号em(n)具有致能电压电平vgl1。被致能的发光信号em(n)导通晶体管t1、t5。被导通的晶体管t1输出前级第一控制信号p(n-1)至节点nd2。前级第一控制信号p(n-1)具有致能电压电平vpl。被致能的前级第一控制信号p(n-1)导通晶体管t2。时钟信号ck具有禁能电压电平vgh1以使被导通的晶体管t2输出被禁能的重置信号rst(n)。

63.在另一方面,在第二发光阶段的期间pem2内,前级发光信号em(n-1)具有禁能电压电平vgh1。被禁能的前级发光信号em(n-1)关断晶体管t9。晶体管t10则维持被关断。时钟信号ck具有禁能电压电平vgh1。时钟信号ck可使晶体管t6、t8被关断。被关断的晶体管t6使节点nd3浮接。如此一来,电容器c2可将后级发光信号em(n 1)的变化耦合至节点nd3来改变节点nd3上的信号。此时,后级发光信号em(n 1)具有致能电压电平vgl2。通过电容器c2,被致能的后级发光信号em(n 1)可拉低节点nd3上的第二控制信号q(n)以导通晶体管t7。被致能的第二控制信号q(n)导通晶体管t11。被导通的晶体管t11将节点nd4上的第一控制信号p(n)拉至电压信号vgh(即,禁能电压电平vgh1)以关断晶体管t12、t13。被导通的晶体管t7将发光信号em(n)拉至电压信号vgl(即,致能电压电平vgl1)以输出被致能的发光信号em(n)。

64.关于第n级的移位暂存电路gc_n在第一重置阶段的期间prt1内的操作细节,请同时参照图3以及图4c。在第一重置阶段的期间prt1的期间内,发光信号em(n)具有禁能电压

电平vgh1。被禁能的发光信号em(n)关断晶体管t1、t5。后级第一控制信号p(n 1)具有禁能电压电平vph。被禁能的后级第一控制信号p(n 1)关断晶体管t3、t4。被关断的晶体管t1、t3使节点nd2浮接。如此一来,电容器c1可将重置信号rst(n)的变化耦合至节点nd2来改变节点nd2上的信号。此时,重置信号rst(n)可具有致能电压电平vgl1。被致能的重置信号rst(n)可使晶体管t2被导通。此时,时钟信号ck具有致能电压电平vgl1则可使被导通的晶体管t2输出被致能的重置信号rst(n)。

65.在另一方面,在第一重置阶段的期间prt1的期间内,前级发光信号em(n-1)具有禁能电压电平vgh1。被禁能的前级发光信号em(n-1)可使晶体管t9被关断。此时,时钟信号ck具有致能电压电平vgl1。时钟信号ck可使晶体管t6、t8被导通。被导通的晶体管t6将节点nd3上的第二控制信号q(n)拉至前级发光信号em(n-1)(即,禁能电压电平vgh1)并借此关断晶体管t7、t11。被导通的晶体管t8则将晶体管t10的控制端上的信号拉至时钟信号ck(即,致能电压电平vgl1)以导通晶体管t10。被导通的晶体管t10将节点nd4上的第一控制信号p(n)拉至时钟信号ck以导通晶体管t12、t13。被导通的晶体管t12将节点nd3上的第二控制信号q(n)拉至电压信号vgh(即,禁能电压电平vgh1)以使节点nd3上的第二控制信号q(n)维持在禁能电压电平vgh1。被导通的晶体管t13将节点nd1上的发光信号em(n)拉至电压信号vgh(即,禁能电压电平vgh1)以使发光信号em(n)被禁能。

66.关于第n级的移位暂存电路gc_n在第二重置阶段的期间prt2内的操作细节,请同时参照图3以及图4d。在第二重置阶段的期间prt2内,发光信号em(n)具有禁能电压电平vgh1。被禁能的发光信号em(n)关断晶体管t1、t5。后级第一控制信号p(n 1)具有致能电压电平vpl。被致能的后级第一控制信号p(n 1)导通晶体管t3、t4。被导通的晶体管t3、t4分别将电容器c1两端上的信号拉至电压信号vgh(即,禁能电压电平vgh1)以关断晶体管t2并使重置信号rst(n)被禁能。

67.在另一方面,在第二重置阶段的期间prt2内,前级发光信号em(n-1)具有禁能电压电平vgh1。被禁能的前级发光信号em(n-1)关断晶体管t9。时钟信号ck具有禁能电压电平vgh1。此时,时钟信号ck可使晶体管t6、t8被关断。晶体管t10则维持被关断。节点nd4上的第一控制信号p(n)维持为前一个期间prt1的信号(即,具有致能电压电平vgl1的时钟信号ck),并使晶体管t12、t13维持被导通。被导通的晶体管t12将节点nd3上的第二控制信号q(n)拉至电压信号vgh(即,禁能电压电平vgh1)以使节点nd3上的信号维持在禁能电压电平vgh1以关断晶体管t7、t11。被导通的晶体管t13将节点nd1上的发光信号em(n)拉至电压信号vgh(即,禁能电压电平vgh1)以使发光信号em(n)被禁能。

68.在本实施例中,晶体管t1~t13是以p型金属氧化物半导体场效晶体管(p-type metal-oxide-semiconductor field-effect transistor,pmosfet)来被实现。在其他实施例中,晶体管t1~t13是以n型金属氧化物半导体场效晶体管(nmosfet)来被实现。在其他实施例中信号反向于本实施例中对应的信号。

69.请参考图5,图5是依据本发明另一实施例所示出的显示面板的方框图。在本实施例中,显示面板500包括像素阵列pxl以及栅极驱动电路gc。像素阵列pxl包括子像素阵列pxl_1、pxl_2。在俯视图中,栅极驱动电路gc设置于子像素阵列pxl_1、pxl_2之间。关于栅极驱动电路gc的实施细节,在前述的实施例中已有详细的说明,在此恕不多重述。

70.综上所述,本发明实施例的栅极驱动电路及显示面板用来产生发光信号的电路以

及用来产生重置信号的电路被整合在相同的移位暂存电路中。此外,栅极驱动电路及显示面板能够依据发光信号来产生重置信号。如此一来,栅极驱动电路及显示面板能够省去额外用来控制重置信号的电路。因此每一级的移位暂存电路具有整合性的电路架构,以增加显示面板上可配置的电路空间而助于设计零边框的显示面板。在部分实施例中,栅极驱动电路是设置于相邻的子像素阵列之间。

71.虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的构思和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。