1.本发明是有关于一种投影技术,且特别是有关于一种投影装置与其梯形校正方法。

背景技术:

2.随着科技的进步,各式各样的投影装置已广泛的被应用于各种场合,如简报、演讲、戏院、视听教学、互动式教学与家庭剧院组等等。投影装置为一种用以产生投影画面的显示装置。投影装置的成像原理是将照明系统所产生的照明光束通过成像器件转换成图像光束,再将图像光束通过投影镜头投射到投影表面或墙面上,以形成投影画面。

3.需说明的是,当投影装置的镜头光轴不与投影表面或墙面垂直(perpendicular)时,投影表面或墙面上的投影画面将具有梯形失真(keystone distortion)的现象,这会降低投影质量。也就是说,投影装置的摆设必须使其镜头光轴垂直于投影表面,则所投放出来的投影画面才不会有扭曲现象。用户可自行手动调整投影装置的摆放位置与摆放方式,但可能受到环境限制而无法将投影画面调整至理想状态。为了解决上述问题,在投影装置进行投影之前,可利用投影装置内部的图像处理芯片执行图像预变形处理来实现梯形校正。目前,可透过图形处理单元(gpu)依据透射技术来完成梯形校正操作。然而,基于透射公式的转换原理,图形处理单元访问存储器时会有数据访问不连续的情况发生,导致gpu访问存储器的访问效率不佳,浪费许多存储器访问带宽。如何实现高效率与校正效果良好的梯形校正实为本领域技术人员关心的议题。

技术实现要素:

4.有鉴于此,本发明提供一种投影装置与其梯形校正方法,其可实现高效率且低成本的梯形校正,进而提升投影质量。

5.本发明实施例提供一种投影装置,其包括投影模块、存储器,以及显示处理电路。显示处理电路耦接投影模块并经由存储器总线耦接存储器,并包括图像处理电路、第一梯形校正电路、旋转电路、第二梯形校正电路,以及视频输出电路。图像处理电路产生经处理图帧。第一梯形校正电路基于水平缩放处理对经处理图帧进行第一梯形校正处理,而获取第一经校正图帧。旋转电路对第一经校正图帧进行旋转处理,以将经旋转图帧写入存储器。第二梯形校正电路自存储器读取经旋转图帧,并基于水平缩放处理对经旋转图帧进行第二梯形校正处理,而获取第二经校正图帧。视频输出电路将第二经校正图帧经由数据传输接口传送至投影模块。

6.本发明实施例提供一种梯形校正方法,适用于包括投影模块、存储器以及显示处理电路的投影装置。所述方法包括下列步骤:通过显示处理电路产生经处理图帧;通过显示处理电路基于水平缩放处理对经处理图帧进行第一梯形校正处理,而获取第一经校正图帧;通过显示处理电路对第一经校正图帧进行旋转处理,以将经旋转图帧写入所述存储器;通过显示处理电路自存储器读取经旋转图帧,并基于水平缩放处理对经旋转图帧进行第二

梯形校正处理,而获取第二经校正图帧;以及通过显示处理电路将第二经校正图帧经由数据传输接口传送至投影模块。

7.基于上述,于本发明的实施例中,显示处理电路先执行第一次的垂直梯形校正处理,接着进行旋转处理后写回存储器。接着,显示处理电路再从存储器读出经旋转图帧进行第二次的垂直梯形校正处理。经过两次的垂直梯形校正处理与一次的旋转处理,显示处理电路可实现投影装置的梯形校正功能。如此,可单纯透过水平线扫描的方式完成投影装置的梯形校正功能,从而节省内存空间的需求量。并且,显示处理电路访问储存器的访问效率高,不会浪费储存器的访问带宽。借此,可通过高效率与成本较低的图像缩放处理来实现梯性校正功能,从而提升投影画面质量。

8.为让本发明的上述特征和优点能更明显易懂,下文特举具体实施方式,并配合附图作详细说明如下。

附图说明

9.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

10.图1a是依照本发明一实施例所绘示的投影装置进行投影的示意图;

11.图1b是依照本发明一实施例的投影装置的示意图;

12.图2是依据本发明一实施例所绘示的梯形校正方法的流程图;

13.图3是依照本发明一实施例的投影装置的示意图;

14.图4为依据本发明一实施例所绘示的旋转电路与其执行旋转操作的示意图。

具体实施方式

15.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在图式和描述中用来表示相同或相似部分。

16.图1a是依照本发明一实施例的投影装置进行投影的示意图。图1b是依照本发明一实施例的投影装置的示意图。请参照图1a与图1b,投影装置100可将图像投影于投影表面s1上,其可以为液晶投影机(liquid crystal projector,lcp)、数字光学处理(digital light processing,dlp)投影机,或反射式液晶(liquid crystal on silicon,lcos)投影显示设备等等。在本实施例中,投影装置100可包括显示处理电路110、投影模块120,以及存储器130。投影模块120可包括光源模块、光机模块、镜头模块以及相关光学及电路控制组件等等。显示处理电路110耦接投影模块120并经由存储器总线耦接存储器130,具有图像处理功能与梯形校正功能。图像处理功能例如是图像缩放处理、图像去噪处理、图像强化处理、图像色调处理或图像叠合处理等等。梯形校正功能于后续实施例有详细说明。存储器130例如是dram,其可经由存储器总线连接至投影装置100的多个电路模块,使这些电路模块可将数据纪录于存储器130之中或从存储器130读取需要的数据。详细而言,显示处理电路110可自存储器130获取待投影图像数据,并对其进行图像处理与梯形校正处理而产生经校正图帧,然后再将经校正图帧提供给投影模块120进行投影。

17.可知的,若投影装置100未进行任何梯形校正处理,且投影装置100的镜头光轴不与投影表面s1垂直,则投影表面s1上的梯形失真画面kf1将具有投影画面变形且内容失真

的现象。基此,于本发明的实施例中,为了实现梯形校正功能,显示处理电路110可进行图像变形处理,致使投影装置100可于投影表面s1上显示出具有不失真内容且矩形的投影画面sf1。于一些实施例中,显示处理电路110是透过进行水平缩放处理来实现梯形校正处理。更详细而言,显示处理电路110是依据定位点r1~r4的坐标信息进行图像缩放处理。因此,当投影模块120投影经过图像缩放处理而产生的图像时,可于投影表面s1上定位点r1~r4所定义的矩形区域中显示出矩形投影画面sf1。

18.于一些实施例中,投影表面s1上的定位点r1~r4可由使用者标定。更具体而言,投影装置100可在未进行梯形校正处理的条件下进行投影,接着使用者可透过输入设备(例如遥控器或投影装置100上的按键)于梯形失真画面kf1的画面范围内标定出定位点r1~r4。又或者,于一些实施例中,投影表面s1上的定位点r1~r4可基于投影装置100自身的距离传感器或图像传感器的感测数据而决定。基于投影表面s1上的定位点r1~r4,投影装置100可以依据透射变换关系获取梯形校正处理所需的一个目标四边形边界,以基于此目标四边形边界进行图像缩放处理。

19.于一些实施例中,在投影装置100投影未经梯形校正处理且为矩形的一张测试图像时,投影表面s1上显示有非矩形的梯形失真画面kf1。于是,图像处理电路110可获取投影表面s1上投影画面kf1的四个顶点g1~g4的坐标,例如透过图像传感器进行拍摄而产生。接着,可依据四个顶点g1~g4的坐标计算出对应的透射变换矩阵。基此,取得投影表面s1上的定位点r1~r4之后,可依据前述透射变换矩阵以及定位点r1~r4的坐标反推导出投影图像坐标系统中由四个目标顶点形成的非矩形四边形边界。如此一来,通过将矩形图帧缩小为贴齐目标变形范围,投影装置100后续可投影出内容不失真的矩形投影画面sf1。

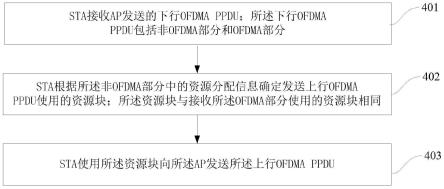

20.请参照图2,图2是依据本发明一实施例所绘示的梯形校正方法的流程图,而图2的方法流程可以由图1b的投影装置100实现。

21.首先,于步骤s201,通过显示处理电路110产生一经处理图帧。详细而言,显示处理电路110可自存储器130获取待投影图像数据,并对其进行图像处理而获取经处理图帧。上述图像处理例如是图像缩放处理、图像去噪处理、图像强化处理、图像色调处理或图像叠合处理等等。需说明的是,在不同的实施例中,显示处理电路110可从存储器130获取经过旋转处理或未经过旋转处理的图帧数据。在一些实施例中,经处理图帧可包括基于视频解码而产生的视频图帧、gpu所产生的图形数据或其组合。

22.于步骤s202,通过显示处理电路110基于水平缩放处理对经处理图帧进行第一梯形校正处理,而获取第一经校正图帧。详细而言,通过执行沿水平方向的水平缩放处理,显示处理电路110可对图像内容经过旋转处理或没有经过图像处理的经处理图帧进行垂直梯形校正处理,以将一个经处理图帧转换为第一梯形图像区块。第一经校正图帧可包括上述第一梯形图像区块与第一梯形图像区块两侧的背景区块。于一实施例中,上述的背景区块可为一黑色区块或其他背景色区块。于此,水平缩放处理为依据缩小倍率将一或多行输入像素转换为一行输出像素的处理,其中一行输入像素具有n个像素点而一行输出像素具有m个像素点,且n≧m。

23.于步骤s203,通过显示处理电路110对第一经校正图帧进行旋转处理,以将经旋转图帧写入存储器130。具体而言,显示处理电路110可经由存储器总线并按照一定顺序和存储位置将第一经校正图帧的像素写回存储器130,以对第一经校正图帧进行旋转处理或镜

像处理。像是,显示处理电路110可将第一经校正图的一行像素写入对应至一列像素的存储位置,以完成对第一经校正图帧进行90度的旋转处理,而将经旋转图帧写回存储器130。或者,于一些实施例中,可于显示处理电路110设置线缓存器,并按照一定顺序和存储位置将将第一经校正图的一行像素写入线缓存器,以对第一经校正图帧进行旋转处理或镜像处理。

24.于步骤s204,通过显示处理电路110自存储器130读取经旋转图帧,并基于水平缩放处理对经旋转图帧进行第二梯形校正处理,而获取第二经校正图帧。显示处理电路110经由存储器总线自存储器130读出经旋转图帧,并对其执行沿水平方向的水平缩放处理,以将一个经旋转图帧转换为第二梯形图像区块。第二经校正图帧可包括上述第二梯形图像区块与第二梯形图像区块两侧的背景区块。于一实施例中,上述的背景区块可为一黑色区块或其他背景色区块。由此可知,于步骤s202中所产生之具有投影内容的第一梯形图像区块可更被转换为具有投影内容且贴齐目标变形范围的非矩形图像区块。

25.值得一提的是,无论是将经旋转图帧写入存储器130或从存储器130读取经旋转图帧,基于存储读取请求或存储写入请求而通过存储器总线传输的像素数据都是必要的,因而不会浪费存储器130的访问带宽。

26.于步骤s205,通过显示处理电路110将第二经校正图帧经由数据传输接口传送至投影模块120。显示处理电路110可依据数据传输接口的数据传输接口标准将第二经校正图帧的像素数据提供给投影模块120,使投影模块120可投影出经过梯形校正处理的矩形投影画面。举例而言,数据传输接口可以用以传输符合prgb规格、srgb规格、bt601规格、bt656规格的第二经校正图帧。

27.以下将详细说明显示处理电路110实现梯形校正功能的实施细节。

28.请参照图3,图3是依照本发明一实施例的投影装置的示意图。除了显示处理电路110、投影模块120,以及存储器130,投影装置110可包括解码处理电路140与图形处理单元150。解码处理电路140与图形处理单元150分别经由存储器总线耦接存储器130。

29.解码处理电路140进行解码操作而产生原始图帧,解码处理电路140将原始图帧写入存储器130。解码处理电路140可应用hevc标准、avs2标准或其他类似的视频编解码标准,本发明对此不限制。于一些实施例中,解码处理电路140可接收经编码压缩处理而产生的码流,并依据前述视频压缩标准解码该码流以重构接收码流中的图帧数据。也就是说,解码处理电路140可重构出视频的原始图帧,使投影装置110可以投影视频内容。

30.图形处理单元150可由gpu来实现,其将图形数据写入存储器130。于一些实施例中,图形处理单元150可依据实际需求产生图形数据,像是投影装置100的osd选单、其他使用者操作选单或其他可叠加于投影画面上的图像数据等等。

31.显示处理电路110包括图像处理电路111、第一梯形校正电路112、旋转电路113、第二梯形校正电路114以及视频输出电路115。

32.于本实施例中,图像处理电路111自存储器130读取解码处理电路140产生的原始图帧与/或图形处理单元150产生的图形数据。图像处理电路111对原始图帧与图形数据进行图像后处理与图像叠合处理,从而产生经处理图帧。更详细而言,图像处理电路111可包括图像后处理模块111a与图像叠合模块111b。图像后处理模块111a可从自存储器130获取解码处理电路140产生的原始图帧与/或图形处理单元150产生的图形数据,并据以进行图

像后处理。上述图像后处理例如是图像缩放处理、图像去噪处理、图像强化处理、图像色调处理或图像叠合处理等等。然后,图像叠合模块111b可将经过图像后处理的原始图帧与/或图形数据进行图像叠合处理,以产生经处理图帧。

33.图像处理电路111将经处理图帧提供给第一梯形校正电路112。第一梯形校正电路112基于水平缩放处理对经处理图帧进行第一梯形校正处理,而获取第一经校正图帧。第一梯形校正处理包括至少一次的非线性插值滤波与一次水平方向的线性缩放滤波。于一些实施例中,第一经校正图帧可包括基于水平缩放处理而产生的梯形图像区块与背景区块的图帧数据。或者,于一些实施例中,第一经校正图帧可包括对具有梯形图像区块与背景区块的图帧数据进行非线性插值滤波之后而产生的图帧数据。

34.也就是说,于一些实施例中,第一梯形校正处理可包括垂直方向的非线性插值滤波、水平方向的线性缩放滤波,以及水平方向的非线性插值滤波。详细而言,为了避免梯形校正后所产生的投影画面出现失真或变形的情况,显示处理电路110内的梯形校正电路(即第一梯形校正电路112与第二梯形校正电路114)是依据非线性取线的原理来进行水平缩放处理。也就是说,在水平缩放处理的过程中,这些梯形校正电路是依循非线性对应规则撷取输入图帧中的输入像素来产生输出像素。举例而言,水平缩放处理所产生的第k行输出像素是基于第p行输出像素(或者第p行输出像素与第(p 1)行输入像素)而产生,其中k可不等于p。基于非线性取线原理执行水平缩放处理的情况下,因为显示处理电路110需要执行两次水平方向的线性缩放滤波,所以显示处理电路110也需要执行两次的非线性插值滤波。如此,可在水平方向的线性缩放滤波之前,依据非线性对应规则产生适合输入至线性缩放滤波器的图帧数据。

35.于一些实施例中,第一梯形校正电路112可透过垂直方向的非线性插值滤波与水平方向的线性缩放滤波将经处理图帧转换为一个梯形图像区块。然后,第一梯形校正电路112可对包括上述梯形图像区块与背景区块的图帧数据执行水平方向的非线性插值滤波,以产生第一经校正图帧。换言之,于一些实施例中,第一梯形校正电路112可负责执行水平方向与垂直方向的非线性插值滤波,使后续的第二梯形校正电路114可免去执行垂直方向的非线性插值滤波的步骤而提升第二梯形校正电路114之内部存储器(未绘示)的访问效率。

36.旋转电路113对第一梯形校正电路112输出的第一经校正图帧进行旋转处理,以将经旋转图帧写入存储器130。如同前述,旋转电路113可按照一定顺序和存储位置将第一经校正图帧的像素经由存储器总线写回存储器130,以对第一经校正图帧进行旋转处理或镜像处理。需说明的是,旋转电路113可依据投影装置100的投影模式决定旋转处理的旋转角度。旋转角度例如是90度、180度或270度。投影模式包括正常投影模式、竖屏投影模式、倒装投影模式,以及背投投影模式。由此可知,显示处理电路110可在执行梯形校正处理的过程中一并完成基于投影模式的投影旋转处理或投影镜像处理。

37.详细而言,当投影装置110操作于正常投影模式(又可称为横屏投影模式)、倒装投影模式或背投投影模式,解码处理电路140对原始图帧进行旋转处理并将经旋转的原始图帧写入存储器130,图形处理单元150对图形数据进行旋转处理并将经旋转的图形数据写入存储器130。

38.更具体而言,当投影装置110操作于正常投影模式时,解码处理电路140与图形处

理单元150可分别对原始图帧与图形数据进行顺时钟方向90度的旋转处理。对应的,旋转电路113后续是进行逆时钟方向90度的旋转处理。当投影装置110操作于竖屏投影模式时,解码处理电路140与图形处理单元150无须原始图帧与图形数据进行旋转处理。当投影装置110操作于倒装投影模式时,解码处理电路140与图形处理单元150可分别对原始图帧与图形数据进行顺时钟方向270度的旋转处理。对应的,旋转电路113后续是进行顺时钟方向90度的旋转处理。当投影装置110操作于背投投影模式时,则可由旋转电路113对经旋转图帧进行镜像处理即可。

39.在旋转电路113将经旋转图帧写入存储器130之后,第二梯形校正电路114自存储器130读取经旋转图帧。并且,第二梯形校正电路114基于水平缩放处理对经旋转图帧进行第二梯形校正处理,而获取第二经校正图帧。于一些实施例中,若第一梯形校正电路112负责执行水平方向的非线性插值滤波与垂直方向的非线性插值滤波,第二梯形校正处理可包括水平方向的线性缩放滤波,且第二梯形校正电路114无须执行关于非线性曲线的非线性插值滤波。换言之,第二梯形校正电路114的内存需求量可小于第一梯形校正电路112的内存需求量。此外,相较于由第二梯形校正电路114自行执行垂直方向的非线性插值滤波,由第一梯形校正电路112在旋转操作前提前执行水平方向的非线性插值滤波可明显提升处理效率。原因在于,垂直方向的滤波处理所耗费的内存需求与效率皆大于水平方向的滤波处理所耗费的内存需求与效率。

40.最后,视频输出电路115可将第二梯形校正电路114输出的第二经校正图帧经由数据传输接口传送至投影模块120。

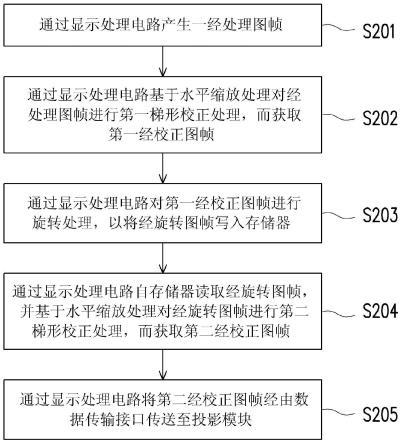

41.图4为依据本发明一实施例所绘示的旋转电路与其执行旋转操作的示意图。请参照图4,旋转电路113可包括线缓存器lb1。旋转电路113可依据第一经校正图帧cf1的多行像素产生经旋转图帧的多列像素,线缓存器lb1记录经旋转图帧的多列像素。如图4所示,旋转电路113可依据第一经校正图帧cf1的第一行像素41产生经旋转图帧rf1的第一列像素42,旋转电路113可依据第一经校正图帧cf1的第二行像素43产生经旋转图帧rf1的第二列像素44。依此类推。线缓存器lb1即用以记录经旋转图帧cf1的多列像素。举例而言,第1条线缓冲器用以记录经旋转图帧rf1的第一列像素42。之后,旋转电路113可透过一笔写入请求将线缓存器lb1中对应至同一行位置且对应至不同列位置的多个像素写入存储器130。

42.值得一提的是,于一些实施例中,线缓存器lb1的容量可依据存储器总线的位宽而决定。旋转电路113可将线缓冲器lb1内的多个像素经由存储器总线写入存储器130,旋转电路113可透过一笔写入请求将经旋转图帧rf1中位于相同行位置的多个像素写入存储器130。举例而言,假设基于存储器总线的位宽(假设等于128位(bits))的限制,旋转电路113可依据单一笔写入请求将128位(bits)的像素数据写入存储器130。若一个像素具有8位(bits),代表一笔写入请求可将16个像素的像素数据写入存储器130。在此情况下,线缓存器lb1可配置为用以记录经旋转图帧rf1的16列像素的16条线缓存器,每一条线缓存器用以记录经旋转图帧rf1的1列像素中的部份或全部。

43.于一些实施例中,旋转电路113可依据行写入格式将线缓冲器lb1内的像素写入存储器130。举例而言,旋转电路113可依据一笔写入请求同时将多条线缓存器所记录的像素写入存储器130,其中同一笔写入请求中的像素可为经旋转图帧rf1中位于相同行位置的多个像素。

44.此外,在配置线缓冲器lb1的情况下,于一些实施例中,旋转电路113可依据区块(tile)写入格式将线缓冲器lb1内的像素写入存储器130。举例而言,旋转电路113可基于区块(tile)写入格式而依据一笔写入请求同时将多条线缓存器所记录的像素写入存储器130,其中同一笔写入请求中的像素可为经旋转图帧rf1中位于不同行位置的多个像素。只需要该笔请求的突发长度(burst length)的长度大于1即可。像是,旋转电路113可先依据一笔写入请求而将经旋转图帧rf1中位于第一行且位于第1列至第16列的多个像素写入存储器130的一个区块(tile)里(写入地址记为a),如果该笔请求的突发长度为2,则可以随后将经旋转图帧中位于第二行且位于第1列至第16列的多个像素也写入存储器130的同一个区块(tile)里(且写入地址紧跟a之后)。同理,如果该笔请求的突发长度为3,则可以随后将经旋转图帧中位于第三行且位于第1列至第16列的多个像素写入存储器130的同一个区块(tile)里。基此,在一笔写入请求的突发长度可弹性配置为大于1的情况下,旋转电路113可使用更少的请求次数与单一笔写入请求所对应的更多的数据突发(data burst)将经旋转图帧rf1写入存储器130,因而可大幅提升旋转电路113访问存储器130的访问效率,且地址连续效率更高。

45.值得注意的是,在不同的实施例中,上述显示处理电路110的相关功能可以利用一般的编程语言(programming languages,例如c或c )、硬件描述语言(hardware description languages,例如verilog hdl或vhdl)或其他合适的编程语言来实现为软件、固件或硬件。可执行所述相关功能的软件(或韧体)可以被布置为任何已知的计算器可存取媒体(computer-accessible medias),例如磁带(magnetic tapes)、半导体(semiconductors)内存、磁盘(magnetic disks)或光盘(compact disks,例如cd-rom或dvd-rom)。所述软件(或固件)可以被存放在计算器的可存取媒体(例如内存)中,以便于由计算器的处理器来存取/执行所述软件(或固件)的编程码(programming codes),以执行所述相关功能。

46.综上所述,于本发明的实施例中,投影装置可透过进行高效率的水平缩放处理来实现梯形校正功能,以使观看者可从投影表面上观看到矩形且不失真的投影画面。此外,于显示处理电路访问存储器的过程中,并不会浪费访问带宽的现象发生,因而可大幅节省访问存储器的消耗带宽。并且,显示处理电路可一并完成梯形校正与关于投影模式的投影方向转换,提升处理效率。因此,可在实现高效率且低成本的梯形校正的情况下提升投影质量。

47.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。