1.本发明的技术领域是非易失性存储器的技术领域。本发明涉及一种集成非易失性存储器功能和选择性功能两者的器件。本发明还涉及该器件的读取方法。

背景技术:

2.对于即使当切断电压时也需要信息存储的应用,常规地使用在场效应晶体管的浮动栅上执行电荷存储的eeprom或flash类型的非易失性存储器。然而,这些存储器具有以下缺点:

[0003]-长写入时间(几微秒),

[0004]-有限的密度,因为晶体管尺寸的减小导致读取信号的减少,即,存储器点的两种状态之间的差异的下降,以及信息的保留持续时间的减少,

[0005]-有限数量的写入循环,因为由于在晶体管的栅氧化物中产生缺陷,信息的保留随着发生写入循环而减少,允许电子从浮动栅逸出。

[0006]

因此,这种类型的存储器不具有支持新技术,如scm存储器(“存储级存储器”)的开发所要求的特性,已经看到这些新技术显著的增长,特别地由于它们在增加计算机的性能同时仍减少其消耗的能力。

[0007]

最近,基于有源材料,如相变材料(pcram存储器或“相变ram”,也称为pcm“相变存储器”)、具有离子导电(cbram存储器或“导电桥接ram”)、具有金属氧化物(oxram存储器或“氧化物电阻ram”)、铁电体(feram存储器或“铁电体ram”)、磁性(mram存储器或“磁性ram”)、或具有自旋转移的磁性(sttram存储器或“自旋扭矩转移ram”),已经出现其他类型的可重写非易失性存储器。这些存储器是电阻类型的(即,它们可以具有对应于从电阻状态(“断开”状态)切换至较小电阻状态(“导电”状态)的至少两个状态“断开”或“导电”)。

[0008]

电阻存储器需要两个电极来运行。在pcram存储器的情况下,使用硫属元素化物材料,已知其无定形(电阻)相和其结晶(导电)相之间存在的电阻的显著对比。这种现象基于pcram相变存储器,其中,由于电脉冲,由焦耳效应引起相变,电脉冲的形状使得可以达到存储器内的特定温度分布。因此,pcram存储器包括基于硫属元素化物材料的有源区。pcram存储器的运行基于硫属元素化物材料的相变,该相变由其两个电极产生的特定电脉冲的作用下该材料的加热引起。在低电阻和热力学稳定的有序的结晶相与高电阻和热力学不稳定的无序的无定形相之间完成这种转变。

[0009]

在此上下文中,基于最成熟的非易失性电阻存储器技术的pcram电阻存储器代表用于支持scm存储器的开发的非常好的候选者。

[0010]

最近,通过集成彼此堆叠的几层存储器,并且使得可以增加同一芯片表面的存储器密度,已经给予了具有3d类型集成的系统的可能性的极大关注。该3d集成基于“交叉”类型(也由术语称为“交叉点”)的集成的使用。pcram电阻存储器特别地具有能够经由“交叉”类型的集成被高密度集成的重要性。

[0011]

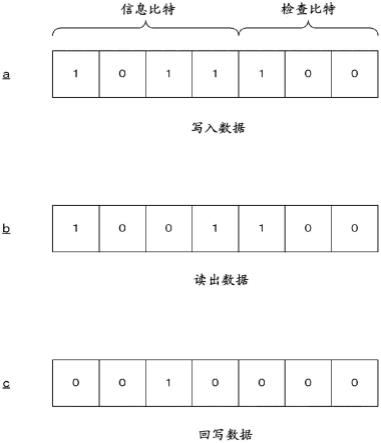

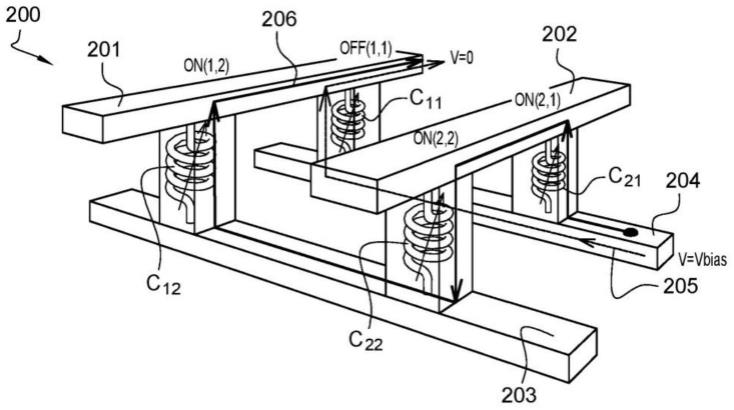

这种架构200在图1中示出,并且包括多条存取线201、202、203和204以及非易失性

可重写pcram类型的多个存储器单元(在此为四个单元c11、c21、c22和c12)。存取线由顶部平行位线201和202以及垂直于位线的底部字线203和204形成,基本单元c11、c21、c22和c12夹在位线201和202与字线203和204之间的相交处。因此,架构200形成其中通过选择正确的位线和正确的字线可以单独地寻址每个存储器单元的网络。

[0012]

然而,这种类型的架构确实具有某些缺点。因此,通过期望行和期望列的极化来执行单元的状态的读取阶段;然后可以观察穿过相邻单元的寄生漏电流。我们在这里假设:

[0013]-单元c11处于断开状态(高电阻状态);

[0014]-单元c21处于导电状态(低电阻状态);

[0015]-单元c22处于导电状态(低电阻状态);

[0016]-单元c12处于导电状态(低电阻状态)。

[0017]

读取单元c11的电阻状态涉及分别地极化位线201和字线204(在这两条线之间施加电位差vbias)。理论上,测量电流应仅根据虚线所示的箭头205流动。实际上,由于三个其他单元处于导电状态的事实,由箭头206表示的寄生漏电流(“潜通过”)穿过非电阻单元c21、c22和c12。该漏电流,特别是在待测量单元的相邻元件处于导电状态的不利情况下,可以干扰测量,直到防止待测量单元的导电状态与断开状态之间的区分。

[0018]

该问题的已知解决方案包括与单元中的每个串联地添加p/n结二极管(例如,具有si基极)207以起到选择器的作用。“二极管”类型的行为被定义为基于两个接入终端的器件的行为,具有高于电压v

th

的电压的非常低的电导率,并且当超过电压v

th

时具有高的电导率。每个存储器单元被称为1r,并且每个选择器被称为1s。这因此被称为存储器点1r/1s。图2中示出了这样的架构300。在图1和2中,共同的元件具有相同的附图标记,应理解的是,图2的单元c11、c21、c22和c12处于与图1的单元c11、c21、c22和c12相同的电阻状态。在这种情况下,由于二极管207是单极的,所以它们阻止寄生电流的通过,因此仅授权由位线201和字线204的极化引起的由箭头210表示的电流(在这两条线之间施加电位差vbias)。

[0019]

然而,如图2中所示的架构还引起特别地与以下事实相关联的某些困难:具有si基极的标准二极管不是最相关的解决方案,因为它们难以制造,它们在与电阻存储器的编程不兼容的“有源”状态下具有过大的串联电阻和低电流密度。由此,二极管在导电模式下保持有限的电流强度。因此,目前,对于给定的硅表面,不可能创建与存储器单元具有相同表面并且具有足够的通过电流i

on

(二极管的电流密度太低)以及同时具有相当低的漏电流i

off

的二极管。在使用与需要大量切换电流的pcram相变类型的单元串联的二极管的情况下,这种情况特别地导致严重的困难。

[0020]

这就是为何在过去的几年里已经研究过若干替代解决方案。在文献中,可以发现不同类型的选择器,如fast(“场辅助超线性阈值”)、miec(“混合离子电子导电”)和ots(“双向阈值切换”)。

[0021]

选择装置由两个电极和有源材料组成,其中这些电极被布置在该有源材料的任一侧上,并且使得可以向此有源材料施加电压。在ots型选择器的情况下,有源材料可以是硫属元素化物合金。图3中示出了选择器件的运行的基本原理。该器件在断开状态下是非常电阻性的。一旦大于阈值电压的电压施加到其上,电流快速地增加以达到装置的导电状态(低电阻状态)。一旦电流或电压减小到低于被称为“保持”或“保留”值的特定值,该器件就再次变为断开。因此,一旦达到阈值电压v

th

,选择器件的第一功能是阻断低电压电流(亚阈值)的

通过,并且允许强电流密度的通过。

[0022]

现在,交叉结构的主要问题是在存储器1r与选择器1s之间的电性能方面找到良好的折衷。为了能够与电阻存储器1r集成,选择器1s必须具有几种约束特异性。实际上,在选择器处于其“断开”状态时,其必须具有与存储器的尺寸接近的尺寸以及低漏电流i

off

,同时仍与存储器1r的存储特性兼容。

[0023]

为了进一步改善电阻存储器的集成密度,常规的解决方案是减小电阻存储器的有源材料与其底部电极之间的表面的尺寸,以便允许减小电阻存储器的编程电流。

[0024]

根据存储的另一种方法,文章“一种使用新型阈值切换,自整流硫属元素化物的器件的无存取晶体管(0t/1r)的非易失性电阻随机存取存储器(rram)(an access-transistor-free(0t/1r)non-volatile resistance random access memory(rram)using a novel threshold switching,self-rectifying chalcogenide device)”(yi-chou chen et al.,iedm 2003)描述了在器件中集成由硫属元素化物(ge2sb2te5被非常广泛地用于创建pcram存储器)制成的有源层,以具有不同的无定形体积的可能性,具有不同的电阻(即,如果无定形体积减小,则编程状态的电阻减小),但根据所使用的编程脉冲参数,尤其具有不同的阈值电压v

th

。在这篇文章中,提出了使用这个电特性,通过由于控制通过不同强度的电脉冲获得的无定形体积,而对其进行编程来将信息存储在由阈值电压v

th

形成的参数中。在专利申请us2004/0257848a1中还描述了这种特性,该专利申请描述了通过控制电脉冲的强度和持续时间,来调制阈值电压,而仅在其无定形相中使用相变存储器的可能性。

[0025]

然而,在文章“一种使用新型阈值切换,自整流硫属元素化物的器件的无存取晶体管(0t/1r)的非易失性电阻随机存取存储器(rram)(an access-transistor-free(0t/1r)non-volatile resistance random access memory(rram)using a novel threshold switching,self-rectifying chalcogenide device)”中描述的器件还具有约10-6

a的亚阈值电流,该亚阈值电流过高而不能在交叉阵列中没有选择器的情况下使用。此外,观察到,这些存储器的编程还未被很好地控制,并且编程脉冲持续时间必须非常短,以便防止材料的任何结晶。

技术实现要素:

[0026]

本发明通过提出一种非易失性存储器器件来提供对上文提及的问题的解决方案,该非易失性存储器器件被适配成集成到具有“交叉”型架构的器件中,并且使得可能克服与选择器串联的电阻存储器的使用约束。

[0027]

本发明的第一方面涉及选择性非易失性存储器器件,该选择性非易失性存储器器件包括:

[0028]-第一电极;

[0029]-第二电极;

[0030]-至少一个由有源材料制成的层,称为有源存储器层,布置在第一电极与第二电极之间;

[0031]

所述器件具有至少两个可编程存储器状态:

[0032]-与有源层的第一阈值电压v

th1

相关联的第一可编程非易失性存储器状态,所述器件在所述第一存储器状态中具有特征电压电流,使得一旦在第一和第二电极之间施加大于

或等于v

th1

的电压,所述器件就从高电阻状态切换到比高电阻状态低的电阻状态,并且所施加的电压严格地小于v

th1

时,所述器件返回到其高电阻状态,在所述存储器的高电阻状态下通过所述存储器的电流强度严格地小于10-7

a;

[0033]-与严格地大于第一阈值电压v

th1

的第二阈值电压v

th2

相关联的第二非易失性存储器状态,所述器件在所述第二存储器状态中具有特征电压电流,使得一旦在第一电极与第二电极之间施加大于或等于v

th2

的电压,所述器件就从高电阻状态切换到比高电阻状态低的电阻状态,并且所施加的电压严格地小于v

th2

时,所述器件返回到其高电阻状态,在所述存储器的高电阻状态下通过所述存储器的电流强度严格地小于10-7

a。

[0034]

根据本发明,有源层的材料由as2te3合金和ge3se7合金的混合物制成。

[0035]

由于本发明,提出了一种集成非易失性可重写存储器功能和选择性功能两者的器件。通过使用可以具有至少两个值v

th1

和v

th2

的可编程阈值电压来提供非易失性存储器功能:存储器状态由器件中的该编程阈值电压的值给出。在其他方面,与pcram存储器相反,根据本发明的非易失性存储器器件不是电阻存储器,因为存储器状态不依赖于器件的电阻状态。“选择性”功能由严格地小于10-7

a的亚阈值电流(即,当器件根据是否处于存储器状态v

th1

或v

th2

分别地经受严格地小于v

th1

或v

th2

的电压时,通过器件的电流)提供:这种亚阈值电流的值比得上由已知选择器提供的那些值。注意,选择性功能是易失性的,其方式为使得只要器件的端子处的电压根据是否其是处于存储器状态v

thl

还是v

th2

分别地在vthl或vth2下通过,器件就变得具有严格地小于10-7

a的强度的电流的高电阻性。

[0036]

因此,根据本发明的第一方面的器件可以被视为具有非易失性阈值切换(或“nvts”)的选择性器件。所选择的材料是通过as2te3和ge3se7合金的组合获得的硫属元素化物材料(即,含有至少一种硫属元素化物元素,如氧、硫、硒、碲或钋的化合物),其中as2te3导致“切换”类型的行为,并且ge3se7导致系统的间隙的增加,这使得可以降低漏电流。

[0037]

硫属元素化物材料将选择为在其无定形静态(断开状态)下具有非常高的电阻率,以及一旦经受大于其阈值电压的电压的强导电性,如所谓的“ots”材料,但是具有可能的阈值电压调制的特殊性。

[0038]

因此,该材料被有利地选择为在其运行期间不具有任何结晶。由于特定材料的选择,因此可以:

[0039]-保证非常大的亚阈值电阻,以便减少交叉类型的阵列中的漏电流;

[0040]-具有取决于所施加的脉冲的形状(特别地,根据脉冲的下降侧翼)的可编程阈值电压。

[0041]

注意,根据本发明的该第一方面,对应于阈值电压状态v

th1

的第一非易失性存储器状态可以通过施加大于v

th2

的电压脉冲而被编程,该电压脉冲具有预定的非零持续时间的预定下降侧翼,并且大于第二存储器状态的编程电压脉冲的下降侧翼的持续时间。因此,根据编程脉冲的下降侧翼的持续时间,将有利地使用的材料的电压阈值改变的行为。有趣的是观察到,当阅读专利申请us 2004/0257848 a1时,本领域的普通技术人员不会自然地朝向这样一种解决方案,在该专利申请中清楚地指出使用具有显著的下降侧翼的脉冲可以触发材料的结晶,并且因此触发运行中的损失。对于两个编程状态使用不同的下降侧翼持续时间,没有差别。此外,在本专利申请中描述的下降侧翼都是小于50ns,特别是为了防止结晶。这样的相变将涉及由于不同因素(如温度或控制电路的寄生效应)引起的信息的可能的

部分或全部损失。

[0042]

最后,令人感兴趣的是观察到,本专利申请中的最高阈值电压的编程是通过施加给定编程电流和大于所述最高电压阈值的电压脉冲获得的(这背离根据本发明的第一方面的器件,其中,最高阈值电压v

th2

的编程是通过施加包括在v

th1

与v

th2

之间、并且因此小于v

th2

的电压脉冲获得的)。

[0043]

除了在前述段落中刚刚已经提及的特征之外,根据本发明的一个方面的器件可以具有以下各项中的一个或多个附加特征,这些特征是单独地考虑或根据任何技术上可允许的组合:

[0044]-混合物包含按重量计大于15%,并且严格地小于60%百分比的as2te3合金。

[0045]-混合物包含按重量计实质上等于20%百分比的as2te3合金。

[0046]-根据第一阈值电压v

th1

与第二阈值电压

vth2

之间期望的差值,选择有源层的厚度。

[0047]-有源层由as2te3合金和ge3se7合金的混合物制成的单个有源层构成。

[0048]-有源层由层的堆叠构成,其中,每个层具有小于或等于5nm的厚度。这些层一起形成由as2te3合金和ge3se7合金的混合物构成的堆叠,用于形成有源层。

[0049]

本发明的第二方面涉及一种用于在根据本发明的器件中写入第二存储器状态的方法,通过施加给定编程电流和包括在v

th1

与v

th2

之间的具有预定持续时间的下降侧翼的电流脉冲来编程所述第二非易失性存储器状态。

[0050]

本发明的第三方面涉及一种用于在根据本发明的器件中写入第一存储器状态的方法,通过施加大于v

th2

的电压脉冲来编程第一非易失性存储器状态,该电压脉冲具有预定的非零持续时间的预定下降侧翼,并且大于通过根据本发明的第二方面的方法写入的第二存储器状态的编程电压脉冲的下降侧翼的持续时间。

[0051]

有利地,大于v

th2

的电压脉冲的预定的非零持续时间的下降侧翼具有优选地包括在106v/s与108v/s之间的斜率。

[0052]

本发明的第四方面涉及一种用于读取根据本发明的器件的存储器状态的方法,该方法包括以下步骤:施加严格地大于v

th1

且严格地小于v

th2

的电压脉冲,该电压脉冲具有预定的非零持续时间的预定下降侧翼,并且大于通过根据本发明的第二方面的用于写入的方法所写入的第二存储器状态的编程电压脉冲的下降侧翼的持续时间。

[0053]

当阅读以下描述时和当检查附图时,将更好地理解本发明及其不同应用。

附图说明

[0054]

这些图是为了信息的目的而示出的,并且决不限制本发明。

[0055]

图1示出了根据现有技术的多个存储器单元的第一寻址架构;

[0056]

图2示出了根据现有技术的多个存储器单元的第二寻址架构;

[0057]

图3示出了解释选择性器件的运行原理的图表;

[0058]

图4示出了根据本发明的第一方面的器件的图示;

[0059]

图5示出了根据在器件的底部电极与顶部电极之间施加的电压,通过图4的器件的对数标度上的电流的变化;

[0060]

图6示意性地示出了使得可以使用图4的器件作为存储器的编程和读取脉冲的实施例;

[0061]

图7示出根据图4的器件的有源层的三种材料的编程脉冲的下降侧翼的斜率,阈值电压的行为;

[0062]

图8示出了根据图4的器件的有源层的三种材料的编程脉冲的下降侧翼的斜率,亚阈值电流的行为;

[0063]

图9示出了图4的器件的编程脉冲的下降侧翼“斜坡率”的斜率;

[0064]

图10示出了根据用于有源层的四个不同厚度的电压阈值,用于图4的器件的有源层的材料的实施例的电压阈值的变化。

[0065]

图11示出了编程脉冲的另一实施例。

具体实施方式

[0066]

除非另外提及,出现在不同图上的相同元件具有唯一的附图标记。

[0067]

图1已经参考现有技术进行了描述。

[0068]

图2已经参考现有技术进行了描述。

[0069]

图3已经参照现有技术进行了描述。

[0070]

图4示出了根据本发明的第一方面的器件1的图示。

[0071]

图5示出了根据在器件的底部电极与顶部电极之间施加的电压,通过图4的器件的对数标度上的电流的变化;

[0072]

图6示意性地示出了使得可以使用图4的器件作为存储器的编程和读取脉冲的实施例;

[0073]

图7示出根据图4的器件的有源层的三种材料的编程脉冲的下降侧翼的斜率,阈值电压的行为;

[0074]

图8示出了根据图4的器件的有源层的三种材料的编程脉冲的下降侧翼的斜率,亚阈值电流的行为;

[0075]

图9示出了图4的器件的编程脉冲的下降侧翼“斜坡率”的斜率;

[0076]

图10示出了根据用于有源层的四个不同厚度的电压阈值,用于图4的器件的有源层的材料的实施例的电压阈值的变化。

[0077]

图11示出了编程脉冲的另一实施例。

[0078]

如下文应当看到的,器件1是用作非易失性存储器和选择器的器件,其中,这两个功能被集成到同一器件1中,该器件包括:

[0079]-第一电极或底部电极3;

[0080]-第二电极或顶部电极4;

[0081]-由有源材料制成的层2,称为有源存储层,设置在第一电极与第二电极之间。

[0082]

器件的顶部电极被定义为位于此器件上方的电极,并且器件的底部电极被定义为位于此器件下方的电极,这些电极位于器件的每一侧上。当然,形容词“顶部”和“底部”在此相对于包括顶部电极、器件和底部电极的组件的定向到这样的程度:当翻转该组件时,先前被认定为顶部的电极变成底部电极,并且先前被认定为底部的电极变成顶部电极。同样,电极的垂直布置也可设置有在两个电极3和4之间布置的有源层2。

[0083]

底部3和顶部4电极各自实施导电材料,该导电材料对于两个电极3和4可以是不同的或相同的。这样的导电材料例如是tin、tan、w、tiwn、tisin或wn。

[0084]

例如,有源层2是通过混合(例如通过共溅射)as2te3和ge3se7合金实施的硫属元素化物类型的有源材料的层。有利地,形成有源材料的混合物包含按重量计大于15%且严格地小于60%百分比的as2te3。作为优选实施例,这里形成有源材料的混合物包含按重量计20%as2te3。共溅射的原理是在一个或多个溅射靶(在此为as2te3和ge3se7靶)的表面上使用等离子体的能量,逐一拉出这个或这些靶的材料的原子并将它们沉积在例如,底部电极3上。

[0085]

选择有源层2的材料以允许器件1在其无定形静止状态(所谓的“断开”状态)下具有非常强的电阻率,以及一旦经受大于阈值电压的电压就具有强的导电性。所选择的材料的特殊性允许对该阈值电压的调制,该阈值电压可以具有若干值(至少两个阈值电压v

th1

和v

th2

),这由于对电编程脉冲的下降侧翼的控制,其在下文中将进一步覆盖。在图5中示出了这两个阈值电压v

th1

和v

th2

的存在(应理解的是,完全可以考虑具有特定的编程的多于两个的阈值电压),该图示出了对于通过编程器件1获得的两个阈值电压v

th1

和v

th2

,根据施加在底部3和顶部4电极之间的电压,通过器件1(在对数标度上)的电流的变化。注意,在此处描述的实施方式中,第二阈值电压v

th2

严格地大于第一阈值电压v

th1

。

[0086]

因此,当器件1具有阈值电压v

th1

时,只要在器件1的端子处的电压严格地小于v

th1

,通过该器件的电流的强度(由i

leak

或亚阈值电流指定)非常低(因此,该器件的电阻性是非常强的)。一旦达到阈值电压v

th1

,电流快速地增加,并且器件1变得非常导电。一旦电压再次降低到v

thl

以下,器件1再次变成低导体。注意,有源层的材料在此被选择成使得亚阈值电流具有特别地低的强度;在其他方面,亚阈值电流的强度严格地小于10-7

a。

[0087]

当器件1具有严格地大于第一阈值电压v

th1

的第二阈值电压v

th2

时,器件的行为是类似的。在这种情况下,只要在器件1的端子处的电压严格地小于v

th2

,通过它的电流(i

leak

或亚阈值电流)的强度非常低。一旦达到阈值电压v

th2

,电流快速地增加,并且器件1变得非常导电。一旦电压再次降低到v

th2

以下,器件1再次变成低导体。在此再次,亚阈值电流的强度严格地小于10-7

a。

[0088]

被选择用于有源层2的材料的特殊性将能够根据器件1的电编程脉冲的类型提供阈值电压v

th

的调制。在其他方面,器件1具有由于有源层的材料引起的至少两个不同的电压阈值(第一阈值电压v

th1

和第二阈值电压v

th2

),该电压阈值将根据电编程脉冲的形状,并且特别地根据电编程脉冲的下降侧翼而不同地反应。以下将更详细地解释该运行。

[0089]

应理解的是,只要与pcram或cbram类型的电阻存储器相反,存储器状态就不取决于器件1的电阻率,而是取决于阈值电压的值v

th1

或v

th2

,其可以通过非易失性方式编程和写入在器件1中。因此,根据本发明的器件1可以由术语“nvts”或“非易失性阈值切换”(具有非易失性切换阈值的器件)指定。存储器信息在这里由阈值电压的值给出。

[0090]

此外,具有严格地小于10-7

a的亚阈值电流的强度和器件1的电阻率的易失性行为(即,根据电压是高于还是低于阈值电压,器件相应地切换至导电状态或电阻状态)使得可以具有还充当选择器的器件1;在交叉型的配置中,在器件的端子处不存在大于阈值电压的极化电压的情况下,通过器件的电流非常低,并且使得可以防止“潜通过”型的寄生漏电流。

[0091]

因此,器件1是非易失性存储器器件(具有作为存储器信息的阈值电压)和选择器(具有非常低的漏电流)两者。

[0092]

在下文中将解释参见图6对根据本发明的器件1的编程和读取。图6示出了根据时

间的编程电压脉冲(三个脉冲100、101和102)和读取的实施例,使得可以使用根据本发明的器件1作为存储器。注意,编程电压和读取电压可以在极性上反转,因为根据本发明的器件对具有反转符号的脉冲同样做出响应。因此,当参考具有小于第二阈值电压v

th2

的强度的强度的第一电压v

th1

时,必须理解的是,当两个电压为负时,比较这两个电压的绝对值。

[0093]

脉冲100(称为reset)是使器件1达到由第二阈值电压v

th2

表示的编程状态的编程脉冲。该脉冲具有包括在第一阈值电压v

th1

与第二阈值电压v

th2

之间的电压强度。

[0094]

根据第一配置,器件1已经处在由第二阈值电压v

th2

表示的编程状态中。在这种情况下,器件1将保持在该状态下。实际上,为了发生阈值电压的改变,足够的编程电流必须在器件1中流动。在此,根据图5,在电压值保持在第二阈值电压v

th2

以下的情况下,不会发生切换。此外,这种特性使得可以保持器件1的耐久性。然而,根据第二配置,如果器件处在由阈值电压v

th1

表示的编程状态中,则当编程电压超过阈值电压v

th1

时,器件1切换到导电状态,并且允许显著水平的编程电流的穿过。脉冲100的下降侧翼的持续时间非常短(接近0)。对于有源层2的特定材料,显著的编程电流(即,器件1的导电状态)的存在和脉冲下降的实质上零的下降侧翼的持续时间的适当选择的组合使得可以修改器件1的阈值电压,并且具有从v

th1

至v

th2

的后来变化(因此,写入存储器状态v

th2

,尽管存储器状态v

th1

被写入在存储器器件1中)。

[0095]

编程脉冲的下降持续时间与阈值电压之间的关联在图7中示出,图7示出了对于有源层mat1、mat2和mat3的三种材料,阈值电压v

th

(以伏特为单位)根据下降侧翼的斜率(以v/s为单位)的行为。

[0096]

有源材料mat1是as2te3和ge3se7合金的混合物,具有按重量计20%的as2te3。

[0097]

有源材料mat2是as2te3和ge3se7合金的混合物,具有按重量计40%的as2te3。

[0098]

有源材料mat3是as2te3和ge3se7合金的混合物,具有按重量计60%的as2te3。

[0099]

图9中定义了下降侧翼的斜率(“斜坡率”)。这是编程电压脉冲的最大幅度和下降侧翼的持续时间之间的比率。在其它方面,对于给定幅度,下降侧翼的持续时间越短,斜率越大。

[0100]

在图7中观察到,对于材料mat1,阈值电压随着下降侧翼的斜率显著地增加。由此,对于组合物mat1,存在阈值电压v

th

的窗口,该阈值电压v

th

的窗口在从约2.25v的电压阈值(对于约0.5.107v/s的斜率,即,显著的下降侧翼的持续时间)至约3.5v的阈值电压(对于约0.8.109v/s的斜率,即,非常短的下降侧翼的持续时间)的范围内是非常显著的。

[0101]

因此,如果器件处在由阈值电压v

th1

表示的编程状态中,并且脉冲100的下降侧翼的非常短的持续时间被用于处于导电状态的器件1,则阈值电压的值将由于侧翼的持续时间而被修改,并且将通过选择下降侧翼的适当持续时间,将阈值电压改变为值v

th2

。

[0102]

脉冲101(称为设置)是用于使器件1达到由第一阈值电压v

th1

表示的编程状态的编程脉冲。该脉冲具有大于第二阈值电压v

th2

的电压强度和具有大于脉冲100的下降侧翼的持续时间的持续时间的下降侧翼。

[0103]

在此,与复位编程相反,脉冲101的效应独立于起始存储器状态。因为编程脉冲101具有超过第二阈值电压v

th2

的电压强度(并且,因此更不用说阈值电压v

th1

),所以一旦超过其阈值电压(无论其是v

th1

还是v

th2

),器件1就将变得导电。因此,电流将达到实质上足够的电流水平。然后,本发明在于有源层2的材料的选择,从而下降侧翼的持续时间使得可以传

到第一阈值电压v

th1

。在此,下降侧翼的斜率(“斜坡率”)有利地包括在107v/s与106v/s之间,这可以例如,对于包括在350ns与3.5μs之间的下降侧翼的持续时间引起3.5v的脉冲。通过施加这种减少的持续时间,第一阈值电压v

th1“写入”在器件1中。

[0104]

在图7中观察到,材料mat1相对于材料mat2和mat3具有最大存储器窗口(并且因此,第一阈值电压v

th1

与第二阈值电压v

th2

之间的最大差值)。因此,优选地选择按重量计约20%百分比的as2te3合金。然而,具有按重量计约40%百分比的as2te3合金的材料mat2也提供了更多减小的窗口的这种可能性。另一方面,具有按重量计约60%百分比的as2te3合金的材料mat3具有窗口,该窗口太小以至于不允许在根据本发明的同一器件中写入两个不同的电压阈值。注意,可以选择曲线的两端处的阈值电压v

th1

和v

th2

(vthmin和vthmax),但没有什么阻止放置在曲线的另一位置处:在这种情况下,因此,将适配下降侧翼的斜率的持续时间(并且,如果认为第二阈值电压v

th2

低于v

th2

的最大值,则对于脉冲101减少该持续时间)。

[0105]

有利地,用于有源层2的合金在器件1作为nvts的运行期间不具有任何结晶。

[0106]

这种类型的行为与在施加具有足够长的下降侧翼的脉冲期间发生的材料结构的重组有关,引起器件的阈值电压的降低。应当强调,即使对于as2te3存在结晶相,并且对于ge3se7存在结晶相,在所考虑的as2te3和ge3se7合金的混合物的情况下,不存在相应的结晶相。仅相偏析可以引起一个或多个结晶相的形成(即,例如,在温度过度升高之后、在器件的过度电阻状态/导电状态循环之后等达到)。然而,可以通过在器件中保留与部分地或完全地结晶的相平行的无定形相,获得nvts类型的行为。该配置还与本发明的目的的器件1的存储器和选择性功能兼容。

[0107]

通常地,用于对根据本发明的器件进行编程的方法包括:

[0108]-复位步骤,包括根据器件1的有源层的材料,施加包括在v

th1

和v

th2

之间的具有预定持续时间的下降侧翼的电压脉冲,以使器件1达到由第一阈值电压v

th2

表示的编程状态;

[0109]-设置步骤,包括根据器件1的有源层的材料,施加具有预定的非零持续时间的预定下降侧翼的大于v

th2

,并且大于复位编程电压脉冲的下降侧翼的持续时间的电压脉冲,以使器件1达到由第二阈值电压v

th1

表示的编程状态。

[0110]

图8示出了对于器件1的有源层2的三种材料mat1、mat2和mat3,根据编程脉冲的下降侧翼的斜率,亚阈值电流(“漏电流”)的行为。观察到,对于三种材料mat1、mat2和mat3,该亚阈值电流保持在远小于10-7

a的非常低的值,而不管编程脉冲的下降侧翼的斜率的值如何。这种行为使得可以提供器件1的选择性功能。

[0111]

图6中所示的脉冲102是使得可以读取器件1的存储器状态的脉冲。读取脉冲102由具有在第一阈值电压v

th1

和第二阈值电压v

th2

之间的中间电压的脉冲形成。在读取由第一阈值电压v

th1

表示的编程状态的情况下,由于超过阈值电压v

th1

,器件1将变得导电,但是具有与设置写入的持续时间基本上相同的脉冲的实质持续时间的下降侧翼将使得可以重构由第一初始阈值电压v

th1

表示的编程状态,而没有写入第二编程状态v

th2

的风险。检测通过器件1的电流指示器件1处于存储器状态v

th1

。相反,在读取由第二阈值电压v

th2

表示的编程状态的情况下,器件1将保持电阻性(无切换),因为不超过第二阈值电压v

th2

。在器件1中没有检测电流指示器件处于存储器状态v

th2

。如果没有发生切换,则读取状态v

th2

,并且同时维持该状态v

th2

,不存在干扰的风险(例如不合时宜的写入)。

[0112]

通常地,根据本发明的用于读取器件的存储器状态的方法包括施加严格地大于vth1

且严格地小于v

th2

的电压脉冲的步骤,该电压脉冲具有预定的非零持续时间的预定下降侧翼,并且大于第二存储器状态v

th2

的编程电压脉冲的下降侧翼的持续时间(有利地,与第一存储器状态v

th1

的编程电压脉冲的下降侧翼的持续时间基本上相同,即,具有有利地包括在107v/s与106v/s之间的下降侧翼的斜率)。

[0113]

鉴于编程脉冲的斜率对有源层2的材料的影响,可以考虑v

th1

和v

th2

之间的中间编程状态,以便获得mlc(“多层单元”)类型的多层编程。

[0114]

还应注意,有源层的厚度有利地根据第一阈值电压v

th1

与第二阈值电压v

th2

之间的期望差值来选择。特别地在图10中示出该选择,图10示出了根据对于有源层2的四个不同厚度:10nm、15nm、25nm和50nm的阈值电压,材料mat2的电压阈值的变化。因此,有源层的厚度的增加有利地增加了存储器窗口,即,最小阈值电压与最大阈值电压两个之间的可能差值。这种增加背离pcram的当前趋势,其目的在于减小pcram的厚度。

[0115]

虽然在d’as2te3和ge3se7的混合物的情况下更具体地描述了本发明,但可以使用其他合金,例如与si、ge、as、sb、bi、s、se、te的基质组合在一起,而且还与元素(即,掺杂剂),如c、n或o的引入一起使用。特别地,具有不同化学计量的asse、aste、gese、ges合金是可以被组合以获得所寻求的机理的那些合金之中。有利地,可以使用iv-vi型合金(例如,具有ge和se基质)与vi-v型合金(例如,具有as和te基质)之间的组合,iv-vi型合金的间隙能量比vi-v合金的间隙能量更显著。此外,注意,尽管有源层2被描述为材料层(as2te3和ge3se7合金的混合物),但是提供存储器行为和nvts选择器的多层材料形式的有源层的配置也适用于根据本发明的器件。

[0116]

不同层(电极、有源层)的沉积技术是本领域技术人员熟知的。这些可以是例如,物理气相沉积(pvd)、化学气相沉积(cvd)或原子层沉积(ald)类型的技术。

[0117]

当然,仅出于示例的目的给出了上文提出的编程;可以考虑智能编程,其中,脉冲可以取决于器件的初始编程状态。例如,这是当根据本发明的器件刚刚被读取,并且待编程状态对应于刚刚被读取的状态时的情况:在这种情况下,可以克服编程脉冲。

[0118]

同样地,使得可以获得处于存储器状态v

th1

的材料的结构重组的任何形式的脉冲当然构成可能的替代方案。特别地,可以通过考虑对阈值电压v

th

的变化具有有效影响的相同侧翼的部分来进一步减小脉冲的下降侧翼。图11中示出了这种类型的脉冲200。与图6的被称为设置的脉冲101相反,脉冲200也是用于使器件1达到由第一阈值电压v

th1

表示的编程状态的设置编程脉冲。该脉冲200具有大于第二阈值电压v

th2

的电压强度和减小的下降侧翼201,但是其持续时间保持大于图6的脉冲100的下降侧翼的持续时间。该评述对于读取脉冲也是有效的。

[0119]

图6和图11的每个脉冲的总持续时间被选择为保证器件的切换(如果需要的话)以及编程电流通过足够的持续时间特别地达到状态v

th2

。对于as2te3和ge3se7合金的混合物,该总持续时间可以例如,包括在10ns与300ns之间。取决于根据本发明的器件的尺寸(即,表面)的编程电流在我们示例的情况下包括在1ma和2ma之间。

[0120]

在替代方案中,根据本发明的器件可以与电阻存储器串联地共集成,以产生使得可以使用根据本发明的器件的选择特性来访问(读取和编程)电阻存储器和同时具有内在的存储器特性的器件。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。