一种基于zynq芯片的数据存储及传输系统

技术领域

1.本发明涉及雷达通信技术,具体涉及一种基于zynq芯片的数据存储及传输系统。

背景技术:

2.作为信息处理的重要组成部分,高速连续数据传输已经在很多方面得到应用,特别在电子对抗领域,电子侦察的信号已然呈现出“大数据”的趋势。随着各种复杂雷达技术及人工智能在电子侦察处理信号的深入应用,对数据的采集也提出了更高的要求。

3.但目前设备大多采用固态硬盘、sd卡等外部存储模式,在机载等场景使用时,由于可靠性较低,面对的环境较为复杂,温度要求苛刻,颠簸严重,很可能导致外部存储失效。

4.对于在实际对雷达干扰过程中对其干扰不理想或者一些异常情况往往需要复盘及分析,所以往往需要将使用过程中一些信息定期存储下来。便于后期在进行复盘时能够从数据中了解设备运行时的实际工作情况,为后期提高产品性能、提升稳定性,实现更加有效的干扰效果奠定基础。这个存储需要一定的容量要求。往往需要增加一个存储模块,不仅增加成本还增加了体积,不利于适用更小型化的应用场景。

技术实现要素:

5.发明目的:本发明的目的在于解决现有技术中存在的不足,提供一种基于zynq芯片的数据存储及传输系统,能够连续高速数据传输及工作日志存取。

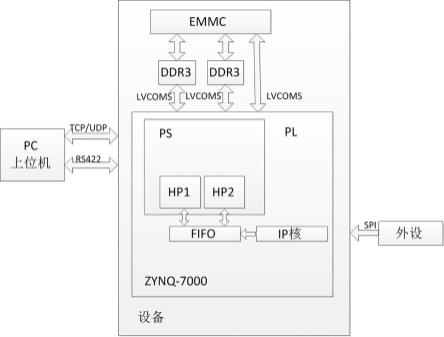

6.技术方案:本发明的一种基于zynq芯片的数据存储及传输系统,包括上位机和基于zynq开发板的主控设备,主控设备包括显控交互模块、内部通信模块和核心处理模块;所述内部通信模块通过网络接口分别与显控交互模块和核心处理模块进行通信,内部通信模块基于串行数据接口连接于外部通信设备;也就是说内部通信模块实现pl到ps以及ps到pl的数据交互、所有外设的数据交互;所述核心处理模块由上位机控制,通过内部通信模块与外部通信设备实现通信,并对接收到的数据进行处理、数据连续存储和工作日志存储,并将对应信息实时传输给外部通信设备,同时将存储及传输器的工作状态和存储数据按时序发送至上位机;所述显控交互模块通过内部通信模块接收核心处理模块的运行状态、工作日志和其他相关数据(包括各个外部通信设备接口通信的命令控制报文等);以及通过上位机配置相关参数下发给核心处理模块以进行各种数据的输入输出及命令控制;上位机通过网络协议接口和串行接口分别给核心处理模块发送指令。

7.进一步地,所述上位机设有x86处理器、100/1000m以太网接口、液晶屏接口和串行接口, x86处理器配置相关参数下发给核心处理模块以进行各种数据的输入输出及命令控制;上位机通过100/1000m以太网接口和串行接口分别给核心处理模块发送指令,通过液晶屏接口连接显示器。本发明的上位机可运行win10操作系统,并根据实际应用需要配置不同上位机应用软件。

8.进一步地,所述核心处理模块包括emmc存储器、ddr3缓存器、100/1000m以太网接口、spi接口、uart 以及zynq芯片自带pl的pfga处理器和ps的arm处理器;通过100/1000m以

太网接口与上位机通信,spi接口用于和外部信号产生单元通信,uart包括422和232,422用于接无线数传,远距离和上位机通信,可用于靶机、船舰等远距离通信场景。232可用于接外部其他设备,如电池、微波等t;核心处理模块对数据进行连续存储,包括以下步骤:步骤1)、zynq的pl端通过外部通信设备获取连续的数据,然后经过fifo缓存于ddr3缓存器a,当达到一定门限后将数据再缓存于ddr3缓存器b,当再次达到一定门限后后重新缓存于ddr3缓存器a,将接收的数据依次循环缓存在ddr3缓存器a和ddr3缓存器b中;步骤2)、zynq的ps端核1通过标志位来判断当前ddr3写入的状态;当数据开始缓存在ddr3缓存器b中时,ps端核1不断读取ddr3缓存器a里的数据,达到门限后将读取的数据一并写入emmc存储器中;当数据开始缓存在ddr3缓存器a中时,ps端核1不断读取ddr3缓存器b里的数据,达到门限后将当前读取的数据一并写入emmc存储器中;依次循环来读取ddr3缓存器a和ddr3缓存器b中的数据,最终都存储于emmc存储器中。

9.步骤3)、若需导出emmc存储器中的数据,则通过上位机发送emmc数据导出命令;核心处理模块通过内部通信模块接收导出命令后,通过读写指针来判断需要上传的数据包数,并且按照数据包格式将emmc存储器中存储的数据一包包的上传给上位机;步骤4)、上位机将接收到的数据解析后形成可读文件存于本地指定文件夹;在上述步骤1)至步骤4)过程中,上位机可随时通过中止命令结束设备核心处理模块的数据上传;且上位机可随时通过覆盖命令复位emmc存储,使emmc从头开始存储。

10.进一步地,所述核心处理模块包括emmc存储器、ddr3缓存器、100/1000m以太网接口、spi接口、uart以及 zynq芯片自带pl的pfga处理器和ps的arm处理器;主核spi接口用于接信号产生单元,uart和100/1000m以太网接口用于和上位机报文通信,从核用于定时存储工作日志,包括接收到上传命令后,用于通过100/1000m以太网把存储的工作日志传给上位机;核心处理模块对工作日志进行存储,详细过程如下:步骤1)、将emmc存储器内部划分成三个不同功能的存储区域且基地址不同;其中,存储区域一存储工作日志,存储区域二存储pdw数据,存储区域三存储edw数据;步骤2)、zynq的ps端核2 将运行中的本机状态、外设状态及运行过程的相应数据定期以报文格式汇总成数据包,并将数据包存入ddr3缓存器的特殊缓存区;步骤3)、zynq的ps端核1通过标志位判断去读取ddr3缓存器的特殊缓存区内的数据包并存入emmc存储器中;步骤4)、若需导出emmc存储器中的数据时,则通过上位机发送日志数据导出命令;核心处理模块通过内部通信模块接收导出命令后,通过读写指针来判断需要上传的数据包数,并按照数据包格式将emmc存储器中存储的日志数据包按序上传给上位机;步骤5)、上位机将接收到的数据包解析后形成可读文件存于本地指定文件夹;步骤6)、上位机点击日志回放命令后去读取解析后的文件,形成指定的显示效果;且可复现其中任意一段的交互命令,实现异常问题的复现;上述步骤1)至步骤5)过程中,上位机可通过中止命令随时结束设备核心处理模块的数据上传,以及可通过覆盖命令复位emmc存储,使emmc从头开始存储。

11.进一步地,将所述emmc存储器中存储的数据导出至上位机的具体过程为:

步骤1)、将zynq的ps端通过tcp/udp接口和rs422接口连接至上位机;步骤2)、上位机通过tcp/udp和rs422给zynq的ps端发送导出指令;步骤3)、zynq的ps端按照导出指令以及结合emmc读写的指针确认传递包数;ps端读取emmc存储数据,并且按照单签数据包格式,分包上传至上位机。

12.进一步地,所述内部通信模块使用tcp/udp网络通信协议通过对应接口分别连接显控交互模块和核心处理模块;所述内部通信模块使用rs422和rs232串口通过差分转换芯片和电平转换芯片与外部通信设备相连接;所述内部通信模块使用spi接口快速读写外部通信设备的数据。

13.有益效果:本发明技术方案提供一种高速大容量的传输方式,解决了现有雷达系统中的数据传输及日志存储后期回放的问题;与现有技术相比,本发明具有以下优点:(1)、存储速度高;本发明在zynq开发板上设置emmc存储器,能够实时记录高速连续的原始数据;(2)、存储容量大,高速多通道数据采集会有大量数据需要存储后解析;(3)存储可靠性高;本发明将emmc存储器与ddr缓存配合使用实现连续的接收存储,能够面对复杂的工作环境,保证存储设备的稳定工作及存储的正确性;(4)、抗震性好,雷达数据的获得一般通过车载、机载、弹载等发送,要求设备能够抗震动及抗冲击力;(5)本发明便携性好,小巧方便不占体积,可用于各种使用场景。

附图说明

14.图1为本发明一实施例的整体结构示意图;图2为本发明一实施例的通信示意图。

具体实施方式

15.下面对本发明技术方案进行详细说明,但是本发明的保护范围不局限于所述实施例。

16.如图1和图2所示,本实施例的的一种基于zynq芯片的数据存储及传输系统,包括上位机和基于zynq开发板的主控设备,主控设备包括显控交互模块、内部通信模块和核心处理模块;内部通信模块通过网络接口分别与显控交互模块和核心处理模块进行通信,内部通信模块基于串行数据接口连接于外部通信设备; 核心处理模块由上位机控制,通过内部通信模块与外部通信设备实现通信,并对接收到的数据进行处理、数据连续存储和工作日志存储,并将对应信息实时传输给外部通信设备,同时将存储及传输器的工作状态和存储数据按时序发送至上位机;显控交互模块通过内部通信模块接收核心处理模块的运行状态、工作日志和其他相关数据;以及通过上位机配置相关参数下发给核心处理模块以进行各种数据的输入输出及命令控制;上位机通过网络协议接口和串行接口分别给核心处理模块发送指令。

17.本实施例的上位机设有x86处理器、100/1000m以太网接口、液晶屏接口和串行接口, x86处理器配置相关参数下发给核心处理模块以进行各种数据的输入输出及命令控

制;上位机通过100/1000m以太网接口和串行接口分别给核心处理模块发送指令,通过液晶屏接口连接显示器。本发明的上位机可运行win10操作系统,并根据实际应用需要配置不同上位机应用软件。

18.本实施例的核心处理模块包括zynq芯片自带pl的pfga处理器、ps的arm处理器以及emmc存储器、ddr3缓存器、100/1000m以太网接口、spi接口和uart;核心处理模块对数据进行连续存储,包括以下步骤:步骤1)、zynq的pl端通过外部通信设备获取连续的数据,然后经过fifo缓存于ddr3缓存器a,当达到一定门限后将数据再缓存于ddr3缓存器b,当再次达到一定门限后后重新缓存于ddr3缓存器a,将接收的数据依次循环缓存在ddr3缓存器a和ddr3缓存器b中;步骤2)、zynq的ps端核1通过标志位来判断当前ddr3写入的状态;当数据开始缓存在ddr3缓存器b中时,ps端核1不断读取ddr3缓存器a里的数据,达到门限后将读取的数据一并写入emmc存储器中;当数据开始缓存在ddr3缓存器a中时,ps端核1不断读取ddr3缓存器b里的数据,达到门限后将当前读取的数据一并写入emmc存储器中;依次循环来读取ddr3缓存器a和ddr3缓存器b中的数据,最终都存储于emmc存储器中。

19.步骤3)、若需导出emmc存储器中的数据,则通过上位机发送emmc数据导出命令;核心处理模块通过内部通信模块接收导出命令后,通过读写指针来判断需要上传的数据包数,并且按照数据包格式将emmc存储器中存储的数据一包包的上传给上位机;步骤4)、上位机将接收到的数据解析后形成可读文件存于本地指定文件夹;在上述步骤1)至步骤4)过程中,上位机可随时通过中止命令结束设备核心处理模块的数据上传;且上位机可随时通过覆盖命令复位emmc存储,使emmc从头开始存储。

20.本实施例的核心处理模块包括zynq芯片自带pl的pfga处理器、ps的arm处理器以及emmc存储器、ddr3缓存器、100/1000m以太网接口、spi接口和uart;其中核心处理模块对工作日志进行存储,详细过程如下:步骤1)、将emmc存储器内部划分成三个不同功能的存储区域且基地址不同;步骤2)、zynq的ps端核2 将运行中的本机状态、外设状态及运行过程的相应数据定期以报文格式汇总成数据包,并将数据包存入ddr3缓存器的特殊缓存区;步骤3)、zynq的ps端核1通过标志位判断去读取ddr3缓存器的特殊缓存区内的数据包并存入emmc存储器中;步骤4)、若需导出emmc存储器中的数据时,则通过上位机发送日志数据导出命令;核心处理模块通过内部通信模块接收导出命令后,通过读写指针来判断需要上传的数据包数,并按照数据包格式将emmc存储器中存储的日志数据包按序上传给上位机;步骤5)、上位机将接收到的数据包解析后形成可读文件存于本地指定文件夹;步骤6)、上位机点击日志回放命令后去读取解析后的文件,形成指定的显示效果;且可复现其中任意一段的交互命令,实现异常问题的复现;上述步骤1)至步骤5)过程中,上位机可通过中止命令随时结束设备核心处理模块的数据上传,以及可通过覆盖命令复位emmc存储,使emmc从头开始存储。

21.上述emmc存储器中存储的数据导出至上位机的具体过程为:

步骤1)、将zynq的ps端通过tcp/udp接口和rs422接口连接至上位机;步骤2)、上位机通过tcp/udp和rs422给zynq的ps端发送导出指令;步骤3)、zynq的ps端按照导出指令以及结合emmc读写的指针确认传递包数;ps端读取emmc存储数据,并且按照单签数据包格式,分包上传至上位机。

22.本实施例的内部通信模块使用tcp/udp网络通信协议通过对应接口分别连接显控交互模块和核心处理模块;内部通信模块使用rs422和rs232串口通过差分转换芯片和电平转换芯片与外部通信设备相连接;内部通信模块使用spi接口快速读写外部通信设备的数据。

23.通过上述实施例可以看出,本发明将dma、ddr、emmc相互配合,通过乒乓缓存实现连续数据如pdw的存储,其连续存储速度能够达到500ms左右。并且本发明的上位机可定时存储收到的状态信息,需要额外的存储介质;主控设备上位机的上传指令时可发送给上位机,一旦出现异常,只要没有断电,仍然会把工作日志存储下来,还可通过后期查阅日志也能知道故障之前的工作状态。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。