1.本实用新型涉及计算机硬件领域,尤其涉及一种基于龙芯双系统平台的主控板。

背景技术:

2.安全可信、自主可控是当前形势对国产计算平台提出的要求,其中安全可信设计是国产计算设备的核心竞争力,硬件架构与软件算法设计则是国产计算设备的可创新突破点。安全可信设计包括理论层面的自主密码体制、芯片层面的主动控制、主控板层面的计算可信双节点融合、软件层面的双系统体系结构等内容。

3.作为新一代开放式工业标准,atca(advanced telecom computingarchitecture,先进电信计算架构)自2002年推出后,就受到了业界瞩目。在产业链诸多企业的大力推进下,目前已经逐渐被业界接受。许多主要的电信设备制造商都已经采用atca设计新产品。现在,atca已从小范围的应用走向大家都普遍认可,并将会得到大规模的应用。

4.在实际生产过程中,有用户提出如下需求:能同时处理不同业务类型,而且处理不同业务时不能相互影响、同时要求采用的器件及操作系统等全国产化的计算机主控板。基于此,有必要设计一种基于双系统平台的计算机主控板。

技术实现要素:

5.本实用新型的目的在于提供一种基于龙芯双系统平台的主控板,能同时处理不同业务类型,而且处理不同业务时不会相互影响,且具有较高的系统集成度。

6.为了达到上述目的,本实用新型提供了一种基于龙芯双系统平台的主控板,包括龙芯通用处理器、桥片、龙芯嵌入式处理器、fpga、微控制单元、第一内存芯片、第二内存芯片、及第三内存芯片;

7.所述龙芯通用处理器与桥片通信连接,所述龙芯嵌入式处理器、fpga及微控制单元均与所述桥片通信连接,所述fpga及微控制单元均与所述龙芯嵌入式处理器通信连接,所述fpga与微控制单元通信连接;

8.所述第一内存芯片与龙芯通用处理器通信连接,第二内存芯片与龙芯嵌入式处理器通信连接,第三内存芯片与fpga通信连接。

9.用于atca设备的核心控制板。

10.所述第一内存芯片、第二内存芯片、及第三内存芯片均为板载的内存芯片;

11.所述第一内存芯片、第二内存芯片、及第三内存芯片均为ddr内存芯片;

12.所述第一内存芯片的容量为8gb,所述第二内存芯片的容量为4gb,所述第三内存芯片的容量为4gb。

13.所述龙芯通用处理器及桥片用于构成一个系统平台,所述龙芯嵌入式处理器用于构成另一个系统平台,两个系统平台分别独立运行各自的操作系统,所述龙芯通用处理器与所述龙芯嵌入式处理器分别连接不同的电源,从而两个系统平台能够进行独立的开关

机。

14.所述龙芯通用处理器为ls3a4000系列芯片,所述桥片为ls7a1000系列芯片,所述龙芯嵌入式处理器为ls2k1000系列芯片。

15.所述龙芯通用处理器具有uart端口、及spi端口,所述基于龙芯双系统平台的主控板还包括与uart端口通信连接的debug器件、及与spi端口通信连接的spi flash。

16.所述桥片具有pcie

×

4端口、sata2.0端口、usb2.0端口、uart端口、及dvo端口;

17.所述pcie

×

4端口的数量为三个,所述sata2.0端口、usb2.0端口、及 dvo端口的数量均为一个,所述uart端口的数量为四个;

18.所述基于龙芯双系统平台的主控板还包括第一zd连接器、第一网络芯片、第二网络芯片、第一显示信号转换芯片、第一msata插槽、usb2.0接口、第二zd连接器、千兆网口、第三zd连接器、及vga信号接口;

19.所述桥片通过三个pcie

×

4端口分别通信连接第一zd连接器、第一网络芯片及第二网络芯片;所述第一网络芯片输出网络信号至千兆网口,所述第二网络芯片输出网络信号至第三zd连接器;

20.所述第一显示信号转换芯片分别与所述dvo端口及vga信号接口通信连接,所述第一显示信号转换芯片从dvo端口接收dvo信号并将其转换为vga 信号输出至vga信号接口;

21.所述桥片通过四个uart端口分别通信连接fpga、第二zd连接器、微控制单元、及龙芯嵌入式处理器;

22.所述桥片通过sata2.0端口通信连接第一msata插槽,所述桥片通过 usb2.0端口通信连接usb2.0接口。

23.所述龙芯嵌入式处理器具有pcie

×

4端口、rgmii端口、dvo端口、pcie

ꢀ×

1端口、uart端口、sata端口、及usb2.0端口;

24.所述基于龙芯双系统平台的主控板还包括第三网络芯片、第四网络芯片、第四zd连接器、第二显示信号转换芯片、第五zd连接器、第六zd连接器、第二msata插槽、及第七zd连接器;

25.所述pcie

×

4端口、rgmii端口、dvo端口、pcie

×

1端口、sata端口、及usb2.0端口的数量均为一个,所述uart端口的数量为两个;

26.所述龙芯嵌入式处理器通过rgmii端口通信连接第三网络芯片;所述第三网络芯片与第二网络芯片通信连接,从而实现桥片及龙芯嵌入式处理器输出的网络信号的板内互联;

27.所述龙芯嵌入式处理器通过pcie

×

4端口通信连接第四网络芯片,所述第四网络芯片31通信连接第四zd连接器;

28.所述第二显示信号转换芯片分别与所述dvo端口及第五zd连接器通信连接,所述第二显示信号转换芯片从dvo端口接收dvo信号并将其转换为vga 信号输出至第五zd连接器;

29.所述龙芯嵌入式处理器通过pcie

×

1端口通信连接第六zd连接器;所述龙芯嵌入式处理器通过两个uart端口分别通信连接fpga及微控制单元;所述龙芯嵌入式处理器通过sata端口通信连接第二msata插槽;所述龙芯嵌入式处理器通过usb2.0端口通信连接第七zd连接器。

30.还包括第八zd连接器、风机控制芯片、扩展io芯片、及时序控制cpld 芯片;

31.所述微控制单元具有两个i2c端口及一个uart端口;

32.所述微控制单元通过两个i2c端口分别通信连接风机控制芯片及扩展io 芯片,所述扩展io芯片输出gpio信号至时序控制cpld芯片;所述微控制单元通过uart端口通信连接fpga;

33.所述fpga具有lvds端口,所述fpga通过lvds端口通信连接第八zd连接器。

34.所述龙芯通用处理器的型号为ls3a4000-i,所述桥片的型号为 ls7a1000-ba,所述龙芯嵌入式处理器的型号为ls2k1000-i,所述fpga的型号为国微电子smq7k325tffg676,所述微控制单元的型号为兆易创新 gd32f450iih6;

35.所述第一显示信号转换芯片及第二显示信号转换芯片的型号均为振芯gm7123c,所述风机控制芯片的型号为兆易创新gd32f103c8t6,所述扩展io 芯片的型号为艾为电子aw9110b,所述时序控制cpld芯片的型号为高云半导体gw1n-uv4lq1006/i5,所述第一网络芯片的型号为网迅科技wx1860a2,第二网络芯片的型号为网迅科技wx1860a4,第三网络芯片的型号为裕太微电子 yt8521sh-ca,第四网络芯片的型号为网迅科技wx1860a4。

36.本实用新型的有益效果:本实用新型提供的一种基于龙芯双系统平台的主控板,包括龙芯通用处理器、桥片、龙芯嵌入式处理器、fpga、微控制单元、第一内存芯片、第二内存芯片、及第三内存芯片;所述龙芯通用处理器与桥片通信连接,所述龙芯嵌入式处理器、fpga及微控制单元均与所述桥片通信连接,所述fpga及微控制单元均与所述龙芯嵌入式处理器通信连接,所述fpga与微控制单元通信连接;所述第一内存芯片与龙芯通用处理器通信连接,第二内存芯片与龙芯嵌入式处理器通信连接,第三内存芯片与fpga通信连接。本实用新型包括龙芯通用处理器系统平台和龙芯嵌入式处理器系统平台,能够独立运行各自的操作系统,互不干扰,并支持国产操作系统。且将两个系统平台设计到同一块主控板中,两者又能分工协助,处理不同的业务类型,提高系统的集成度。

附图说明

37.为了能更进一步了解本实用新型的特征以及技术内容,请参阅以下有关本实用新型的详细说明与附图,然而附图仅提供参考与说明用,并非用来对本实用新型加以限制。

38.附图中,

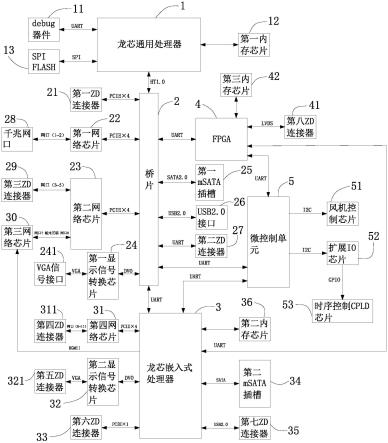

39.图1为本实用新型的基于龙芯双系统平台的主控板的模块示意图。

具体实施方式

40.为更进一步阐述本实用新型所采取的技术手段及其效果,以下结合本实用新型的优选实施例及其附图进行详细描述。

41.请参阅图1,本实用新型提供一种基于龙芯双系统平台的主控板,用于 atca设备的核心控制板,该atca设备应用于网络通信领域。所述主控板包括龙芯通用处理器1、桥片2、龙芯嵌入式处理器3、现场可编程门阵列 (field programmable gate array,fpga)4、微控制单元 (microcontroller unit,mcu)5、第一内存芯片12、第二内存芯片36、及第三内存芯片42。

42.所述龙芯通用处理器1与桥片2通信连接,所述龙芯嵌入式处理器3、 fpga 4及微

控制单元5均与所述桥片2通信连接,所述fpga4及微控制单元5均与所述龙芯嵌入式处理器3通信连接,所述fpga4与微控制单元5通信连接。

43.所述第一内存芯片12与龙芯通用处理器1通信连接,第二内存芯片36与龙芯嵌入式处理器3通信连接,第三内存芯片42与fpga4通信连接。

44.可选地,所述龙芯通用处理器1与桥片2通过端到端总线技术(hypertransport,ht)1.0总线实现通信连接。

45.所述龙芯通用处理器1为ls3a4000系列芯片,所述桥片2为ls7a1000系列芯片,所述龙芯嵌入式处理器3为ls2k1000系列芯片。

46.优选地,所述龙芯通用处理器1的型号为ls3a4000-i,所述桥片2的型号为ls7a1000-ba,所述龙芯嵌入式处理器3的型号为ls2k1000-i。

47.所述fpga4的型号为国微电子smq7k325tffg676,所述微控制单元5的型号为兆易创新gd32f450iih6。

48.具体地,所述主控板采用板载内存方式,也即主控板上本身集成内存。板载内存相较于非板载内存,性能稳定性及结构稳定性等方面都有提高。即所述第一内存芯片12、第二内存芯片36、及第三内存芯片42均为板载的内存芯片。

49.具体地,所述第一内存芯片12、第二内存芯片36、及第三内存芯片42均为ddr(doubledatarate,双倍速率同步动态随机存储器)内存芯片。所述第一内存芯片12的容量为8gb,所述第二内存芯片36的容量为4gb,所述第三内存芯片42的容量为4gb。

50.优选地,所述第一内存芯片12为第四代双倍速率(doubledatarate4,ddr4)内存芯片。所述第二内存芯片36为第三代双倍速率(doubledatarate3,ddr3)内存芯片。所述第三内存芯片42为ddr3内存芯片。

51.在本实用新型的一具体实施例中,所述第一内存芯片12为板载的八颗ddr4内存芯片,总容量为8gb。所述第二内存芯片36为板载的四颗ddr3内存芯片,总容量为4gb。所述第三内存芯片42为板载的四颗ddr3内存芯片,总容量为4gb。

52.具体地,所述龙芯通用处理器1具有通用异步收发传输器(universalasynchronousreceiver/transmitter,uart)端口、及串行外设(serialperipheralinterface,spi)端口,所述主控板还包括与uart端口通信连接的debug器件11、及与spi端口通信连接的串行外设(serialperipheralinterface,spi)闪存(flash)13。

53.所述桥片2具有高速串行计算机扩展总线标准(peripheralcomponentinterconnectexpress,pcie)

×

4端口、串行高级技术附件(serialadvancedtechnologyattachment,sata)2.0端口、usb2.0端口、uart端口、及数字视频输出(digitalvisualoutput,dvo)端口。

54.所述pcie

×

4端口的数量为三个,所述sata2.0端口、usb2.0端口、及dvo端口的数量均为一个,所述uart端口的数量为四个。

55.所述主控板还包括第一zd连接器(高速板对板连接器)21、第一网络芯片22、第二网络芯片23、第一显示信号转换芯片24、第一msata(miniserialadvancedtechnologyattachment)插槽25、usb2.0接口26、第二zd连接器27、千兆网口28、第三zd连接器29、及视频图形阵列(videographicsarray,vga)信号接口241。

56.所述桥片2通过三个pcie

×

4端口分别通信连接第一zd连接器21、第一网络芯片

22、及第二网络芯片23。所述第一网络芯片22输出网络信号至千兆网口28,所述第二网络芯片23输出网络信号至第三zd连接器29。

57.所述第一显示信号转换芯片24分别与所述dvo端口及vga信号接口241 通信连接,所述第一显示信号转换芯片24从dvo端口接收dvo信号并将其转换为vga信号输出至vga信号接口241。

58.所述桥片2通过四个uart端口分别通信连接fpga 4、第二zd连接器 27、微控制单元5、及龙芯嵌入式处理器3。

59.所述桥片2通过sata2.0端口通信连接第一msata插槽25,从而在外接存储设备后进行数据传输。所述桥片2通过usb2.0端口通信连接usb2.0接口26,从而输出usb2.0信号。

60.具体地,所述龙芯嵌入式处理器3具有pcie

×

4端口、简化的吉比特媒体独立(reduced gigabit media independent interface,rgmii)端口、 dvo端口、pcie

×

1端口、uart端口、sata端口、及usb2.0端口。

61.所述主控板还包括第三网络芯片30、第四网络芯片31、第四zd连接器 311、第二显示信号转换芯片32、第五zd连接器321、第六zd连接器33、第二msata插槽34、及第七zd连接器35。

62.所述pcie

×

4端口、rgmii端口、dvo端口、pcie

×

1端口、sata端口、及usb2.0端口的数量为一个,所述uart端口的数量为两个。

63.所述龙芯嵌入式处理器3通过rgmii端口通信连接第三网络芯片30。所述第三网络芯片30与第二网络芯片23通信连接,从而实现桥片2及龙芯嵌入式处理器3输出的网络信号的板内互联。

64.所述龙芯嵌入式处理器3通过pcie

×

4端口通信连接第四网络芯片31,所述第四网络芯片31通信连接第四zd连接器311。

65.所述第二显示信号转换芯片32分别与所述dvo端口及第五zd连接器 321通信连接,所述第二显示信号转换芯片32从dvo端口接收dvo信号并将其转换为vga信号输出至第五zd连接器321。

66.所述第一显示信号转换芯片24及第二显示信号转换芯片32的型号均为振芯gm7123c。

67.所述龙芯嵌入式处理器3通过pcie

×

1端口通信连接第六zd连接器 33,所述龙芯嵌入式处理器3通过两个uart端口分别通信连接fpga 4及微控制单元5;所述龙芯嵌入式处理器3通过sata端口通信连接第二msata插槽34,所述龙芯嵌入式处理器3通过usb2.0端口通信连接第七zd连接器 35。

68.具体地,所述主控板还包括第八zd连接器41、风机控制芯片51、扩展 io(input output,输入输出)芯片52、及时序控制cpld(complexprogrammable logic device,复杂可编程逻辑器件)芯片53。

69.所述微控制单元5具有两个i2c(inter-integrated circuit)端口及一个uart端口。所述微控制单元5通过两个i2c端口分别通信连接风机控制芯片51及扩展io芯片52,所述扩展io芯片52输出gpio(generalpurpose input/output,通用输入输出)信号至时序控制cpld芯片53。所述微控制单元5通过uart端口通信连接fpga 4。

70.所述fpga 4具有低电压差分信号(low-voltage differentialsignaling,lvds)

端口,所述fpga 4通过lvds端口通信连接第八zd连接器41。

71.所述风机控制芯片51的型号为兆易创新gd32f103c8t6,所述扩展io芯片52的型号为艾为电子aw9110b,所述时序控制cpld芯片53的型号为高云半导体gw1n-uv4lq1006/i5。

72.在本实用新型的一个具体实施例中,所述主控板集成了11路千兆网,所述第一网络芯片22的型号为网迅科技wx1860a2,第二网络芯片23的型号为网迅科技wx1860a4,第三网络芯片30的型号为裕太微电子yt8521sh-ca,第四网络芯片31的型号为网迅科技wx1860a4。所述千兆网口28的数量为两个,第一网络芯片22输出两路网络信号分别至两个千兆网口28(图1中记为网口(1~2))。所述第三zd连接器29包括三个千兆网口,所述第二网络芯片23输出四路网络信号,其中三路网络信号输出至第三zd连接器29(图1 中记为网口(3~5)),另一路网络信号(网口6)与第三网络芯片30输出的网络信号(网口7)实现网络信号板内互联(图1中记为网口7与网口6板内互联)。所述第四zd连接器311包括四个千兆网口,所述第四网络芯片31 输出四路网络信号至第四zd连接器311(图1中记为网口(8~11))。

73.具体地,所述第一zd连接器21、第二zd连接器27、第三zd连接器 29、第四zd连接器311、第五zd连接器321、第六zd连接器33、第七zd 连接器35、及第八zd连接器41均能够以高数据传输率实现高要求应用用途,数据传输率可达20或25gbit/s。优选为泰科电子有限公司的z-packhm-zd系列连接器。

74.所述第一zd连接器21、第二zd连接器27、第三zd连接器29、第四zd 连接器311、第五zd连接器321、第六zd连接器33、第七zd连接器35、及第八zd连接器41均用于通信连接测试板(图未示),从而通过测试板分别测试主控板上的pcie

×

4信号、uart信号、网口信号(网口(3~5))、网口信号(网口(8~11))、vga信号、pcie

×

1信号、usb信号、及lvds信号,进而验证主控板的相关功能。另一方面,所述第一zd连接器21、第二zd连接器27、第三zd连接器29、第四zd连接器311、第五zd连接器321、第六 zd连接器33、第七zd连接器35、及第八zd连接器41均还用于通信连接扩展板(图未示),从而实现主控板上的pcie

×

4信号、uart信号、网口信号 (网口(3~5))、网口信号(网口(8~11))、vga信号、pcie

×

1信号、usb信号、及lvds信号与扩展板的通信。

75.需要说明的是,本实用新型的基于龙芯双系统平台的主控板包括两个硬件平台(所述龙芯通用处理器及桥片用于构成一个系统平台,即龙芯通用处理器系统平台;所述龙芯嵌入式处理器用于构成另一个系统平台,即龙芯嵌入式处理器系统平台),能够独立运行各自的操作系统,能够支持国产操作系统(目前已适配中标麒麟桌面版操作系统和统信uos(unity operatingsystem)操作系统)。其中龙芯通用处理器为主处理器,龙芯嵌入式处理器为辅助处理器,这两个硬件平台有独立的外围接口,包括显示接口(如vga信号接口)、usb接口、及网络接口等。将龙芯通用处理器系统平台和龙芯嵌入式处理器系统平台设计到同一块主控板中,两者分工协助,处理不同的业务类型,提高系统的集成度。另一方面,由于龙芯通用处理器系统平台和龙芯嵌入式处理器系统平台分别独立运行各自的操作系统,并且所述龙芯通用处理器与所述龙芯嵌入式处理器分别连接不同的电源(图未示),从而两个系统平台可以进行独立的开关机,因此互不影响。也就是说,当龙芯通用处理器系统处于关机或出现异常不能正常工作时龙芯嵌入式处理器系统仍能够正常工作,反之当龙芯嵌入式处理器系统处于关机或出现异常不能正常工作时龙芯通用处理器系统也仍能够正常工作。

76.综上所述,本实用新型提供一种基于龙芯双系统平台的主控板,包括龙芯通用处理器、桥片、龙芯嵌入式处理器、fpga、微控制单元、第一内存芯片、第二内存芯片、及第三内存芯片;所述龙芯通用处理器与桥片通信连接,所述龙芯嵌入式处理器、fpga及微控制单元均与所述桥片通信连接,所述fpga及微控制单元均与所述龙芯嵌入式处理器通信连接,所述fpga与微控制单元通信连接;所述第一内存芯片与龙芯通用处理器通信连接,第二内存芯片与龙芯嵌入式处理器通信连接,第三内存芯片与fpga通信连接。本实用新型包括龙芯通用处理器系统平台和龙芯嵌入式处理器系统平台,能够独立运行各自的操作系统,互不干扰,并支持国产操作系统。且将两个系统平台设计到同一块主控板中,两者又能分工协助,处理不同的业务类型,提高系统的集成度。

77.以上所述,对于本领域的普通技术人员来说,可以根据本实用新型的技术方案和技术构思作出其他各种相应的改变和变形,而所有这些改变和变形都应属于本实用新型后附的权利要求的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。