技术特征:

1.一种锁相环即pll,其包括:第一相位检测器单元即第一pd单元,所述第一相位检测器单元具有第一参考频率输入、第一反馈输入和第一相位误差输出;所述第一pd被配置为产生具有第一增益极性的增益;第二pd单元,所述第二pd单元具有第二参考频率输入、第二反馈输入和第二相位误差输出;所述第一pd被配置为产生具有与所述第一增益极性相反的第二增益极性的增益;以及环路滤波器,所述环路滤波器具有滤波器输出,所述环路滤波器具有耦接到所述滤波器输出的积分路径和前馈路径;所述前馈路径具有第三pd单元,所述第三pd单元具有第三参考频率输入、第三反馈输入和ac耦接到所述滤波器输出的第三相位误差输出;所述积分路径包括运算放大器,所述运算放大器具有耦接到所述第一相位误差输出的反相输入和耦接到所述第二相位误差输出的非反相输入,所述运算放大器具有耦接到所述滤波器输出的输出。2.根据权利要求1所述的pll,还包括频率检测器,所述频率检测器具有第四参考输入、第四反馈输入和耦接到所述运算放大器的所述反相输入的频率检测器输出。3.根据权利要求1所述的pll,其中所述第一pd单元、所述第二pd单元和所述第三pd单元包括各自具有rc节点的相应电阻器-电容器充电电路即rc充电电路,其中每个rc节点耦接到相应第一pd单元、第二pd单元和第三pd单元的所述相位误差输出。4.根据权利要求3所述的pll,其中所述第一pd单元、所述第二pd单元和所述第三pd单元中的每一者包括耦接到相应rc节点的电荷泵。5.根据权利要求4所述的pll,其中至少所述第一pd单元包括耦接在第一rc节点和第二rc节点之间的第一开关,所述开关由第一门信号控制,其中所述第一rc节点通过第二开关耦接到所述滤波器输出,并且所述第二rc节点通过由第二门信号控制的第三开关耦接到所述滤波器输出,由此所述第一门信号在所述第二门信号之前启用。6.根据权利要求1所述的pll,其中所述第一pd单元、所述第二pd单元和所述第三pd单元各自包括异或电路,所述异或电路具有分别耦接到相应pd单元的所述第一参考输入、所述第二参考输入和所述第三参考输入以及所述第一反馈输入、所述第二反馈输入和所述第三反馈输入的输入。7.根据权利要求3所述的pll,还包括脉冲生成电路,所述脉冲生成电路具有参考频率输入和反馈输入,其中所述脉冲生成电路具有可控制地耦接到所述第一pd单元、所述第二pd单元和所述第三pd单元的所述rc充电电路的脉冲输出。8.根据权利要求1所述的pll,还包括电压控制振荡器即vco,所述电压控制振荡器具有控制输入和vco输出,所述控制输入耦接到所述滤波器输出。9.根据权利要求8所述的pll,还包括:除法器,所述除法器具有输入、分频值输入和输出,所述除法器的所述输入耦接到所述vco输出;数字到时间转换器即dtc,所述数字到时间转换器具有输入和输出,所述dtc的所述输入耦接到所述除法器输出,所述dtc输出耦接到所述第一反馈输入、所述第二反馈输入和所述第三反馈输入;以及

德尔塔-西格马调制器,所述德尔塔-西格马调制器具有时钟输入和输出,所述德尔塔-西格马调制器的所述时钟输入耦接到所述除法器输出,并且所述德尔塔-西格马调制器的所述输出耦接到所述分频值输入。10.一种相位检测器单元,其包括:脉冲生成电路,所述脉冲生成电路具有参考频率输入、反馈输入,以及第一脉冲信号输出和第二脉冲信号输出,其中所述第一脉冲信号输出和所述第二脉冲信号输出被配置为指示参考频率信号和反馈信号之间的相位关系;第一电阻器-电容器充电电路即第一rc充电电路,所述第一电阻器-电容器充电电路具有第一rc节点,其中所述第一rc充电电路通过第一开关耦接到第一电压参考并且所述第一rc节点耦接到相位检测器单元即pd单元的输出,其中所述第一开关可控制地耦接到所述第一脉冲信号输出;第二rc充电电路,所述第二rc充电电路具有第二rc节点,其中所述第二rc充电电路通过第二开关耦接到第二电压参考并且所述第二rc节点耦接到所述pd单元的所述输出;第一电荷泵,所述第一电荷泵具有耦接到所述第一rc节点的输出,所述第一电荷泵具有耦接到所述第一脉冲信号输出的第一控制输入;以及第二电荷泵,所述第二电荷泵具有耦接到所述第二rc节点的输出,所述第二电荷泵具有耦接到所述第二脉冲信号输出的第二控制输入。11.根据权利要求10所述的相位检测器单元,其中所述pd单元包括耦接在所述第一rc节点和所述第二rc节点之间的第三开关,其中所述第一rc节点通过第四开关耦接到所述滤波器输出并且所述第二rc节点通过第五开关耦接到所述滤波器输出。12.根据权利要求11所述的相位检测器单元,其中所述定时电路具有针对门信号的输出,并且其中所述第三开关、第四开关和第五开关由所述门信号控制。13.根据权利要求11所述的相位检测器单元,其中所述定时电路具有针对第一门信号和第二门信号的输出,并且其中所述第三开关由所述第一门信号控制,所述第四开关和第五开关由所述第二门信号控制,并且由此所述第一门信号在所述第二门信号之前启用。14.一种操作锁相环即pll的方法,所述方法包括:利用具有增益极性的第一相位检测器单元,生成针对参考信号和反馈信号之间的相位差的第一相位误差信号;利用具有相反增益极性的第二相位检测器单元,生成针对所述参考信号和所述反馈信号之间的相位差的第二相位误差信号;放大所述第一相位误差信号和所述第二相位误差信号并且组合结果以形成积分相位误差信号。15.根据权利要求14所述的方法,还包括利用第三相位检测器单元生成针对所述参考信号和所述反馈信号之间的相位差的第三相位误差信号以形成前馈相位误差信号;以及组合所述前馈相位误差信号和所述积分相位误差信号以形成控制信号。16.根据权利要求15所述的方法,还包括:响应于所述控制信号而操作电压控制振荡器即vco以生成输出信号;确定所述输出信号的频率是否在目标频率范围之外;以及当所述输出信号的所述频率在所述目标频率范围之外时,调整所述积分相位误差信号

的量值。17.根据权利要求16所述的方法,还包括:利用德尔塔-西格马调制器来调制耦接到所述vco的除法器的输出;以及响应于所述除法器的经调制的输出而使所述反馈信号延迟变化的量。18.根据权利要求14所述的方法,其中生成所述第一相位误差信号还包括:在与第一相位差成比例的时间量内将第一电压施加到第一电阻器-电容器以形成第一rc节点电压,其中所述电压的量值由第一电荷泵加强;以及在与第二相位差成比例的时间量内将第二电压施加到第二电阻器-电容器以形成第二rc节点电压,其中所述电压的量值由第二电荷泵加强。19.根据权利要求18所述的方法,还包括:组合所述第一rc节点电压和所述第二rc节点电压以形成组合的rc节点电压;以及将所述组合的rc节点电压传递到滤波器。20.根据权利要求19所述的方法,还包括使所述组合的rc节点电压到所述滤波器的所述传递延迟达一时间段以便允许所述组合的rc节点电压稳定。

技术总结

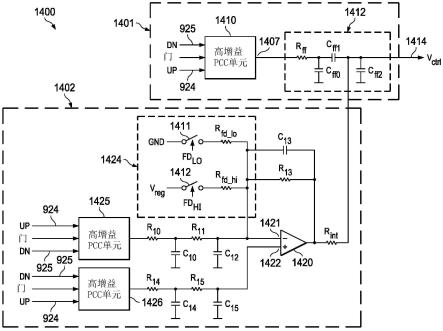

本申请涉及用于高带宽低噪声锁相环的高增益检测器技术。在所描述的示例中,锁相环(PLL)(1400)具有第一相位检测器单元(PD)(1424),其具有增益极性。第一PD单元具有相位误差输出以及耦接到参考频率信号和反馈信号的输入。第二PD单元(1426)具有相反增益极性。第二PD单元具有相位误差输出以及耦接到参考频率信号和反馈信号的输入。环路滤波器(1412)具有耦接到滤波器的输出(1414)的(有损)积分路径(1402)和前馈路径(1401)。前馈路径具有第三PD单元(1410),其具有AC耦接到滤波器输出的相位误差输出。积分路径包括运算放大器(1420),其具有耦接到第一PD单元相位误差输出的反相输入(1421)和耦接到第二PD单元相位误差输出的非反相输入(1422)。差输出的非反相输入(1422)。差输出的非反相输入(1422)。

技术研发人员:M

受保护的技术使用者:德克萨斯仪器股份有限公司

技术研发日:2021.12.31

技术公布日:2022/7/19

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。