用于低带宽低噪声锁相环的高增益检测器技术

1.相关申请的交叉引用

2.本技术要求2021年1月12日提交的美国临时专利申请no.63/136,245的 优先权,该申请的整体通过引用并入本文。

技术领域

3.本技术涉及用于低噪声反馈环路的高增益相位检测器技术。

背景技术:

4.通过高增益相位检测器(pd)技术,实现了锁相环(pll)或相关反馈 结构的低相位噪声操作。高增益pd允许实现低检测器噪声,这通常是在低频 偏移下实现低相位噪声的关键瓶颈。

5.存在用于实现高增益pd功能的若干技术。示例是基于斜率的采样pd结 构,例如,参见:“a 28-nm 75-fsrms analog fractional-n sampling pll with ahighly linear dtc incorporating background dtc gain calibration andreference clock duty cycle correction,”wanghua wu et al,2019。另一个示例是 利用up/dn定时窗口的有限时间范围的up/down电阻器-电容器(rc)充电 电路,例如参见:“a low area,switched-resistor based fractional-n synthesizerapplied to a mems-based programmable oscillator phase detector,”michael h. perrott,et al,2010。基于斜率的采样pd结构提供高增益,但由于斜率将通常 会受到pt变化的影响而承受该增益的工艺和温度(pt)敏感性。up/dn rc 充电电路提供了通常对pt变化具有稳健性的增益,但通常比基于斜率的结构 更受电源电压的限制。这两种方法都对电源噪声敏感。

技术实现要素:

6.在所描述的示例中,反馈环路包括全差分环路滤波器结构,其增益由具 有相反增益极性的高增益相位检测器馈送以用于电源抑制。在某些示例中, 差分输出馈入差分或伪差分adc。在一些示例中,反馈环路用具有死区的 bang-bang检测器来加强以便扩展相位误差范围以用于更快地锁相。

7.在所描述的用于低带宽应用的示例中,增强型德尔塔-西格马调制器用于 减小低频下的量化噪声而不显著影响高频下的整形噪声。

附图说明

8.图1是示例锁相环(pll)的框图。

9.图2是图1的pll的示例噪声模型。

10.图3-图5是图2的噪声模型的相位噪声水平(dbc/hz)相对于偏移频率 (f)的曲线图。

11.图6a是现有技术的相位检测器和环路滤波器的示意图并且图6b是其时 序图。

12.图7a是另一个现有技术的相位检测器的示意图并且图7b是其时序图。

13.图8a是另一个现有技术的相位检测器的示意图并且图8b是其时序图。

14.图9a是示例高增益相位检测器的示意图并且图9b是其时序图。

15.图10是图9a的相位检测器的等效电路的示意图。

16.图11a是没有电荷泵升压的示例相位到电荷转换器的示意图并且图11b 是其时序图。

17.图12是示出在图9a的相位检测器中提供的电荷泵结构的效果的时序图。

18.图13a是另一个示例高增益相位检测器的示意图并且图13b是其时序图。

19.图14是示例差分高增益相位检测器和环路滤波器的示意图。

20.图15是简单异或相位检测器的示意图。

21.图16是示例异或差分高增益相位检测器和环路滤波器的示意图。

22.图17是示例相位检测器和频率检测器电路的示意图。

23.图18是示出图17的示例电路的操作的时序图。

24.图19是示出示例pll中的相位噪声的曲线图。

25.图20是pll的示例电压源的框图。

26.图21是图20的电源的噪声相对于频率的曲线图。

27.图22是具有高增益相位检测器的示例反馈环路的框图。

28.图23是示出图22的反馈环路内的高增益相位检测器的操作的时序图。

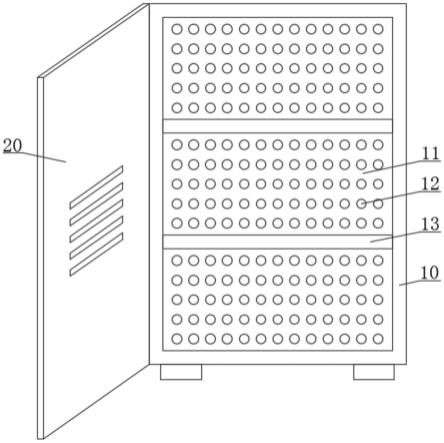

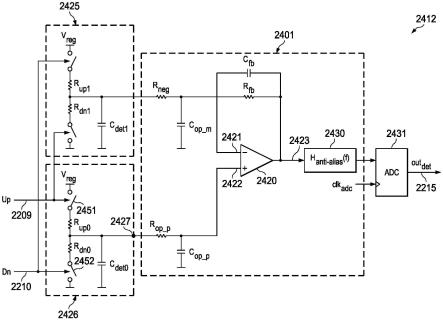

29.图24是低bw反馈环路的示例相位到数字转换器的示意图。

30.图25是图24的电阻器开关区段的仿真模型。

31.图26是低bw反馈环路的示例全差分相位到数字转换器的示意图。

32.图27是低bw反馈环路的另一个示例全差分相位到数字转换器的示意 图。

33.图28是示例替代开关式电阻器相位到电荷转换器的示意图。

34.图29是示例替代开关方案的示意图。

35.图30是示出示例相位到数字转换器的示例可配置性选项的示意图。

36.图31是用于生成早/晚脉冲的示例电路的框图并且图32是其时序图。

37.图33-图36是示例线性相位检测器的示意图和时序图。

38.图37a-图37e是示出具有线性相位检测器定时的示例bang-bang定时的 时序图。

39.图38是用于生成bang-bang信号的示例电路的示意图。

40.图39是示例2阶mash德尔塔-西格马调制器的框图。

41.图40是示例增强型2阶mash德尔塔-西格马调制器的框图。

42.图41是图40的示例增强型德尔塔-西格马的示例噪声模型。

43.图42是示出图40的增强型德尔塔-西格马的仿真结果的曲线图。

44.图43是由图22的反馈环路控制的示例模拟锁相环的框图。

45.图44是由数字pll加强的图43的示例模拟锁相环的框图。

46.图45是示出图2的示例噪声模型的仿真操作的相位噪声水平(dbc/hz) 相对于偏移频率的曲线图。

47.图46是示出图43的示例系统4300的仿真操作的相位噪声水平(dbc/hz) 相对于偏移频率的曲线图。

48.图47a、图47b是示出示例bang-bang电路的操作的曲线图。

具体实施方式

49.在附图中,为了一致性,类似的元件由类似的附图标记表示。

50.在本文所描述的示例中,通过高增益相位检测器(pd)技术,使得能够 实现锁相环或相关反馈结构在低偏移频率下的低相位噪声。具体地,高增益 pd允许实现减小检测器噪声的影响,这通常是在低频偏移下实现低相位噪声 的关键瓶颈。

51.在本文描述的其他示例中,通过实现pll的宽带宽(bw)以抑制电压控 制振荡器(vco)噪声,极大地有助于低噪声pll或相关反馈结构。然而, 宽bw pll受到相位检测器噪声的显著影响,并且因此必须实现低相位检测 器噪声以便实现低抖动。高增益相位检测器技术允许实现低检测器噪声影响。

52.虽然存在高增益pd技术,但它们通常对工艺和温度(pt)变化、电压 源噪声和/或有限电源电压(对于先进cmos中的核心设备,通常《1.2v)敏 感。由于pll带宽的对应改变,pd增益变化可跨pt变化劣化pll抖动性能。

53.电压源噪声可劣化低频相位噪声性能。虽然这种电源噪声可通过无源低 通滤波来减小,但此类滤波器需要大量的面积并且甚至可能需要包括不期望 的片外部件,诸如分立电容器。期望较低的电源电压以便减小功耗并且允许 使用先进cmos中的核心设备,但由于减小的pd增益而可能劣化pll性能。

54.存在用于实现高增益pd功能的若干技术。一个示例是基于斜率的采样 pd结构。另一个示例是利用up/dn定时窗口的有限时间范围的up/down电 阻器-电容器(rc)充电电路。基于斜率的采样pd结构提供高增益,但由于 斜率将通常受到pt变化的影响而承受该增益的pt敏感性。up/dn rc充电电 路提供了通常对pt变化具有稳健性的增益,但通常比基于斜率的结构更受电 源电压的限制。这两种方法都对电源噪声敏感。

55.在本文描述的示例中,高增益pd技术通过利用差分结构来减小对电源噪 声的敏感性。在另一个示例中,描述了一种用于加强德尔塔-西格马调制器以 减小其低频量化噪声而不显著增加高频量化噪声的技术,这有助于改进低频 相位噪声性能而不会由于相位检测器的非线性而引起附加的噪声折叠(noisefolding)。在另一个示例中,数字到时间转换器被用作用于减小量化噪声的替 代方案,其益处是实现更宽的带宽,但以更高的复杂性、功率和面积为代价。

56.本文描述的示例基于对up/dn rc充电电路方法的改进以实现更高的pd 增益并减小对电源噪声的敏感性。通过利用电荷泵技术来增加pd在up/dn 充电/放电时间期间见证的有效电源电压,实现了更高的pd增益。

57.通过可以与各种相位检测器技术组合的环路滤波器拓扑实现了对电源噪 声的较低敏感性。本文描述了示例环路滤波器拓扑的单端和差分版本。本文 描述的一些示例利用差分结构以便在保持pd的高增益的同时减小对电源噪 声的敏感性。在一些描述的示例中,包括adc以数字化差分信号。

58.通常,通过强力方法(诸如增加的功率/面积)来实现低噪声遇到由于产 品的功率/面积约束而引起的实际限制。在本文描述的示例中,用于增加pd 增益的技术利用电路拓扑,这些电路拓扑可通过适度的功率/面积要求来实现 并且使得能够满足当前发展水平

的抖动要求。通常可通过外部电容器实现对 低频电源噪声的不敏感,但由于最终系统的成本增加以及电路板设计中避免 噪声注入到与外部电容器相关联的路由迹线和引脚的困难,这是不期望的。 本文描述的示例使用了用于减小电源敏感性的技术,这些技术避免了对此类 外部电容器的需要。

59.图1是示例锁相环(pll)100的框图。电压控制振荡器(vco)108在 振荡器输出节点122上输出根据控制电压107调谐的可变频率信号。反馈用 于通过使用多模频率除法器(multi-modulus frequency divider,mmd)110、 相位检测器(pd)102和环路滤波器106将vco输出频率锁定为参考频率输 入信号120的倍数。在该示例中,相位检测器102还包括频率检测(fd)逻 辑104。相位检测器102包括脉冲生成(pg)逻辑103,该脉冲生成(pg) 逻辑103产生上行(up)脉冲和下行(dn)脉冲,其脉冲宽度随参考频率120 (ref)和除法器(div)输出121之间的相位差而变化。相位到电荷转换器 (pcc)105将上行pd信号和下行pd信号转换成脉冲,该脉冲然后由环路 滤波器106滤波以形成控制电压107。pcc 105被配置为提供pd 102的高增 益。

60.利用数字到时间转换器(dtc)112来减小来自德尔塔-西格马调制器114 的量化误差(除法器110的颤动(dithering))以便避免由于高增益pd 102的 非线性引起的噪声折叠。在一些示例中,dtc 112允许相位调整。dtc 112 产生由德尔塔-西格马114和mmd 110提供的数字输入值确定的可变延迟。 mmd 112的分频值由德尔塔-西格马114控制。mmd 110的输出用作德尔塔

‑ꢀ

西格马114的时钟输入和dtc 112的输入。

61.在一些示例中,多模除法器110的除数值可以被动态地改变。

62.图2是图1的pll的示例噪声模型200。图3是图2的噪声模型的原始 相位噪声水平(dbc/hz)相对于偏移频率(f)的曲线图。图3是在pll 100 (图1)内的滤波之前的相位噪声水平的曲线图。图4是在pll 100(图1) 内的滤波之后的相位噪声水平的曲线图。该示例模型包括相位检测器202、环 路滤波器206、vco 208和除法器210。k

d 202是相位检测器102的增益。 h(s)206是环路滤波器106的传递函数。(2πkv)/s 208是vco 108的传递函数。 n是除法器110的除法器值。

63.各种噪声源导致环路性能的劣化,诸如:相位检测器(det)噪声221、 来自除法器的量化噪声、dtc热噪声和德尔塔-西格马颤动噪声223、未被消 除的一些残余噪声、电源噪声等。电源噪声影响所有块,但尤其是相位检测 器和环路滤波器的问题。德尔塔-西格马调制器114致使噪声223上升到可由 环路滤波器206滤波的较高频率。vco噪声222通过环路被高通滤波,但一 些低频噪声通过。相位检测器202由环路滤波器206进行低通滤波,但一些 高频噪声通过。

64.如图4所示,在通过pll 100滤波之后,检测器噪声421主要在于相对 于301所示的pll带宽的低频偏移。vco噪声422主要在于高频偏移。dtc 和ds噪声422由于由pll的滤波而减小。

65.参照图2,表达式(1)量化从检测器噪声到输出端子122上的输出信号 的传递函数关系。对于其中s远小于pll带宽(bw)的情况,表达式(1) 可被简化为表达式(2)。

[0066][0067]

因此,检测器噪声421大约等于n/kd,因此,最大化检测器增益kd导 致最小化检测器噪声对输出122的影响。

[0068]

图5示出了如果pll 100中不包括dtc 112(参见图1)则可能发生的噪 声折叠。在没有dtc 112的情况下,相位检测器102中的非线性导致德尔塔

‑ꢀ

西格马噪声423的噪声折叠,如523处指示的。通过使用dtc 112避免了这 种噪声折叠,该dtc减小德尔塔-西格马调制器114(参见图1)的颤动对相 位误差的影响。

[0069]

图6a是用于诸如锁相环的反馈结构的现有技术相位检测器601和环路滤 波器602的示意图。相位检测器601生成上行脉冲信号624和下行脉冲信号 625,其宽度是参考频率信号620和反馈分频信号621之间的相位差的函数, 如图6b所示。

[0070]

电荷泵626响应于上行脉冲信号624而导通,并且电荷泵627响应于下 行脉冲信号625而导通。电荷泵626、627被添加以允许对形成在节点628上 的vco调谐电压进行上行控制或下行控制。表达式(3)表示从电荷泵的输 出到vco调谐电压628的环路滤波器传递函数h(s)。通常,较大电荷泵电流 (其有利于改进的检测器噪声)必须伴随着环路滤波电容器的增加以获得给 定pll带宽。这通常导致对大型物理电容器的要求,这些电容器通常必须位 于芯片外,这对于集成单芯片解决方案来说是不期望的。

[0071][0072]

图7a是用于诸如锁相环的反馈结构的现有技术相位检测器701和环路滤 波器的示意图,其不使用电流源来增加相位检测器增益。相反,增加参考信 号周期(tref)与分频反馈信号周期(tdiv)的比率。在该示例中,选择除数 以使得反馈分频信号721的频率是参考信号720的频率的四倍。相位检测器 701在较小相位窗口上看到相位误差范围,并且由于小相位误差范围,对应的 相位检测器增益增加。在该示例中,由于4倍的频率比率,存在4倍的改进。 这提供了相对稳定的相位检测器增益,因为tref/tdiv比率是pvt不敏感的。 然而,该相位检测器和环路滤波器方法对电源电压(vdd)噪声非常敏感,并 且由于来自环路滤波器内的rc充电行为的非线性,对于分数n实施方式存 在噪声折叠的一些影响。

[0073]

相位检测器701生成上行脉冲信号724和下行脉冲信号725,其宽度是参 考频率信号720和反馈分频信号721之间的相位差的函数,如图7b所示。

[0074]

相位检测器701是基于具有电阻器r1和电容器c1的rc充电机构。当 上行信号724有效时,电容器c1经由电阻器r1来充电。当下行信号725有 效时,c1被放电。当不存在上行或下行时,则电容器c1保持电压。

[0075]

图8a是另一个现有技术的开关式相位检测器801和环路滤波器802的示 意图并且图8b是其时序图。在该示例中,为了简单起见,仅详细示出相位检 测器的相位到电荷模块

805。脉冲生成模块803生成图8b中示出的脉冲信号。 在该示例中,单独的上行电荷电阻器rup和下行电荷电阻器rdn连接到充电 节点828和充电电容器cdet。在该示例中,相位检测器包括脉冲生成电路803 以生成上行脉冲信号824、下行脉冲信号825和门信号826。

[0076]

在该示例中,除法器被配置为提供具有比参考信号820的频率低的频率 的分频反馈信号821。如在图7a的示例中,由于fref/fdiv的比率,相位检测 器的增益增加。

[0077]

开关830由门信号826控制以仅在有限时间段内将电荷从rc节点828 传递到环路滤波器802。相位检测器增益的所得增加减小了从相位到电荷转换 器805传递到环路滤波器802的噪声的影响。

[0078]

在“a low area,switched-resistor based fractional-n synthesizer appliedto a mems-based programmable oscillator phase detector,”michael h.perrott, et al,2010中更详细地描述了相位检测器701(图7a)和802。

[0079]

高带宽、高增益相位检测器示例

[0080]

图9a是开关式电阻器相位检测器901和环路滤波器902的示意图。在该 示例中,利用改变rc充电的结构来改进相位检测器901的增益。相位检测器 增益受电源电压的限制。如果使用较大的电源电压,增益可增加。然而,由 于过电压问题,工艺限制了在没有设备问题的情况下的电源电压的量值。在 该示例中,通过使用加强相位检测器的电压升压结构926、927(也称为“电 荷泵”)来提高rc充电电路上的“有效”电源电压。为此,电容器cup2和 cdn2与反相器926和927一起被添加,以便在up和dn信号的断言(assertion) 期间分别向电容器cup1和cdn1注入附加电荷。这种额外电荷的注入对rc 充电具有类似效果,就像用较高的电源电压所实现的那样。额外开关932允 许在up和dn充电事件发生之后共享up和dn网络电荷状态。开关933和 934将组合的up和dn电荷状态传递到电容器c1,使得实现相位误差电压信 号(vfilt),该信号可以在影响vco控制电压vctrl之前被进一步滤波。

[0081]

在所描述的示例中,电荷泵926、927分别使升压电容器cup2、cdn2上 的充电电压升压以增加相位检测器的增益。在另一个示例中,可使用将电流 推动到合适元件(诸如电感器)中的电荷泵结构来增加有效电源电压以便增 加相位检测器的增益。

[0082]

图9b是示出由脉冲生成器模块903响应于参考信号920(ref_xn)和反 馈信号921(div)而生成的定时信号924、925、926的时序图。上行脉冲924 的持续时间与参考信号920和反馈信号921的边沿之间的时间成比例。下行 脉冲925的持续时间与参考信号920和反馈信号921的边沿之间的时间成比 例。上行脉冲924和下行脉冲925的总长度被约束为参考信号的周期tspan。

[0083]

例如,当下行脉冲925变得被断言并且开关931闭合时,反相器927的 输出将转变到高电压状态,并且由此经由vdn rc节点937通过电阻器rdn 到接地对电容器cdn2充电,并且还与电容器cdn1共享电荷。然后,当上行 脉冲924被断言并且开关930闭合时,反相器926的输出将变低,并且由此 经由vup rc节点936从vreg通过电阻器rup对电容器cup2充电,并且还 与电容器cup1共享电荷。然后,当上行脉冲924和下行脉冲925被去断言(de-asserted)并且开关930、931断开时,门脉冲926被激活以闭合开关932、 933和934并且由此将rc节点936、937耦接到相位误差输出节点928处的 滤波电容器c1。

[0084]

在该示例中,为了简单起见,仅详细示出相位检测器901的相位到电荷 转换器905。脉冲生成模块903生成图9b中示出的脉冲信号。脉冲生成电路 903生成上行脉冲信号

924、下行脉冲信号925和门信号926。在该示例中, 仅从参考信号920的上升沿到分频信号921的上升沿启用下行脉冲信号925, 并且仅从分频信号921的上升沿到参考信号920的上升沿启用上行脉冲信号 924。以这种方式,上行脉冲信号924和下行脉冲信号925是不重叠的,并且 具有等效于参考信号920的周期(tspan)的总有效时间。

[0085]

在该示例中,除法器被配置为提供具有比参考信号920的频率低的频率 的分频反馈信号921。由于fref/fdiv的比率,相位检测器的增益增加。

[0086]

开关933、934由门信号926控制以便在门信号926有效时的有限时段内 将电荷从rc节点936、937传递到输出节点928。这防止相位误差电压vfilt 以及vco控制电压vctrl在启用上行脉冲和下行脉冲期间受到rc充电活动 的干扰。

[0087]

当门开关932、933、934断开时,启用上行脉冲924和下行脉冲925。相 位检测器增益通过阿尔法因子得到改进,该阿尔法因子是由表达式(4)方程 给出的电容器的比率。表达式(5)表示假定电容器cup1和cdn1的值相等并 且电容器cup2和cdn2的值也相等时的相位检测器901的总增益因子。

[0088][0089][0090]

在一些示例中,可提供多个电容器,该多个电容器可使用开关、多路复 用器或其他已知或后来开发的技术来选择性地关断,以通过改变电容器比率 阿尔法来动态地改变系统的增益以便优化增益。如果只考虑检测器噪声的影 响的最小化,则阿尔法应被选择为尽可能高的。然而,诸如实施区域、具有 电容性负载的反相器926和927的可实现开关速度,以及对电源的影响等其 他考虑因素可影响阿尔法的最佳设置。

[0091]

图10是图9a的相位检测器901的相位到电荷转换器905的等效电路1005 的示意图。如图9a所述,电荷泵结构926、927和cup2、cdn2产生等效于 提高电源电压的效果。在该示例中,结果与以下相同:电源电压升高等于α

det

乘以电源电压的一半的量并且接地电压降低等于α

det

乘以电源电压的一半的 量。在该示例中,相位检测器901的电源电压是经调节的电压vreg。在其他 示例中,相位检测器的电源电压可以是芯片宽度电源电压vdd或另一个不同 电压源。在该示例中,电荷泵结构926、927和cup2、cdn2的使用允许有效 地增加相位检测器增益,如由电容器比率α

det

确定的。

[0092]

图11a是示例相位到电荷转换器(pcc)1105的示意图并且图11b是其 时序图,该相位到电荷转换器与没有电荷泵结构926、927的pcc 905(图9a) 类似。在没有增益提升电荷泵的该示例中,对于上行路径和下行路径,在上 行脉冲924期间的vup节点1136处的放电和在下行脉冲925期间的vdn节点 1137处的放电在约vreg/2处开始。在输出节点1128上形成所得的vfilt信号。

[0093]

图12是示例pcc 905的时序图,示出电荷泵结构926、927和cup2、cdn2 的效果。在该示例中,增益提升是通过在上行脉冲924和下行脉冲925的启 用时间期间增加rup、rdn电阻器两端的初始电压来实现的,如分别在1242、 1243处的vup 936和vdn 937上指示的。对

于给定的相位误差改变,这导致 vfilt 928的幅度的较大改变。因此,具有电荷泵结构926、927和cup2、cdn2 的pcc 905比没有电荷泵结构的pcc 1105具有更高的增益。

[0094]

图13a是类似于pcc 905(图9a)的另一个示例高增益相位到电荷转换 器(pcc)1305的示意图。在该示例中,门932由gate0信号13260控制,而 门933、934由偏移的gate1信号13261控制。

[0095]

图13b是示出由类似于pg 903(图9a)的脉冲生成器模块响应于参考 信号920(ref_xn)和反馈信号921(div)而生成的定时信号924、925、13260、 13261的时序图。gate0信号13260从gate1信号13261偏移小量,使得门932 稍微在门933、934之前闭合。这允许节点1336、1337上的纹波在闭合开关 933、934之前稳定,并且由此减小发送到滤波器1302和输出vctrl的纹波。 在该示例中,偏移时间约为tspan的5%-10%,但最佳偏移时间将根据开关 13260接通时的稳定行为以及其他约束而变化。应注意,gate0信号被示为在 gate1信号之前被去断言,但其他实施方式可在gate1信号的同时或之后使 gate0信号被去断言。

[0096]

图14是可用于图1的示例pll 100中的示例差分高增益相位检测器和环 路滤波器1400的示意图。在该示例中,宽带前馈(ff)路径1401包括耦接 到ff滤波器1412的高增益pcc单元1410。有损积分路径1402包括运算放 大器1420,其具有被耦接以接收来自pcc单元1425的经滤波的输出的反相 输入1421和被耦接以接收来自pcc单元1426的经滤波的输出的非反相输入 1422。

[0097]

有损积分路径1402还包括频率检测路径1424,其中开关1411被配置为 在输出信号(诸如输出信号122(图1))的频率太低的情况下,当信号fdlo 断言时,通过电阻器rfd_lo将反相输入1421耦接到接地,并且其中开关1412 被配置为在输出信号的频率太高的情况下,当信号fdhi断言时,通过电阻器 rfd_hi将反相输入1421耦接到vreg。

[0098]

ff滤波器1412组合pcc单元1410的输出1407和积分路径1402以在输 出节点1414上产生控制信号vctrl。控制信号vctrl用于控制输出信号信号122 (图1)的可变频率振荡器。在另一个示例中,可在控制信号vctrl在节点1414 上输出之前为其提供附加滤波。

[0099]

pcc单元1410、1425和1426可与pcc 905(图9a)、pcc 1005(图10)、 pcc 1105(图11b)、pcc 1305(图13a)或其他已知或后来开发的pcc单 元相同。然而,需注意,up信号924和dn信号925在pcc 1425和pvv 1426 之间是相反的。这允许消除低频电源噪声以及使用运算放大器1420的反相输 入1421和非反相输入1422两者。以这种方式,通过利用反相和非反相增益 路径两者,运算放大器1420的噪声影响减小到原来的约1/2。

[0100]

运算放大器的反相路径的dc增益对应于跨反馈的电阻与输入电阻器的 比率-(r13/(r10 r11)),而非反相路径的dc增益为(1 r13/(r10 r11))。在 反相路径的dc增益的量值显著大于1的情况下,则非反相路径的dc增益的 量值将具有类似的量值。因此,任何共模信号(诸如高增益pd单元1425和 1426中的电源噪声)将被很大程度地消除。例如,如果反相路径的dc增益 的量值为10,则非反相路径的dc增益的量值为1 10=11。在这种情况下, 假设电源噪声对高增益pd单元1425和1426两者具有相同的效果,电源噪声 将衰减约90%。因此,在单端系统(与差分双输出系统相反)中提供了良好 的电源噪声消除,这便于对vco进行模拟控制,因为vco通常具有单端控 制输入。

[0101]

此示例提供了低频的电源噪声消除的益处,并且有效地从运算放大器获 得更多增益。如果只使用反相端子,则增益为10(在本示例中),然而,在该 情况下,反相输入的增

益为-10并且非反相输入的增益为11,则与值21相比, 有损积分路径的总增益有效地加倍。因此,与仅使用反相或非反相路径相比, 运算放大器输出提供双倍的相位误差信号。这是重要的,因为来自运算放大 器的噪声是由非反相路径增益增加的,使得相对于非反相路径的相位误差信 号的增益的加倍导致运算放大器输出处的信噪比的约2倍的改进。实际上, 运算放大器噪声影响减小到原来的约二分之一。因此,该示例提供了通过积 分路径消除低频电源噪声的益处,以及减小系统中的运算放大器噪声的影响 的益处。

[0102]

在该示例中,每个pcc单元1410、1425、1426在1.1v的经调节的电压 vreg上操作。在另一个示例中,可使用不同的电源电压。每个pcc单元1410、 1425、1426和相关联的滤波器网络可以被单独地优化。

[0103]

在该示例中,积分路径1402被描述为“有损”积分器。为了避免饱和问 题,反馈电容器c13由反馈电阻r13分流。c13和r13的并联组合像耗散功 率的实际电容器运行,而不像理想的电容器。由于这个原因,实际积分器被 称为有损积分器。在另一示例中,可基于其他参数来选择由r13贡献的损耗 量以控制饱和。

[0104]

图15是简单异或相位检测器单元1500的示意图。在该示例中,参考信 号1520和分频反馈信号1521连接到异或门1501的输入。反馈信号1521类 似于pll 100(图1)的反馈信号121(图1)。反相缓冲器1504提供缓冲的 相位检测信号vpdb 1507。反相缓冲器1505提供相反相位检测信号vpd 1506。

[0105]

图16是使用图15的简单异或pd单元代替pcc单元的示例异或差分高 增益相位检测器1600的示意图。当高频参考信号(诸如ref 1520)可用时, 该结构是有用的。用于增加pd增益的一种方法是减少滤波后从pd获得给定 电压误差信号所需的时间范围,这是当pd的操作频率增加时的情况。典型参 考频率小于几百mhz,然而,在该示例中,参考振荡器以2.5ghz运行,而 vco以多个ghz运行。由于参考频率非常高,因此不需要其中参考频率和反 馈分频信号是彼此的倍数的pcc配置,并且可以替代地使用简单异或类型pd (诸如pd 1500(图15))。在该示例中,不需要增加pd增益;取而代之的是, 期望简单的实施方式以便允许在非常高的频率下进行稳健的操作。由于在稳 态操作期间避免了窄输出脉冲,因此在反馈环路中包括德尔塔-西格马调制的 系统中,异或pd提供了非常线性的行为,只要瞬时相位误差偏差不大到在 pd输出处创建非常小的脉冲即可。

[0106]

在该示例中,宽带前馈(ff)路径1601包括耦接到ff滤波器1412的 pd单元1610。有损积分路径1602包括运算放大器1420,其具有被耦接以接 收来自pd单元1425的经滤波的输出的反相输入1421和被耦接以接收来自 pd单元1426的经滤波的输出的非反相输入1422。

[0107]

有损积分路径1602还包括频率检测路径1424,其中开关1411被配置为 在输出信号(诸如输出信号122(图1))的频率太低的情况下,当信号fdlo 断言时,通过电阻器rfd_lo将反相输入1421耦接到接地,并且其中开关1412 被配置为在输出信号的频率太高的情况下,当信号fdhi断言时,通过电阻器 rfd_hi将反相输入1421耦接到vreg。

[0108]

ff滤波器1412组合pd单元1610的输出1507和积分路径1602以在输 出节点1614上产生控制信号vctrl。控制信号vctrl用于控制产生输出信号122 的可变频率振荡器。在另一个示例中,可在控制信号vctrl在节点1414上输 出之前为其提供附加滤波。

[0109]

在该示例中,pd单元1410、1425和1426与pd单元1500(图15)或另 一个已知或后来

开发的pd单元相同。然而,应注意,输出信号vpd 1506耦 接到运算放大器1420的反相输入1421,而相反极性输出信号vpdb 1507耦接 到非反相输入1422。这允许消除低频电源噪声以及使用运算放大器1420的反 相输入1421和非反相输入1422两者。以这种方式,通过利用反相和非反相 增益路径两者,运算放大器1420的噪声影响减小到原来的约1/2。

[0110]

运算放大器的反相路径的dc增益对应于跨反馈的电阻与输入电阻器的 比率-(r13/(r10 r11)),而非反相路径的dc增益为(1 r13/(r10 r11))。在 反相路径的dc增益的量值显著大于1的情况下,则非反相路径的dc增益的 量值将具有类似的量值。因此,任何共模信号(诸如高增益pd单元1425和 1426中的电源噪声)将被很大程度地消除。例如,如果反相路径的dc增益 的量值为10,则非反相路径的dc增益的量值为1 10=11。在这种情况下, 假设电源噪声对高增益pd单元1425和1426两者具有相同的效果,电源噪声 将衰减约90%。因此,在单端系统(与差分双输出系统相反)中提供了良好 的电源噪声消除,这便于对vco进行模拟控制,因为vco通常具有单端控 制输入。

[0111]

此示例提供了低频的电源噪声消除的益处,并且有效地从运算放大器获 得更多增益。如果只使用反相端子,则增益为10(在本示例中),然而,在该 情况下,反相输入的增益为-10并且非反相输入的增益为11,则与值21相比, 有损积分路径的总增益有效地加倍。因此,与仅使用反相或非反相路径相比, 运算放大器输出提供双倍的相位误差信号。这是重要的,因为来自运算放大 器的噪声是由非反相路径增益增加的,使得相对于非反相路径的相位误差信 号的增益的加倍导致运算放大器输出处的信噪比的约2倍的改进。实际上, 运算放大器噪声影响减小到原来的约二分之一。因此,该示例提供了通过积 分路径消除低频电源噪声的益处,以及减小系统中的运算放大器噪声的影响 的益处。

[0112]

在该示例中,每个pd单元1610、1625、1626在1.1v的经调节的电压 vreg上操作。在另一个示例中,可使用不同的电源电压。每个pd单元1610、 1625、1626和相关联的滤波器网络可被单独地优化。

[0113]

图17是示例相位检测器脉冲生成(pg)电路1701、频率检测器电路1702 和bang-bang相位检测器电路1703的示意图。提供参考频率信号120和分频 反馈信号121作为这些电路的输入。pg电路1701生成在上文更详细描述的 pcc单元中使用的相位检测器控制信号up 924、dn 925和gate 926。当振荡 器输出的频率在选定范围之外时,频率检测器1702生成上文更详细描述的 fdhi和fdlo信号以便实现pll的初始锁定。bang-bang pd电路1703用于 dtc校准并将在下文中更详细地描述。

[0114]

图18是示出图17的示例电路的pg部分1701的操作的时序图。在该示 例中,参考频率信号120的频率为1.25ghz。分频反馈信号121的频率为625 mhz,使得ref 120具有div 121的两倍的频率。在另一个示例中,可使用更 大的倍数并且也可使用更高的参考频率。ref 120和div 121之间的频率的两 倍差异提供了pd/pcc单元中的两倍增益的等效。替代地,在另一个示例中, div 121的频率可被配置为ref 120的频率的倍数。

[0115]

作为相位误差的函数,上行/下行脉冲924、925以相反方式改变宽度。即 使在up/dn环路滤波器路径之间存在不匹配的情况下,这种关系也提供了高 线性度。这与上行或下行脉冲独立地改变宽度的现有技术形成对比。

[0116]

图19是以dbc/hz表示的噪声相对于偏移频率(hz)的曲线图,示出了 示例pll中的噪声。在该示例中,pll 100(图1)配备有使用定时电路1701、 1702(图17)的pcc块和环路滤

波器电路1400(图14)。在该示例中,参考 频率为1.25ghz并且反馈频率为625mhz。如曲线图线1902所指示,来自 经调节的电源电压(vreg)的低频噪声被良好地抑制。总体噪声由曲线图线 1901指示。从12khz到20mhz积分的总体抖动为46.0fs(rms)。

[0117]

在所描述的示例中,描述了操作锁相环(pll)的方法。利用具有增益极 性的第一相位检测器单元1425(图14),针对参考信号和反馈信号之间的相 位差生成第一相位误差信号。利用具有相反增益极性的第二相位检测器单元 1426,针对参考信号和反馈信号之间的相位差生成第二相位误差信号。第一 相位误差信号和第二相位误差信号由运算放大器1420(图14)放大并组合结 果以形成积分相位误差信号。利用第三相位检测器单元1410(图14),针对 参考信号和反馈信号之间的相位差生成第三相位误差信号以形成前馈相位误 差信号。前馈相位误差信号与积分相位误差信号组合以形成控制信号vctrl1414(图14)。

[0118]

在所描述的示例中,响应于控制信号vctrl操作电压控制振荡器(vco) 108(图1)以生成输出信号out 122(图1)。连续监测输出信号的频率以确 定其是否在目标频率范围之外。当输出信号的频率在目标频率范围之外时, 调整积分相位误差信号vctrl的量值(值和/或符号)。

[0119]

在所描述的示例中,耦接到vco的除法器110(图1)的输出利用德尔 塔-西格马调制器来调制。反馈信号通过dtc 112(图1)响应于除法器的经 调制的输出而被延迟变化量。

[0120]

在所描述的示例中,通过在与第一相位差成比例的时间量内将第一电压 施加到第一电阻器-电容器rup、cup1(图9a)以形成第一rc节点电压来生 成第一相位误差信号,其中电压的量值由第一电荷泵926(图9a)加强。在 与第二相位差成比例的时间量内将第二电压施加到第二电阻器-电容器rdn、 cdn1(图9a)以形成第二rc节点电压,其中电压的量值由第二电荷泵927 (图9a)加强。通过闭合开关932(图9a)来组合第一rc节点电压和第二 rc节点电压以形成组合的rc节点电压。通过开关933、934(图9a)将组 合的rc节点电压传递到滤波器。在一些示例中,通过门信号13260、13261 (图13b)使组合的rc节点电压到滤波器的传递延迟达一时间段以允许组合 的rc节点电压稳定。

[0121]

低带宽、高增益相位检测器示例

[0122]

在以下示例中,差分开关式rc前端用于消除来自电压调节器的低频噪 声。差分前端与部分和全差分环路滤波器和adc(模数转换器)组合。环路 滤波器的增益被设置得足够高以使得adc噪声影响被充分减小。

[0123]

在一些示例中,线性pd利用bang-bang检测器和频率检测器来加强以获 得合理的锁定时间。

[0124]

在一些示例中,通过避免高频下的量化噪声频谱量值的显著增强,数字 德尔塔-西格马调制器被加强以减小低频下的量化噪声而不显著增加噪声折 叠。

[0125]

图20是示例pll的示例电压源的框图。在典型的pll系统中,电源电 压2001由诸如带隙电路的电路提供,该电路创建准确的参考电压vref。虽然 vref提供了跨pvt变化的合理一致的准确电压值,但它通常容易伴随高噪声 并且不能提供足够输出电流以作为集成电路内的包括pll的各种电路的电源 运行。因此,电压源调节器vreg 2003用于为pll和其他块提供足够的输出 电流,并且vref 2001被用作vreg的参考电压以便跨pvt实现准确电压。在 供应给vreg之前,vref中存在的噪声被滤波2002。因此,由于被低通滤波的 带隙噪声的影响,用于pll的典型电源调节器的输出噪声频谱密度噪声在低 频下最高。

[0126]

图21是图20的电压源调节器的噪声频谱密度(v/rhz)相对于频率(hz) 的示例曲线图,示出在较低频率下的vref噪声的影响。

[0127]

图22是在输出节点上提供数字频率比率信号“outn”的示例反馈环路 2200的框图,该数字频率比率信号是从高频体声波(baw)振荡器2201的 相位/频率与参考频率ftcxo的比较中导出的。具体地,节点2215上的输出信 号outn是baw输出信号2202的频率和参考信号2204的频率的估计瞬时比 率,在此示例中,该比率由温度控制晶体振荡器(tcxo)2203提供。以高 操作频率(高达几ghz)和小尺寸为特征的baw谐振器多年来一直用于移动 应用,诸如无线收发器的rf前端的滤波器。baw谐振器是压电薄膜谐振器 (其与石英晶体类似地操作),由baw振荡器电路用于创建周期振荡信号。 在该示例中,baw振荡器2204以2.5ghz操作。

[0128]

多模除法器(mmd)2206将baw频率信号2202除以由数字德尔塔-西 格马调制器2216提供的反馈信号2217的比数n。如图23所示,由mmd 2206 生成div_early和div_late脉冲。在该示例中,德尔塔-西格马调制器2216由 div_late脉冲2219钟控。

[0129]

响应于参考信号2204与div_early和div_late脉冲之间的定时关系,相位 检测器2208使用参考信号2204以及div_early和div_late脉冲来生成包括上 行脉冲2209和下行脉冲2210的相位差信号。

[0130]

相位到数字转换器(p2dc)2212响应于上行脉冲2209和下行脉冲2210 而产生数字输出值2213。数字环路滤波器2214对数字值2213进行滤波以在 节点2215上产生输出信号outn。

[0131]

在该示例中,通过下文中将更详细描述的“bang-bang”(bb)环路2220、 2221来改进初始锁定时间。bb环路在初始稳定时利用额外相位检测器加强系 统。bb环路提供误差信号以驱动系统。一旦系统锁定,bb环路在活动中退 出并且不影响噪声等。

[0132]

在该示例中,德尔塔-西格马2216被设计成减小德尔塔-西格马噪声影响 而不加剧噪声折叠,如下文将更详细地描述。

[0133]

图23是示出由mmd 2206(图22)和pd 2208(图22)生成的定时信号 的时序图。

[0134]

图24是用于诸如反馈环路2200(图22)的低bw反馈环路的示例p2dc 2412的示意图。

[0135]

模块2412包括以差分方式配置的开关式电阻器相位到电荷转换器(pcc) 2425、2426。每个pcc 2425、2426包括两个开关,诸如分别由上行脉冲信号 2209和下行脉冲信号2210控制的开关2451、2452。在该示例中,开关2451、 2452各自被实施为fet晶体管。

[0136]

差分环路滤波器2401包括运算放大器2420。pcc 2425的输出耦接到运 算放大器2420的反相输入2421,并且pcc 2426的输出耦接到运算放大器2420 的非反相输入2422。应注意,从pd 2208(图22)接收的信号up 2209和dn 2210在pcc 2425和2426之间反转。

[0137]

抗混叠滤波器2430使模数转换器(adc)2431的奈奎斯特(nyquist) 采样率以上的频率衰减以消除混叠。

[0138]

adc 2431将来自运算放大器2420的经放大的输出转换成在节点2215上 输出的数字值。此类数字值对于数字锁相环(dpll)是有用的。

[0139]

在该示例中,差分配置抑制经调节的电源电压vreg上的低频噪声并且减 小由运算放大器2420产生的噪声的影响,如针对运算放大器1420(图14) 更详细地描述的。

[0140]

图25是图24的电阻器开关区段(诸如开关区段2426)的仿真模型。等 效电阻器rdet 2501的值由表达式(6)给出,但该表达式是近似的,因为rdet 可通过图24中的网络2425和2426中的寄生电容的影响而减小。

[0141][0142]

对应于从相位误差到verror的dc增益的块2508指示相位检测器2412 的dc增益以参考信号2204(图22)的周期与div_early和div_late的上升沿 之间的时间跨度tspan的比率增加。

[0143]

由verror馈送的环路滤波器电路的dc增益基于表达式(7)作为参考 (tcxo)频率的函数改变,其中rdet由表达式(6)给出。参考信号2204 的较低频率导致增加的r

det

以及因此较低的dc增益。参考信号2204的较高 频率导致减小的r

det

以及因此较高的dc增益。

[0144]

环路滤波器的dc增益=1 2*r

fb

/(r

det

r

neg

)

ꢀꢀꢀꢀꢀ

(7)

[0145]

adc 2431(图24)的输入和运算放大器2420的输出各自具有有限的电 压范围。这导致有效相位误差分辨率和有效相位误差范围之间的折衷。有效 相位误差范围必须足够宽以适应抖动(包括德尔塔-西格马颤动)。有效相位误 差范围受adc运算放大器电压范围、pd增益和环路滤波器增益(表达式(7)) 的影响。

[0146]

图26是用于诸如反馈环路2200(图22)的低bw反馈环路的示例全差 分p2dc 2600的示意图。在该示例中,相位到电荷转换器(pcc)2425、2426 以差分方式配置并耦接到两个单独的运算放大器2420、2620。

[0147]

差分环路滤波器2601包括运算放大器2420和2620。pcc 2425的输出耦 接到运算放大器2420的反相输入2421,并且pcc 2426的输出耦接到运算放 大器2420的非反相输入2422。类似地,pcc 2425的输出耦接到运算放大器 2620的非反相输入2622,并且pcc 2426的输出耦接到运算放大器2620的反 相输入2621。应注意,从pd 2208(图22)接收的信号up 2209和dn 2210 在pcc 2425和2426之间反转。

[0148]

运算放大器2420的输出2423和运算放大器2620的输出2623耦接到差 分adc 2631的输入。adc 2631量化在信号线2423和2623上出现的电压差 并将其转换为数字输出。然后在输出节点2215上提供adc 2631的输出。adc2631可以是全差分或伪差分的。

[0149]

图27是用于诸如反馈环路2200(图22)的低bw反馈环路的示例全差 分p2dc 2700的示意图。在该示例中,利用包括单个差分运算放大器2720的 差分环路滤波器2701,相位到电荷转换器(pcc)2425、2426以差分方式配 置。pcc 2425的输出耦接到运算放大器2720的反相输入2721,并且pcc 2426 的输出耦接到运算放大器2720的非反相输入2722。运算放大器2720提供耦 接到差分adc 2631的差分输出2723、2724。adc 2631量化在信号线2723 和2724上出现的电压差并将其转换为数字输出。然后在输出节点2215上提 供adc 2631的输出。adc 2631可以是全差分或伪差分的。

[0150]

图28是示例替代开关式电阻器相位到电荷转换器的示意图。在该示例中, 具有单个电阻器rdet1的开关式pcc 2825可以替换具有两个电阻器rup1和 rdn1的pcc 2425。类似地,具有单个电阻器rdet0的开关式pcc 2826可以 替换具有两个电阻器rup0和rdn0的pcc 2426。该替代配置可用于前面描述 的系统2412、2600或2700中的任一者。

[0151]

图29是用于pcc 2426(参见24)的示例替代开关方案的示意图。在pcc2425中(图24)可使用类似的配置。在该示例中,缓冲器2951插入在开关 fet 2451和vreg之间并跟踪up信号2209。在该配置中,提供给开关晶体管 2451的电源电压由缓冲器2951的输出提供。因此,当up信号2209无效时, 向开关2451提供近似处于接地电势的电压。类似地,缓冲器2952插入在开 关fet 2452和接地之间并且使dn信号2210反相。在该配置中,提供给开关 晶体管2452的电源电压由缓冲器2952的输出提供。因此,当dn信号2952 无效时,向开关2452提供近似为vreg电势的电压。以这种方式,开关电路 2951、2952的关断电阻显著增加。导通电阻仅由于缓冲器2951、2952的电阻 而略微增加。

[0152]

图30是示出示例pcc 3012的示例可配置性选项的示意图,其具有与示 例pcc 2412(图24)相同的总体示意图。保持足够高的环路滤波器增益以使 得adc 2413量化噪声被很好地加扰(即,使得至少若干adc码通过噪声或 其他信号执行(exercised))是有益的。参照表达式(6)和(7),环路滤波器 增益随参考频率的周期tref而变化。因此,当tref变化时,通过适当调整或 修整pcc 3012中的各种电阻器和电容器值来保持足够的环路滤波器增益是有 益的。

[0153]

在该示例中,rup0、rup1、rdn0、rdn1、rop_p、rneg、rfb、cdet0、 cdet1和cfb各自使用适当配置中的修整开关和附加电阻器和电容器(诸如串 联或并联连接修整部件)来个体调节。在该示例中,修整开关由配置寄存器 (未示出)控制,该配置寄存器由系统的控制处理器(未示出)设置。在另 一个示例中,修整可使用已知或后来开发的技术来控制,诸如:可熔链路、 可擦除可编程只读存储器(eprom)位等。

[0154]

图31是用于在图22所示的多模除法器2206中生成早/晚脉冲2218、2219 的示例电路3100的框图并且图32是其时序图。多级除法器拓扑3102提供从 div_in反馈信号2217(参见图22)重新定时的div_early输出脉冲信号2218。 在该示例中,利用可配置移位寄存器3104以将div_late输出脉冲信号2219 准确地延迟选定数量的div_in 2217脉冲。以这种方式,准确地设置div_early 2218的上升沿和div_late 2219的上升沿之间的时间长度tspan。在一些示例 中,移位寄存器3104可被配置为允许通过div_in反馈信号2217的半周期来 调整tspan。已知或以后开发的技术可与多路复用器和寄存器一起使用以控制 延迟寄存器3104的配置并由此选择tspan的值。

[0155]

图33是被包括在pd 2208(参见图22)内的示例线性相位检测器3300 的示意图并且图34是其时序图。在该示例中,触发器3302在时钟输入上接 收div_early 2218脉冲信号并且在重置输入上接收div_late 2219脉冲信号。 纯“1”逻辑电平应用于d输入。触发器3302生成耦接到门3304、3306上的 输入的pd_pulse信号3303。参考信号2204耦接到门3304的第二输入并且参 考信号2204的反相版本耦接到门3306的第二输入。“与”门3304生成下行 脉冲信号2210,而“与”门3306生成上行脉冲信号2209。在该示例中,包 括可选的延迟模块3308以将下行脉冲2210延迟一小量,使得上行脉冲和下 行脉冲不重叠。在该示例中,tdelay是使用反相器来实现的。在另一个示例 中,其他类型的已知或后来开发的技术或电路元件可用于产生延迟。在一些 示例中,如果重叠的上行/下行脉冲是可接受的,则可省略延迟3308。

[0156]

图35是被包括在pd 2208(参见图22)内的示例线性相位检测器3500 的示意图并且图36是其时序图。在该示例中,触发器3502在时钟输入上接 收参考信号2204,在d输入上

接收纯1逻辑电平,并且在重置输入上接收 div_early。触发器3502生成下行脉冲信号2210。触发器3504在时钟输入上 接收参考信号2204,在d输入上接收纯1逻辑电平,并且在重置输入上接收 div_late。触发器3504生成上行脉冲信号2209。在该示例中,包括可选的延 迟模块3508以将下行脉冲2210延迟一小量,使得上行脉冲和下行脉冲不重 叠。在该示例中,tdelay是使用反相器来实现的。在另一个示例中,其他类 型的已知或后来开发的技术或电路元件可用于产生延迟。在一些示例中,如 果重叠的上行/下行脉冲是可接受的,则可省略延迟3308。

[0157]

图37a-图37e是示出由pd 2208(图22)内的定时电路系统生成的示例 bang-bang(bb)定时信号以及线性相位检测器信号up和dn的时序图。如 图37b、图37c和图37d所示,只要参考信号2204的上升沿落在tspan窗口 3701内,bb late 2223和bb early 2222是无效的,该tspan窗口3701由 div_early脉冲2218的上升沿和div_late 2219的后续上升沿之间的时间定义。 图37a示出了其中参考信号2204的上升沿出现在tspan窗口3701之前的示 例情况。在这种情况下,bb early信号2222被激活。图37e示出了其中参考 信号2204的上升沿出现在tspan窗口3701之后的示例情况。在这种情况下, bb late信号2223被激活。因此,在该示例中,只要up信号2209和dn信号 2201都是有效的从而指示反馈环路2200(图22)是锁定的,则bb early和 bb late是无效的。应注意,存在一些情况,诸如遇到35的pd电路,up和 dn可在tspan窗口之外具有活动性,而不干扰bb early和bb late在tspan 窗口之外变得无效的关系。

[0158]

图38是被包括在pd 2208(图22)内以生成bang-bang信号的示例电路 的示意图。只要参考信号2204的上升沿落在tspan窗口3701(图37a)内, bb late 2223和bb early 2222是无效的,该tspan窗口3701由div_early脉冲 2218的上升沿和div_late 2219的后续上升沿之间的时间定义。

[0159]

假设西格马-德尔塔模块由div_late时钟信号2218钟控,对触发器3801、 3802重新定时将bb_early和bb_late的定时同步到div_late时钟信号2218。 假设adc 2431(图24)或adc 2631(图26或图27)模块由adc时钟信号 2226钟控,对触发器3803、3804重新定时将bb_early和bb_late的定时同步 到adc时钟信号2226。

[0160]

增强型数字德尔塔-西格马调制器

[0161]

如上文对于图1-图5所描述的,如果dtc 112(参见图1)不被包括在 pll 100中,则可能发生噪声折叠。在没有dtc 112的情况下,相位检测器102中的非线性导致德尔塔-西格马噪声223的噪声折叠,如523(图5)处指 示的。通过使用dtc 112避免了这种噪声折叠,该dtc减小德尔塔-西格马 调制器114(参见图1)的颤动对相位误差的影响。dtc 112减小进入相位检 测器102(图1)的相位变化,并且还允许宽带宽操作。然而,dtc添加集成 电路的复杂性、功耗和面积。

[0162]

德尔塔-西格马(δσ;或西格马-德尔塔、σδ)调制是用于将模拟信号编 码成数字信号的方法,如在模数转换器(adc)中发现的。它还用于将具有 相对低频率内容的高位计数数字信号转换成其中保留相对低频率内容的较低 位计数较高频率数字信号。例如,作为数模转换器(dac)以及分数n频率 合成器的一部分,数字信号到模拟信号的转换可利用德尔塔-西格马调制。德 尔塔-西格马调制技术是已知的,例如参见:“德尔塔-西格马调制”,维基百科, 2021年8月9日或更晚。

[0163]

图39是2阶mash数字德尔塔-西格马调制器3901的框图。多级噪声整 形(mash)数字结构具有噪声整形属性并且通常用于数字音频和分数n频 率合成器。它包括两个或更多个级联溢出累加器,累加器中的每一者相当于 一阶西格马-德尔塔调制器。进位输出通过求和以及延迟进行组合以产生二进 制输出,其宽度取决于mash的级(阶)数。

[0164]

诸如pcc 2212(图22)的高增益pcc的rc充电具有非线性,该非线性 导致由德尔塔-西格马模块2216(图22)产生的德尔塔-西格马噪声的噪声折 叠。2阶mash德尔塔-西格马3901通常产生可接受的低噪声折叠,但没有 充分的噪声整形。然而,3阶德尔塔-西格马通常产生不可接受的高噪声折叠。

[0165]

图40是示例增强型2阶mash德尔塔-西格马调制器4001的框图。在该 示例中,2阶mash德尔塔-西格马3901通过使用设计参数“k”和“a”的 反馈环路得到增强。在该示例中,反馈块4009用作数字低通滤波器,该数字 低通滤波器提取低频量化噪声以使得通过反馈的作用可抑制低频量化噪声。 所得的反馈导致闭环系统的dc增益的改变,其由级联增益块4007补偿。

[0166]

图41是图40的示例增强型德尔塔-西格马调制器4001的示例噪声模型。 在该示例中,表达式(8)表示德尔塔-西格马量化噪声4010到输出节点4005 的传递函数。总体德尔塔-西格马噪声谱由表达式(9)表示,其中“n”是德 尔塔-西格马的mash阶。从输入4003到输出4005的信号传递函数由表达式 (10)表示。

[0167][0168]

sq(z)=1/12*|hq(z)|2|1_z-1

|

2n

ꢀꢀꢀꢀꢀꢀ

(9)

[0169][0170]

图42是示出与常规的2阶和3阶mash结构相比的图40的增强型德尔 塔-西格马的仿真结果(以db/hz为单位)相对于频率(mhz)的曲线图。曲 线图线4201表示2阶mash德尔塔-西格马3901(图39)。曲线图线4202表 示增强型2阶mash德尔塔-西格马4001(图40)。曲线图线4203表示3阶 mash德尔塔-西格马(未示出)。

[0171]

在该示例中,k被选择为3并且被设置为在反馈环路4009(图40)中实 现时钟频率的约1/100的低通带宽。在该示例中,高频噪声保持大致相同,但 在较低频率下观察到约9db的改进。

[0172]

锁相环示例

[0173]

图43是包括由图22的低带宽反馈环路2200控制的高带宽模拟锁相环 4301的示例频率生成系统4300的框图。高bw pll 4301类似于高bw pll100(图1)。在该示例中,高bw pll 4301被锁定到由提供高频和低抖动的 baw振荡器2201所提供的参考频率fbaw 2202。在该示例中,为了简单起见, 除法器4302将高频参考信号2202除以4,但可以应用所讨论的高增益pd技 术并且因此导致该分频值的最佳选择的改变。在另一个示例中,参考频率可 由另一个已知或后来开发的技术提供,诸如基于晶体的参考振荡器。

[0174]

在该示例中,低bw反馈环路2200还被锁定到fbaw参考频率信号2202 和由温度控制晶体振荡器提供的ftcxo参考频率信号2204。在另一个示例中, 参考频率可由另一个已知或后来开发的技术提供,诸如基于晶体的参考振荡 器。

[0175]

在该示例中,高bw pll 4301可包括如上文更详细描述的高增益相位检 测器102。在该示例中,低bw反馈环路2200可包括如上文更详细地描述的 高增益pd 2208。

[0176]

在该示例中,数字处理逻辑4310从反馈环路2200接收outn信号2215。 outn信号2215提供fbaw参考信号2202和ftcxo参考信号2204的频率之间 的比率的值。处理逻辑4310将该比率转换成提供给德尔塔-西格马114的分数 值nfrac 4311。这样,可根据ftcxo设置fvco1的ppm准确度,并且可实现 baw的低频相位噪声的抑制。

[0177]

在该示例中,描述了apll 4301。在另一个示例中,可使用数字pll来 代替apll 4301。

[0178]

图44是包括由数字pll(dpll)4401加强的图43的示例频率生成系统 4300的示例频率生成系统的框图。在该示例中,由tcxo反馈环路2200和 模拟pll 4301提供baw低偏移相位噪声的开环消除,如上文更详细地描述 的。

[0179]

在此示例中,dpll 4401向fref 4406提供闭环跟踪,以提供ppm准确度 和非常低的偏移相位噪声抑制。dpll 4401包括时间到数字转换器(tdc) 4402、数字环路滤波器4403、多模除法器4404和德尔塔-西格马4405。

[0180]

在该示例中,描述了apll 4301。在另一个示例中,可使用数字pll来 代替apll 4301。类似地,在该示例中描述了数字pll 4401。在另一个示例 中,可使用模拟pll来代替数字pll 4401。

[0181]

仿真

[0182]

图45是图2的示例噪声模型的仿真操作的相位噪声水平(dbc/hz)相对 于偏移频率的曲线图,示出了德尔塔-西格马噪声的噪声折叠效果(参见图5)。 在该示例中,曲线图线4510表示输出122(图1)处的总体相位噪声。在该 示例中,载波频率为312.5mhz,参考频率120(图2)为40.0mhz,除法器 210(图2)输入为2.5ghz,bw为14.7khz。由于德尔塔-西格马量化噪声 的噪声折叠,在低频下发生显著的劣化,但总噪声保持低于两个示例系统的 噪声目标,如4501、4502处指示的。

[0183]

图46是示出图43的示例系统4300的仿真操作的相位噪声水平(dbc/hz) 相对于偏移频率的曲线图。在该示例中,载波频率为312.5mhz,baw参考 频率2202(图43)为40.0mhz,除法器110(图43)输入为2.5ghz,bw 为14.7khz。在该示例中,曲线图线4610示出了出现在输出122(图43)上 的总体相位噪声。曲线图线4611示出了tcxo环路2200(图43)中的具有 折叠的德尔塔-西格马噪声。曲线图线4612示出了来自仿真并联baw振荡器 2201(图43)的baw噪声。曲线图线4613示出了txco环路2200(图43) 内的10位4.0mhz adc量化器的量化噪声。总噪声保持低于两个示例系统的 噪声目标,如4501、4502处指示的。

[0184]

图47a、图47b是示出由pd 2208(图22)内的定时电路系统生成的示 例bang-bang电路的操作的曲线图。在该示例中,曲线图线4701示出了馈入 德尔塔-西格马114(图43)的分数比率值4311(图43)的仿真阶跃响应。在 阶跃之前,bang-bang输出信号2222、2223(图22)是静止的,如4702处指 示的。在阶跃输入之后,bb输出信号2222、2223在少量时间(ms)内有效, 如4703处指示的,以便更快地稳定比率值。在短时间段之后,一旦比率值稳 定,bb

输出信号2222、2223再次变为静止,如4704处指示的。

[0185]

其他实施例

[0186]

在所描述的示例中,提出了高增益高bw相位检测器和高增益低bw相 位检测器。在所描述的示例中,这些以各种组合方式组合以提供产生具有低 噪声的稳定频率信号的可变频率系统。在另一个示例中,这些部件可被配置 为各种拓扑以提供增强的低噪声系统性能。

[0187]

在本说明中,术语“相位检测器”用于指检测参考信号和反馈信号之间 的相位差的电路。在一些示例中,相位检测器可包括脉冲生成器定时电路, 诸如pg电路1701(图17)。在其他示例中,相位检测器可以是如图15所示 的简单异或门。在一些示例中,相位检测器可包括“相位到电荷转换器

”ꢀ

(pcc),诸如pcc 905(图9)。在一些示例中,相位检测器可包括相位到数 字转换器,诸如相位到数字转换器2212(图22)。

[0188]

在所描述的示例中,在pcc中使用运算放大器。在另一个示例中,可使 用具有反相和非反相输入的另一类型的已知或后来开发的放大器配置。

[0189]

在本说明书中,术语“耦接”及其衍生物意味着间接的、直接的、光学 的和/或无线的电连接。因此,如果第一设备耦接到第二设备,则该连接可通 过直接电连接、通过经由其他设备和连接的间接电连接、通过光电连接和/或 通过无线电连接。

[0190]

在权利要求的范围内,在所描述的实施例中修改是可能的,并且其他实 施例是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。