能够自动分配地址的plc系统及其控制方法

技术领域

1.本发明涉及集成电路技术领域,尤其涉及一种能够自动分配地址的plc系统及其控制方法。

背景技术:

2.在可编程逻辑控制器(plc)系统中,一般都采用plc主控制器同时与多个i/o模块连接的星形结构,plc通过一条rs485或can总线访问各个独立的i/o模块。这种结构,各个i/o模块均需要独立供电,plc主控制器在访问各个独立的i/o模块之前,必须先给各个独立的i/o模块分配地址。

3.现有的i/o模块的地址分配方式有2种:(1)采用拨码开关方式,通过设置旋转拨码开关来设置每个i/o模块的地址,i/o模块上电时先采样拨码开关各引脚的状态从而将其解析成本i/o模块的地址;(2)采用通信设置方式,pc机或其他主机通过串口与i/o模块相连,把要配置成的“地址”发送给“i/o模块”,“i/o模块”将收到的“地址”保存至自身的flash中。

4.以上两种地址分配方式,至少存在以下不足:

5.(1)plc主控制器通过一条总线与多个i/o模块相连,物理上的接线需要额外增加“接线排”,才能使得plc主控制器的总线与i/o模块连接上,这样会导致布线复杂且不美观。

6.(2)当i/o模块个数较多时,总线上数据繁忙,plc主控制器需要分配大量的资源来负责轮询数据、接收数据及处理数据,给系统的运行增加了不可控因素,增加了不稳定风险。

7.(2)现场安装时,每个i/o模块需要根据现场需求,人为配置地址,这样不可避免的会出现地址重复设置或设置错误的现象,进而导致系统运行出错。

技术实现要素:

8.本发明要解决的技术问题是:为了解决现有技术中plc主控制器与多个i/o模块连接的方式,存在布线复杂,且会导致系统运行不稳定的技术问题,本发明提供一种能够自动分配地址的plc系统及其控制方法,不仅可以简化布线,还能够自动分配地址给i/o模块,提高系统运行的稳定性。

9.本发明解决其技术问题所采用的技术方案是:一种能够自动分配地址的plc系统,包括:主控制器、n个i/o模块以及lcd显示器,所述n个i/o模块之间依次串联,第一个所述i/o模块与所述主控制器连接,第一个所述i/o模块与所述lcd显示器连接,n≥2;其中,每个所述i/o模块均包含单片机和背板总线,所述单片机与所述背板总线连接,所述单片机能够根据所述背板总线输出分频信号自动分配地址给所述i/o模块。由此,不仅可以简化布线,还能够自动分配地址给i/o模块,提高系统运行的稳定性。

10.进一步地,所述背板总线包括电源模块、通讯模块及分频模块,所述电源模块与所述通讯模块连接,所述电源模块与所述分频模块连接。

11.进一步地,每个所述i/o模块还包括输入插接件xs1和输出插接件xs2,所述输入插

接件xs1与所述通讯模块连接,所述输入插接件xs1与所述分频模块连接,所述分频模块与所述输出插接件xs2连接。

12.进一步地,所述通讯模块包括一通讯芯片u2,所述通讯芯片u2具有ro引脚、re引脚、de引脚、di引脚、第一gnd引脚、a输出端、b输出端及第一vcc引脚,所述ro引脚、re引脚、de引脚及di引脚均与所述单片机连接,所述re引脚与de引脚连接,所述第一gnd引脚接地,所述第一vcc引脚与所述电源模块连接,所述a输出端和b输出端均与所述输入插接件xs1连接。

13.进一步地,所述分频模块包括一分频芯片u1,所述分频芯片u1具有clk引脚、第二gnd引脚、输入引脚d、输出引脚q、第二vcc引脚及clr引脚,所述clk引脚与所述输入插接件xs1连接,所述clr引脚和第二vcc引脚均与所述电源模块连接,所述第二gnd引脚接地,所述输入引脚d与输出引脚q连接,所述输出引脚q与所述输出插接件xs2连接。

14.进一步地,所述分频模块还包括电阻r46、电阻r48、三极管v4、二极管vd14及电阻r44,所述电阻r48的一端与所述输入引脚d连接,所述电阻r48的另一端与所述二极管vd14的阴极连接,所述二极管vd14的阳极接地,所述电阻r46的一端与所述输出引脚q连接,所述电阻r46的另一端与所述三极管v4的基极连接,所述三极管v4的集电极与所述电阻r44的一端连接,所述三极管v4的发射极与所述二极管vd14的阳极连接,所述二极管vd14的阴极与所述三极管v4的集电极连接,所述电阻r44的另一端与所述输出插接件xs2连接。

15.进一步地,第一个i/o模块的分频芯片u1的clk引脚与所述单片机连接,第一个i/o模块的分频芯片u1能够接收一个初始频率f1。

16.本发明还提供了一种能够自动分配地址的plc系统的控制方法,包括以下步骤:

17.s1、将第一个i/o模块记为主模块,每个i/o模块均能够进行数据采集;当n个i/o模块上电时,i/o模块的单片机可以读取背板总线输出的分频信号,单片机根据分频信号自动分配相应的地址给i/o模块;

18.s2、第一个i/o模块接收主控制器下发的控制信号,第一个i/o模块通过通讯协议能够将控制信号分别发送给第二个至第n个i/o模块;第一个i/o模块通过通讯协议能够分别接收第二个至第n个i/o模块采集到的数据信息,并将数据信息汇总后发送给主控制器;

19.s3、第一个i/o模块将汇总后的数据信息发送给lcd显示器进行显示。

20.进一步地,步骤s1中,单片机根据分频信号自动分配相应的地址给i/o模块,具体包括:

21.第一个i/o模块能够产生一个初始频率f1,初始频率f1通过分频芯片u1,从输出引脚q输出第一个分频信号f1/2,第一分频信号f1/2输入给第二个i/o模块,第二个i/o模块的输出引脚q输出第二个分频信号f1/4,以此类推,第n-1个i/o模块的输出引脚q输出第n-1个分频信号f1/2

n-1

,第n-1个分频信号f1/2

n-1

输入给第n个i/o模块,第n个i/o模块输出第n个分频信号f1/2n;

22.每一个分频信号均对应一个地址,当i/o模块上电后,每个i/o模块均能够产生相应的分频信号,单片机通过读取分频信号分配对应的地址给i/o模块。

23.本发明的有益效果是,本发明通过背板总线将n个i/o模块进行级联,一方面可以方便布线,提升系统整体的美观性,另一方面,单片机能够通过识别对应的i/o模块输出的分频信号,自动分配地址给i/o模块,不仅能够提高工作效率,还能够减少人为因素产生的

误差,保证plc系统运行的准确性。

附图说明

24.下面结合附图和实施例对本发明进一步说明。

25.图1是本发明的能够自动分配地址的plc系统的结构示意图;

26.图2是本发明的i/o模块的结构示意图;

27.图3是本发明的背板总线的结构示意图;

28.图4是本发明的背板总线的电路原理图;

29.图5是本发明的能够自动分配地址的plc系统的控制方法的流程图。

30.图中:1、主控制器;2、i/o模块;3、lcd显示器;21、单片机;22、背板总线;221、电源模块;222、通讯模块;223、分频模块。

具体实施方式

31.现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

32.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

33.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

34.如图1至图4所示,一种能够自动分配地址的plc系统包括:主控制器1、n个i/o模块2以及lcd显示器3,n个i/o模块2之间依次串联,第一个i/o模块2与主控制器1连接,第一个i/o模块2与lcd显示器3连接,n≥2;其中,每个i/o模块2均包含单片机21和背板总线22,单片机21与背板总线22连接,单片机21能够根据背板总线22输出分频信号自动分配地址给i/o模块2。换言之,在本实施例中,第一个i/o模块2与第二个i/o模块2连接,第二个i/o模块2与第三个i/o模块2连接,以此类推,第n-1个i/o模块2与第n个i/o模块2连接,每个i/o模块2均可以与传感设备连接,收集传感设备采集到的数据,同时能够接收主控制器1下发的控制信号,对传感设备进行调控。n个i/o模块2之间通过背板总线22连接起来,只有第一个i/o模块2与主控制器1连接,第一个i/o模块2通过背板总线22可以收集第二个至第n个i/o模块2接收到的数据,汇总后再发给主控制器1,并且,第一个i/o模块2能够接收主控制器1发出的控制信号,再分别发送给第二个至第n个i/o模块2,也就是说,本发明虽然具有多个i/o模块2,但是主控制器1仍然只与一个i/o模块2进行信号传输,减少了主控制器1被占用的资源,

提高了系统运行的稳定性。换言之,对主控制器1来说,n个i/o模块2可以等效为一个i/o模块。

35.在本实施例中,背板总线22包括电源模块221、通讯模块222及分频模块223,电源模块221与通讯模块222连接,电源模块221与分频模块223连接。每个i/o模块2还包括输入插接件xs1和输出插接件xs2,输入插接件xs1与通讯模块222连接,输入插接件xs1与分频模块223连接,分频模块223与输出插接件xs2连接。需要说明的是,每个i/o模块2的结构是相同的,通讯模块222与分频模块223之间可以通过输入插接件xs1连接起来,第一个i/o模块2与第二个i/o模块2之间可以通过输出插接件xs2实现连接,以此,可以将n个i/o模块2串联起来。电源模块221例如可以是3.3v电源。

36.具体的,通讯模块222包括一通讯芯片u2,通讯芯片u2具有ro引脚、re引脚、de引脚、di引脚、第一gnd引脚、a输出端、b输出端及第一vcc引脚,ro引脚、re引脚、de引脚及di引脚均与单片机21连接,re引脚与de引脚连接,第一gnd引脚接地,第一vcc引脚与电源模块221连接,a输出端和b输出端均与输入插接件xs1连接。ro引脚用于接收数据,di引脚用于发送数据,通讯模块222能够实现rs485通信,通讯模块222还包括电阻r35、三极管v3、电阻r40、电阻r30、电阻r32、电阻r38、电阻r41、电阻r33、电阻r36、电阻r31、电阻r39、电阻r34、电阻r37、二极管vd12及二极管vd13。电阻r32的一端与单片机21连接,电阻r32的另一端与ro引脚连接,电阻r30的一端与电源模块221连接,电阻r30的另一端与电阻r32的一端连接。电阻r38的一端与单片机21连接,电阻r38的另一端与di引脚连接,电阻r41的一端与di引脚连接,电阻r41的另一端与电源模块221连接。电阻r35的一端与电源模块221连接,电阻r35的另一端与de引脚连接,三极管v3的发射极与de引脚连接,三极管v3的集电极接地,三极管v3的基极与单片机21连接,电阻r40的一端与三极管v3的基极连接,电阻r40的另一端与三极管v3的集电极连接。当三极管v3的基极输入为低电平时,三极管v3导通,re引脚和de引脚为低电平,ro引脚处于工作状态,通讯芯片u2处于接收状态;当三极管v3的基极输入为高电平时,三极管v3截止,re引脚和de引脚为高电平,di引脚处于工作状态,通讯芯片u2处于发送状态,此时,通讯芯片u2可以通过a输出端和b输出端发送信号。电阻r33的一端与b输入端连接,电阻r33的另一端与二极管vd12的阴极连接,二极管vd12的阳极接地,电阻r31的一端接地,电阻r31的另一端与二极管vd12的阴极连接,电阻r34的一端与二极管vd12的阴极连接,电阻r34的另一端与输入插接件xs1连接。电阻r36的一端与a输出端连接,电阻r36的另一端与二极管vd13的阴极连接,二极管vd13的阳极接地,电阻r39的一端与二极管vd13的阴极连接,电阻r39的另一端与电源模块221连接,电阻r37的一端与二极管vd13的阴极连接,电阻r37的另一端与输入插接件xs1连接。在通讯模块222中,电阻可以起到限流、分压作用,使得电路中的电子元器件能够正常工作,二极管vd12和二极管vd13能够起到防反作用。

37.分频模块223包括一分频芯片u1,分频芯片u1具有clk引脚、第二gnd引脚、输入引脚d、输出引脚q、第二vcc引脚及clr引脚,clk引脚与输入插接件xs1连接,clr引脚和第二vcc引脚均与电源模块221连接,第二gnd引脚接地,输入引脚d与输出引脚q连接,输出引脚q与输出插接件xs2连接。分频模块223还包括电阻r46、电阻r48、三极管v4、二极管vd14及电阻r44,电阻r48的一端与输入引脚d连接,电阻r48的另一端与二极管vd14的阴极连接,二极管vd14的阳极接地,电阻r46的一端与输出引脚q连接,电阻r46的另一端与三极管v4的基极连接,三极管v4的集电极与电阻r44的一端连接,三极管v4的发射极与二极管vd14的阳极连

接,二极管vd14的阴极与三极管v4的集电极连接,电阻r44的另一端与输出插接件xs2连接。二极管vd14具有防反作用。

38.本实施例的分频模块223的工作原理是,clr引脚为高电平,clk引脚输入时钟信号,当clk引脚的时钟信号在上升沿时,数据可以从输入引脚d传输至输出引脚q。例如,输入引脚d为“1”(即高电平),在时钟信号的第一个上升沿时,输出引脚q为“1”,此时,可以导通三极管vd14,使得输入引脚d变为“0”(即低电平),在时钟信号的第二个上升沿时,输出引脚q输出“0”,三极管vd14截止,使得输入引脚d又变为“1”。也就是说,输出引脚q的频率为clk引脚的二分之一。

39.本实施例通过对分频模块223电路结构的设计,使得输出引脚q的频率为输入频率的一半,而n个i/o模块2是依次串联的,第一个i/o模块2的输出频率可以传递给第二个i/o模块2,第二个i/o模块2的输出频率也为输入频率(即第一个i/o模块2的输出频率)的一半,依次类推,第n个i/o模块2的输出频率为第n-1个i/o模块2的输出频率的一半。输出频率即分频信号。

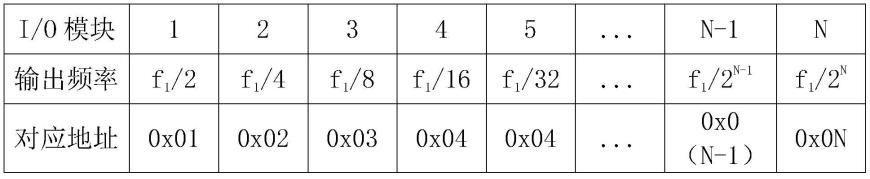

40.第一个i/o模块2的分频芯片u1的clk引脚与单片机21连接,第一个i/o模块2的分频芯片u1能够接收一个初始频率f1。即,在分频模块223的backbusmcu处输入一个初始频率f1,初始频率f1经过分频芯片u1可以在输出引脚q处输出第一个分频信号f1/2。请参考表1,每个i/o模块2输出的频率是不同的,例如,初始频率为4khz时,第一i/o模块2的输出频率为2khz,第二个i/o模块2的输出频率为1khz,第三个i/o模块2的输出频率为500hz,第四个i/o模块2的输出频率为250hz,以此类推,第八个i/o模块2的输出频率为15hz(误差在5%以内),i/o模块2的具体数量可以根据初始频率f1的大小进行设置,以最后一个i/o模块2的输出频率不能过小为准(例如,不能小于5hz),否则无法被单片机21采集到。当n个i/o模块2通电后,每个i/o模块2可以输出一个对应的分频信号,这个分频信号可以被i/o模块2自身的单片机21采集到,单片机21采集到分频信号后,可以根据对应关系(即表2)分配相应的地址给这个i/o模块2,频率和地址的对应的关系已提前存储在每个单片机21内。

41.表1

[0042][0043]

本实施例通过将n个i/o模块串联,结合分频模块223的特性,可以使得n个i/o模块2输出不同的分频信号,单片机21再根据这个分频信号分配不同地址给i/o模块2;由此,一方面,可以简化plc系统的布线,提高plc系统整体布线的美观性;另一方面,每个i/o模块2的地址是自动分配的,可以防止出现地址重复的情况。并且,本实施例由第一个i/o模块2与主控制器1之间直接进行数据收发,可以减少主控制器1的内存资源消耗,提高olc系统运行的稳定性,降低崩溃的风险。

[0044]

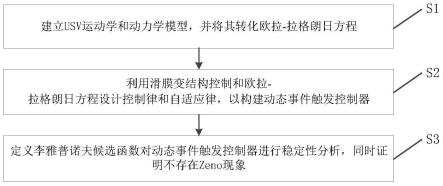

如图5所示,本发明还提供一种上述的能够自动分配地址的plc系统的控制方法,包括以下步骤:

[0045]

s1、将第一个i/o模块2记为主模块,每个i/o模块2均能够进行数据采集;当n个i/o

模块2上电时,i/o模块2的单片机21可以读取背板总线22输出的分频信号,单片机21根据分频信号自动分配相应的地址给i/o模块2。

[0046]

s2、第一个i/o模块2接收主控制器1下发的控制信号,第一个i/o模块2通过通讯协议能够将控制信号分别发送给第二个至第n个i/o模块2;第一个i/o模块2通过通讯协议能够分别接收第二个至第n个i/o模块2采集到的数据信息,并将数据信息汇总后发送给主控制器1。

[0047]

s3、第一个i/o模块2将汇总后的数据信息发送给lcd显示器3进行显示。

[0048]

需要说明的是,单片机21根据分频信号自动分配相应的地址给i/o模块2,具体包括:第一个i/o模块2能够产生一个初始频率f1,初始频率f1通过分频芯片u1,从输出引脚q输出第一个分频信号f1/2,第一分频信号f1/2输入给第二个i/o模块2,第二个i/o模块2的输出引脚q输出第二个分频信号f1/4,以此类推,第n-1个i/o模块2的输出引脚q输出第n-1个分频信号f1/2

n-1

,第n-1个分频信号f1/2

n-1

输入给第n个i/o模块2,第n个i/o模块2输出第n个分频信号f1/2n。每一个分频信号均对应一个地址,当i/o模块2上电后,每个i/o模块2均能够产生相应的分频信号,单片机21通过读取分频信号分配对应的地址给i/o模块2。对应的技术效果请参考能够自动分配地址的plc系统部分的描述,此处不再赘述。

[0049]

需要说明的是,由于本发明的n个i/o模块2之间串联,且由第一个i/o模块2收集或下发第二个至第n个i/o模块2的数据信息,因此,需要定义新的通讯协议。

[0050]

首先,确定通讯协议的数据帧格式,如表2所示,设备地址指的是i/o模块2的地址,表1中的地址是用十六进制表示的,可以转换成二进制表示(即8bit)功能号可以设置为0x2b和0x2c,0x2b表示主机发送命令,0x2c表示从机回复命令,数据格式表示i/o模块采集或接受到的数据表示形式,crc校验l和crc校验h是用于检验接收的数据是否正确,如果验证正确,才可以进行下一步操作。

[0051]

表2

[0052]

设备地址功能代码数据帧crc校验lcrc校验h8bit8bitn*8bit8bit8bit

[0053]

主i/o模块2和其他i/o模块2之间的数据收发协议可以设置为:

[0054]

每个ai/ao通道的数据占2字节(byte),一个字节包含8位,低端排列;每个di/do占用1位(bit),位0为低端口号数据。其中,di表示:数字信号输入,do表示:数字信号输出,ai表示:模拟信号输入,ao表示:模拟信号输出。

[0055]

若主i/o模块2发送数据给其他i/o模块2,数据帧中的第一个字节的含义为:bit0:主i/o模块有无do的控制数据发给其他i/o模块(1表示有do数据,0表示无do数据);bit1:主i/o模块有无ao的控制数据发给其他i/o模块(1表示有ao数据,0为无)bit2~bit7:保留。

[0056]

若数据帧的byte1的bit0\bit1均为1,则先传do数据,再传ao数据。从数据帧byte2开始分别为do的通道个数(当数据帧的byte1的bit0为1时才有)和ao的通道个数(当数据帧的byte1的bit1为1时才有),然后byte2的其他位表示分别表示各个do的数据和各个ao的数据,接收方必须依据协议核实数据帧的总字节数、通道数和数据数的关系,才能设置本地的do和ao。需要说明的是,当主i/o模块读过某个其他i/o模块后,根据其他i/o模块回复的数据,主i/o模块才能知道某个其他i/o模块的di/ai/do/ao的通道个数。

[0057]

例如,

[0058]

示例1:主i/o模块读第二个i/o模块,需要发送数据:ox01 0x2b 0x00 0x3e 0xf0,则:

[0059]

设备地址功能代码数据帧crc校验lcrc校验h0x010x2b0x000x3e0xfo

[0060]

示例2:主i/o模块读第二个i/o模块,并且控制第二个i/o模块的第一位继电器输出,需发送数据:0x01 0x2b 0x01 0x01 0x01 0x81 0xb4,则:

[0061]

设备地址功能代码数据帧crc校验lcrc校验h0x010x2b0x01 0x01 0x010x810xb4

[0062]

示例3:主i/o模块读第二个i/o模块,并且控制第二个主i/o模块的ao通道输出2.56v(0x00 0x01),需发送数据:0x01 0x2b 0x02 0x01 0x00 0x01 0xb4 0x74,则:

[0063]

设备地址功能代码数据帧crc校验lcrc校验h0x010x2b0x02 0x01 0x00 0x010xb40x74

[0064]

若其他i/o模块需要发送数据给主i/o模块,数据帧中的第一个字节(byte1)的含义位:bit0:其他i/o模块有无di的数据发给主i/o模块(1表示有di数据,0表示无di数据);bit1:其他i/o模块有无ai的数据发给主i/o模块(1表示有ai数据,0表示无ai数据);bit2:其他i/o模块有无do的状态数据发给主i/o模块(1表示有do状态数据,0表示无do状态数据);bit3:其他i/o模块有无ao的状态数据发给主i/o模块(1表示有ao状态数据,0表示无ao状态数据);bit4~7:保留。

[0065]

若bit0\bit1均为1,bit2\bit3均为0,则先di后ai;数据帧的byte2开始分别表示di通道个数和ai通道个数数,然后分别是各个di的数据和各个ai的数据。

[0066]

例如,若第二个i/o模块硬件上支持1路di、1路ai、2路do、1路ao,假设此时di数据为0x01 0x02,ai数据为:0x03 0x04,do为0x03,ao为0x05 0x06,则当第二个i/o模块收到主i/o模块的0x2b命令后,第二个i/o模块回复:0x01 0x2c 0x0f 0x01 0x01 0x02 0x01 0x01 0x02 0x03 0x04 0x03 0x05 0x06 0x7b 0xad,则

[0067][0068]

当其他i/o模块通讯中断3秒后,其数据输出应当进行复位,主i/o模块对从第二个i/o模块开始的连续在线的其他i/o模块通讯控制输出,主i/o模块依据其他i/o模块的通道数,自动转存数据到主i/o模块的di/do/ai/ao通道。

[0069]

换言之,本发明通过自定义的通讯协议,可以实现主i/o模块与其他i/o模块之间的数据收发,使得主控制器1只需要与第一个i/o模块2之间进行通信即可,可以减少主控制器1的内存占用,提高plc系统整体运行的稳定性。

[0070]

综上所述,本发明的能够自动分配地址的plc系统及其控制方法,通过背板总线22将n个i/o模块2进行级联,一方面可以方便布线,提升系统整体的美观性,另一方面,单片机21能够通过识别对应的i/o模块2输出的分频信号,自动分配地址给i/o模块2,不仅能够提高工作效率,还能够减少人为因素产生的误差,保证plc系统运行的准确性。

[0071]

以上述依据本发明的理想实施例为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要如权利要求范围来确定其技术性范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。