用于逐元素乘法的存储器内处理器件

1.相关申请的交叉引用

2.本技术要求于2021年1月11日提交的韩国申请第10-2021-0003633号的优先权,其整体内容通过引用合并于此。

技术领域

3.本发明的各实施方式涉及存储器内处理(以下称为“pim”)器件,更具体地,涉及用于逐元素乘法(以下称为“ewm”)的pim器件。

背景技术:

4.近来,不仅在信息技术行业而且在金融和医疗行业中,对人工智能(ai)的兴趣一直在增加。因此,在相应的领域中,人工智能、更确切地说是深度学习的引入被考虑以及原型化。通常,用于有效学习深度神经网络(dnn)或与通用神经网络相比具有增加的层的深度网络以利用深度神经网络(dnn)或深度网络进行模式识别或推理的技术通常称为深度学习。

5.这种引起广泛关注的一个原因是执行算术运算的处理器的性能提高。为了提高人工智能的性能,有必要增加构成人工智能中的神经网络的层数以训练人工智能。近年来,这种趋势一直持续,这导致实际执行计算的硬件所需的计算量呈指数增长。此外,如果人工智能采用包括彼此分离的存储器和处理器的通用硬件系统,则人工智能的性能可能由于存储器和处理器之间的数据通信量的限制而降低。

技术实现要素:

6.根据一个实施方式,一种存储器内处理(pim)器件包括乘法器电路、存储器电路和地址流水线电路。乘法器电路被配置为执行第一输入数据和第二输入数据的逐元素乘法(ewm)计算以生成结果数据。存储器电路被配置为响应于读取控制信号将第一输入数据和第二输入数据输出至乘法器电路,以及被配置为响应于写入控制信号存储结果数据。地址流水线电路被配置为接收读取控制信号以存储地址信号用作目标地址信号,目标地址信号用于指定存储器电路的且中存储结果数据的区域,以及被配置为接收写入控制信号以将目标地址信号输出到存储器电路。

7.根据另一实施方式,一种存储器内处理(pim)器件包括乘法累加(mac)电路、存储器电路和地址流水线电路。mac电路被配置为对第一输入数据和第二输入数据执行mac算术运算或逐元素乘法(ewm)计算以生成结果数据。存储器电路被配置为响应于读取控制信号将第一输入数据和第二输入数据输出至mac电路,以及被配置为响应于写入控制信号存储结果数据。地址流水线电路被配置为接收读取控制信号以存储地址信号用作目标地址信号,目标地址信号用于指定存储器电路的且中存储结果数据的区域,以及被配置为接收写入控制信号以将目标地址信号输出到存储器电路。

附图说明

8.参照附图通过各种实施方式示出了所公开的技术的某些特征,其中:

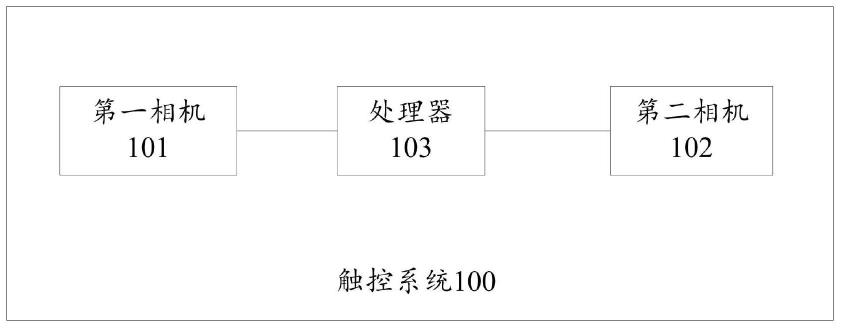

9.图1是示出根据本教导的一个实施方式的pim器件的框图;

10.图2是示出由图1所示的pim器件执行的ewm处理的示意图;

11.图3示出了包括在图1所示的pim器件中的地址流水线电路的配置;

12.图4是示出由图1所示的pim器件执行的ewm处理的时序图;

13.图5至图13是示出在图4所示的时序图的相应的时间点处执行的ewm计算的框图;

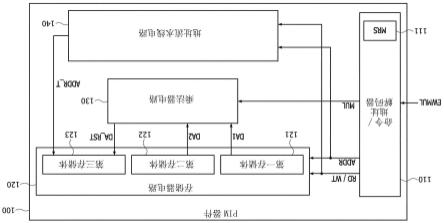

14.图14是示出根据本教导的另一实施方式的pim器件的框图;以及

15.图15是示出图14所示的pim器件中包括的乘法累加(mac)电路的框图。

具体实施方式

16.在实施方式的以下描述中,将理解的是,术语“第一”和“第二”旨在标识元件,但是不用于限定元件的特定数量或顺序。此外,当元件被称为位于另一元件“上”、“之上”、“上方”、“下”或“之下”时,旨在表示相对位置关系,但不用于限制该元件直接接触另一元件、或者在这两个元件之间存在至少一个中间元件的特定情况。因此,在这里使用的诸如“上”、“之上”、“上方”、“下”、“之下”和“下方”等术语仅出于描述特定实施方式的目的,而非意在限制本公开的范围。此外,当一个元件被称为“连接”或“耦接”到另一元件时,该元件可以直接电气或机械地连接或耦接到另一元件,或者可以以这两个元件之间具有一个或更多个其他元件的方式间接地被电气或机械地连接或耦接到该另一元件。此外,当参数被称为“预定的”时,旨在意指在将参数用于处理或算法中之前预先确定参数的值。可以在处理或算法开始时设置参数的值,或者可以在处理或算法被执行的时段期间设置参数的值。逻辑“高”电平和逻辑“低”电平可用于描述电信号的逻辑电平。具有逻辑“高”电平的信号可以区别于具有逻辑“低”电平的信号。例如,当具有第一电压的信号对应于具有逻辑“高”电平的信号时,具有第二电压的信号可以对应于具有逻辑“低”电平的信号。在一个实施方式中,逻辑“高”电平可以被设置为高于逻辑“低”电平的电压电平的电压电平。而且,信号的逻辑电平可以根据实施方式而被设置为不同或相反。例如,在一个实施方式中具有逻辑“高”电平的某个信号可以在另一实施方式中被设置为具有逻辑“低”电平。

17.在下文中将参考附图详细描述本公开的各实施方式。然而,本文描述的实施方式仅用于说明性目的,以及不旨在限制本公开的范围。

18.各实施方式涉及基于在cas到cas命令延迟时间“tccd”的间隔发送的命令执行逐元素乘法(ewm)算术运算以加速ewm算术运算的存储器内处理(pim)器件。

19.图1是示出根据本教导的一个实施方式的pim器件100的框图。参照图1,pim器件100可以包括命令/地址解码器110、存储器电路120、乘法器电路130和地址流水线电路140。

20.命令/地址解码器110可以从外部设备(例如主机或控制器)接收命令。除了命令之外,命令/地址解码器110还可以接收关于地址的信息。在下文中,可以假定该命令包括关于地址的信息。命令/地址解码器110可以对命令进行解码以生成各种控制信号rd、wt和mul。命令/地址解码器110还可以解码地址信息以生成地址信号addr。在另一实施方式中,命令/地址解码器110可以包括对命令进行解码的命令解码器和对地址信息进行解码的地址解码器。

21.在一个实施方式中,命令/地址解码器110可以从外部设备接收ewm命令ewmul。命令/地址解码器110可以对ewm命令ewmul进行解码以生成读取控制信号rd、写入控制信号wt、算术控制信号mul和地址信号addr。由命令/地址解码器110生成的读取控制信号rd、写入控制信号wt和地址信号addr可以被发送到存储器电路120和地址流水线电路140两者。由命令/地址解码器110生成的算术控制信号mul可以被发送到乘法器电路130。

22.命令/地址解码器110可以包括模式寄存器组(mrs)111。模式寄存器组111可以具有与pim器件100的操作所需的参数的信息有关的预定值。pim器件100可以执行通常的存储器访问操作,例如,存储器读取操作和存储器写入操作。此外,pim器件100可以执行ewm算术运算。在本实施方式中,ewm算术运算是指执行具有相同形式的两个矩阵的逐元素乘法的运算。在下文中,术语“ewm算术运算”可以被解释为具有与术语“ewm计算”相同的含义。模式寄存器组111可以具有用于pim器件100的存储器访问操作的第一预定值和用于pim器件100的ewm算术运算的第二预定值。例如,模式寄存器组111可以激活第一预定值以执行诸如pim器件100的存储器读取操作或存储器写入操作的存储器访问操作。相反,模式寄存器组111可以激活第二预定值以执行pim器件100的ewm算术运算。

23.在下文中,可以假设pim器件100操作以执行ewm算术运算,以及模式寄存器组111激活第二预定值以执行ewm算术运算。因此,可以将在pim器件100的ewm算术运算期间从命令/地址解码器110输出的读取控制信号rd和写入控制信号wt与在pim器件100的存储器访问操作期间从命令/地址解码器110输出的读取控制信号和写入控制信号区分开。

24.存储器电路120可以包括第一存储体121、第二存储体122和第三存储体123。在一个实施方式中,存储器电路120可以包括易失性存储器,诸如sram或dram。例如,存储器电路120可以包括sram、同步dram(sdram)、双数据速率同步dram(ddr sdram、ddr2 sdram或ddr3 sdram)、图形双数据速率同步dram(gddr、gddr2或gddr3等)、四数据速率dram(qdr dram)、rambus极限数据速率dram(rambus xdr dram)、快速页面模式dram(fpm dram)、视频dram(vdram)、扩展数据输出dram(edo dram)、突发扩展数据输出dram(bedo dram)、多存储体dram(mdram)、同步图形ram(sgram)或其他类型的dram。在又一实施方式中,存储器电路120可以包括非易失性存储器,诸如闪存、相变存储器(pcram)、电阻存储器(reram)、铁电存储器(feram)或磁存储器(mram)。在再一实施方式中,存储器电路120可以包括易失性存储器和非易失性存储器两者。

25.第一存储体121、第二存储体122和第三存储体123可具有多个行和多个列。存储单元可以分别位于行和列的交叉点处。可以通过行地址和列地址来实现对第一至第三存储体121、122和123中的存储单元的访问。即,当行地址和列地址确定时,在由行地址指定的行中排列的存储单元中的位于由列地址指定的列中的存储单元可以被选择。

26.第一存储体121可以存储用于ewm算术运算的第一输入数据da1,以及第二存储体122可以存储用于ewm算术运算的第二输入数据da2。可以通过通常的存储器写入操作来执行用于将第一输入数据da1存储到第一存储体121中以及用于将第二输入数据da2存储到第二存储体122中的操作。在下文中,可以假设通过通常的存储器写入操作将第一输入数据da1和第二输入数据da2存储在第一存储体121和第二存储体122中的相应一个中。由ewm算术运算生成的结果数据da_rst可以存储到第三存储体123中。

27.第一存储体121和第二存储体122可以响应于从命令/地址解码器110输出的读取

控制信号rd输出第一输入数据da1和第二输入数据da2以及将其发送到乘法器电路130。第三存储体123可以响应于从命令/地址解码器110输出的写入控制信号wt而存储从乘法器电路130输出的结果数据da_rst。为了将结果数据da_rst存储到第三存储体123中,第三存储体123可以从地址流水线电路140接收目标地址信号addr_t。第三存储体123可以响应于从命令/地址解码器110输出的写入控制信号wt而将结果数据da_rst存储到与目标地址信号addr_t相对应的位置中。

28.乘法器电路130可以对分别从第一存储体121和第二存储体122接收到的第一输入数据da1和第二输入数据da2执行ewm算术运算以生成结果数据da_rst。乘法器电路130可以响应于从命令/地址解码器110输出的算术控制信号mul来执行ewm算术运算。乘法器电路130可以将结果数据da_rst发送到存储器电路120的第三存储体123。在一个实施方式中,乘法器电路130可以包括至少一个乘法器,其执行第一输入数据da1和第二输入数据da2的乘法计算以输出乘法计算的结果数据。

29.地址流水线电路140可以存储向第三存储体123发送的目标地址信号addr_t。目标地址信号addr_t可以被限定为用于指定第三存储体123的其中存储从乘法器电路130输出的结果数据da_rst的位置的地址信号。地址流水线电路140可以响应于写入控制信号wt而将目标地址信号addr_t发送到第三存储体123。地址流水线电路140可以包括多个存储区域,每个存储区域能够存储目标地址信号addr_t。在一个实施方式中,多个存储区域中的每个可以包括地址寄存器。

30.具体地,地址流水线电路140可以执行地址存储操作和地址输出操作。地址流水线电路140的地址存储操作可以响应于从命令/地址解码器110输出的读取控制信号rd来被执行。也就是说,地址流水线电路140可以响应于读取控制信号rd而存储与读取控制信号rd一起发送的地址信号addr作为目标地址信号addr_t。在这种情况下,地址流水线电路140可以生成与读取控制信号rd相对应的索引。目标地址信号addr_t和读取控制信号rd可以通过索引而彼此相关。

31.地址流水线电路140的地址输出操作可以响应于从命令/地址解码器110输出的写入控制信号wt来被执行。也就是说,地址流水线电路140可以响应于写入控制信号wt输出其中存储的目标地址信号addr_t以及将其发送到存储器电路120的第三存储体123。在这种情况下,地址流水线电路140可以生成与写入控制信号wt相对应的索引选择信号。地址流水线电路140可以将与具有与索引选择信号相同的值的索引相对应的目标地址信号addr_t发送到第三存储体123。例如,当索引选择信号具有“111”的逻辑电平组合时,地址流水线电路140可以将对应于具有逻辑电平组合“111”的索引的目标地址信号addr_t发送到第三存储体123。

32.在将ewm命令ewmul发送到pim器件100时,第一输入数据da1和第二输入数据da2可以从第一存储体121和第二存储体122发送到乘法器电路130。此外,用于指定第三存储体123的存储从乘法器电路130输出的结果数据da_rst的位置的地址信号addr可以被存储在地址流水线电路140中作为目标地址信号addr_t。存储在地址流水线电路140中的目标地址信号addr_t可以被发送到第三存储体123。用于将结果数据da_rst存储到第三存储体123中的写入控制信号wt也可以随目标地址信号addr_t被发送到第三存储体123。如上所述,由于目标地址信号addr_t由地址流水线电路140生成以及被发送到第三存储体123,因此直到结

果数据da_rst被存储到第三存储体123中为止都保持由命令/地址解码器110生成的地址信号addr可以是不必要的。因此,命令/地址解码器110可以以cas到cas命令延迟时间“tccd”的间隔来执行ewm命令ewmul,该间隔与顺次生成的命令之间的最小间隔时间相对应。

33.图2是示出由图1所示的pim器件100执行的ewm算术运算的示意图。参照图2,pim器件100可以对第一输入数据da1_0~da1_n和第二输入数据da2_0~da2_n执行ewm算术运算以生成结果数据da_rst_0~da_rst_n(其中“n”表示自然数)。在下文中,可以假定所有第一输入数据da1_0~da1_n、第二输入数据da2_0~da2_n和结果数据da_rst_0~da_rst_n都具有浮点类型。

34.当对第一矩阵和第二矩阵执行ewm算术运算时,第一输入数据da1_0~da1_n可以对应于第一矩阵的元素,以及第二输入数据da2_0~da2_n可以对应于第二矩阵的元素。在这种情况下,第一输入数据da1_0~da1_n中的向乘法器电路130输入的第一输入数据和第二输入数据da2_0~da2_n中的向乘法器电路130输入的第二输入数据可以对应于位于第一矩阵和第二矩阵中的相同位置处的两个元素。替选地,第一输入数据da1_0~da1_n可以对应于在第一矩阵中排列的元素之一,以及第二输入数据da2_0~da2_n可以对应于在第二矩阵中排列的元素之一。即使在这种情况下,第一输入数据da1_0~da1_n和第二输入数据da2_0~da2_n也可以对应于位于第一矩阵和第二矩阵中的相同位置的两个元素。

35.第一输入数据da1_0~da1_n可以存储在第一存储体121的第一行rl中,以及第二输入数据da2_0~da2_n可以存储在第二存储体122的第一行rl中。此外,结果数据da_rst_0~da_rst_n可以存储在第三存储体123的第一行r1中。第一至第三存储体121、122和123的所有第一行r1可以具有相同的行地址。

36.在一个实施方式中,第一输入数据da1_0~da1_n中的每个和第二输入数据da2_0~da2_n中的每个可以具有适合于乘法器电路130中包括的乘法器的计算能力的数据尺寸。例如,当乘法器电路130中包括的乘法器能够对具有浮点类型的16比特位数据执行乘法计算时,向乘法器输入的第一输入数据da1_0和第二输入数据da2_0每个可以包括具有浮点类型的16比特位数据。在这种情况下,为了完成第一输入数据da1_0~da1_n和第二输入数据da2_0~da2_n的ewm算术运算,乘法器电路130必须迭代执行ewm计算(n 1)次。

37.为了pim器件100执行ewm计算(n 1)次,pim器件100必须从诸如主机或控制器的外部设备接收ewm命令ewmul(n 1)次。在本实施方式中,可以假设ewm命令ewmul包括地址信号addr。然而,本实施方式仅是本公开的示例。因此,在另一实施方式中,ewm命令ewmul和地址信号addr可以被分开地并且独立地发送。在本实施方式中,可以假设地址信号addr包括列地址信号。因此,包括在ewm命令ewmul中的地址信号addr可以表示用于指定存储第一输入数据da1和第二输入数据da2的区域以及用于指定其中存储结果数据da_rst的区域的列地址。在下文中,可以假定第一输入数据和第二输入数据被存储在具有相同列地址的区域中,并且结果数据也可以被存储在具有相同列地址的区域中。

38.当包括第一地址信号addr_0的ewm命令ewmul被发送到pim器件100时,pim器件100可以执行第一ewm计算。在这种情况下,为了执行第一ewm计算,如图2所示,可以将存储在第一存储体121的由第一地址信号addr_0指定的区域中的第一输入数据da1_0发送到乘法器电路130,以及还可以将存储在第二存储体122的由第一地址信号addr_0指定的区域中的第二输入数据da2_0发送到乘法器电路130。乘法器电路130可以对第一输入数据da1_0和第二

输入数据da2_0执行ewm计算以生成第一结果数据da_rst_0。第一结果数据da_rst_0可以被存储到第三存储体123的由第一地址信号addr_0指定的区域中。

39.当包括第二地址信号addr_1的ewm命令ewmul被发送到pim器件100时,pim器件100可以执行第二ewm计算。在这种情况下,为了执行第二ewm计算,可以将存储在第一存储体121的由第二地址信号addr_1指定的区域中的第一输入数据da1_1发送到乘法器电路130,以及还可以将存储在第二存储体122的由第二地址信号addr_1指定的区域中的第二输入数据da2_1发送到乘法器电路130。乘法器电路130可以对第一输入数据da1_1和第二输入数据da2_1执行ewm计算以生成第二结果数据da_rst_1。第二结果数据da_rst_1可以被存储到第三存储体123的由第二地址信号addr_1指定的区域中。结果,可以迭代地执行(n 1)次ewm计算以处理所有第一输入数据da1_0~da1_n和第二输入数据da2_0~da2_n。

40.如上所述,第一至第(n 1)ewm计算中的每个可以在结果数据da_rst被存储到第三存储体123中之后结束。为了将结果数据da_rst存储到第三存储体123中,用于指定第三存储体123的其中存储结果数据da_rst的区域的地址信号addr必须保持激活状态。例如,第一地址信号addr_0必须被激活,直到由第一ewm计算生成的第一结果数据da_rst_0被存储到第三存储体123中为止。因此,在通常情况下,直到将第一结果数据da_rst_0存储到第三存储体123中为止可能无法执行第二ewm计算。然而,根据本实施方式,可以将第一地址信号addr_0存储到地址流水线电路(图1的140)中作为目标地址信号addr_t,而存储在地址流水线电路140中的目标地址信号addr_t(即,第一地址信号addr_0)可以在第一结果数据da_rst_0被存储到第三存储体123中的时间点处被发送到第三存储体123。因此,甚至在将第一结果数据da_rst_0存储到第三存储体123中之前执行第二ewm计算可以是可能的。因此,第一ewm计算和第二ewm计算可以并存地被执行而彼此部分交叠。

41.图3示出了包括在图1所示的pim器件100中的地址流水线电路140的配置。在下文中,可以假定第一ewm命令、第二ewm命令和第三ewm命令被顺次发送到pim器件100。因此,第一读取控制信号rd0、第一写入控制信号wt0和第一地址信号addr_0被发送到地址流水线电路140;然后第二读取控制信号rd1、第二写入控制信号wt1和第二地址信号addr_1被发送到地址流水线电路140;以及最后第三读取控制信号rd2、第三写入控制信号wt2和第三地址信号addr_2被发送到地址流水线电路140。参照图3,地址流水线电路140可以包括:存储目标地址信号和索引的地址存储部141;生成索引的索引生成器142;以及生成用于检测索引以指定目标地址信号addr_t的索引选择信号index_s的索引检测器143。

42.地址存储部141可具有多个地址存储区域141-1和多个索引存储区域141-2。多个目标地址信号addr_t可以分别存储在多个地址存储区域141-1中。即,从命令/地址解码器(图1的110)发送到地址流水线电路140的地址信号addr可以被存储到多个地址存储区域141-1中的一个中。例如,第一地址信号addr_0可以被存储到第一个地址存储区域141-1中以用作第一目标地址信号addr_t0,第二地址信号addr_1可以被存储到第二个地址存储区域141-1中以用作第二目标地址信号addr_t1,以及第三地址信号addr_2可以被存储到第三个地址存储区域141-1中以用作第三目标地址信号addr_t2。一个索引可以被存储到多个索引存储区域141-2中的一个中。例如,可以将第一索引index0存储到第一个索引存储区域141-2中,可以将第二索引index1存储到第二各索引存储区域141-2中,以及可以将第三索引index2存储到第三个索引存储区域141-2中。

43.存储在相应的地址存储区域141-1中的目标地址信号addr_t可以以一对一的方式对应于存储在相应的索引存储区域141-2中的索引。例如,第一目标地址信号addr_t0可以对应于第一索引index0,第二目标地址信号addr_t1可以对应于第二索引index1,以及第三目标地址信号addr_t2可以对应于第三索引index2。因此,当索引中的任何一个被选择时,多个目标地址信号中的与所选择的索引对应的目标地址信号可以被选择。

44.索引生成器142可以响应于从命令/地址解码器(图1的110)输出的读取控制信号rd生成索引,以及可以将所生成的索引发送到多个索引存储区域141-2中的一个中。在一个实施方式中,索引生成器142可以包括第一计数器142-1。第一计数器142-1可以接收读取控制信号rd。第一计数器142-1可以对读取控制信号rd进行计数以生成用作索引的计数值,以及可以将索引输出到索引存储区域141-2。在这种情况下,可以将索引存储到索引存储区域141-2中以对应于与同读取控制信号rd一起输入的地址信号addr匹配的目标地址信号addr_t。

45.具体地,当第一读取控制信号rd0和第一地址信号addr0被输入到地址流水线电路140时,第一地址信号addr0可以被存储到地址存储区域141-1中以用作第一目标地址信号addr_t0。第一计数器142-1可以对第一读取控制信号rd0进行计数以生成具有计数值“001”的索引。计数值“001”可以被存储到索引存储区域141-2中以用作与第一目标地址信号addr_t0相对应的第一索引index0。随后,当第二读取控制信号rd1和第二地址信号addr1被输入到地址流水线电路140时,第二地址信号addr1可以被存储到地址存储区域141-1中以用作第二目标地址信号addr_t1。第一计数器142-1可以对第二读取控制信号rd1进行计数以生成具有计数值“010”的索引。计数值“010”可以被存储到索引存储区域141-2中以用作与第二目标地址信号addr_t1相对应的第二索引index1。类似地,当第三读取控制信号rd2和第三地址信号addr2被输入到地址流水线电路140时,第三地址信号addr2可以被存储到地址存储区域141-1中以用作第三目标地址信号addr_t2。第一计数器142-1可以对第三读取控制信号rd2进行计数以生成具有计数值“011”的索引。计数值“011”可以被存储到索引存储区域141-2中以用作与第三目标地址信号addr_t2相对应的第三索引index2。

46.索引检测器143可以响应于从命令/地址解码器(图1的110)输出的写入控制信号wt来生成索引选择信号index_s,以及可以将索引选择信号index_s发送到地址存储部141。在一个实施方式中,索引检测器143可以包括第二计数器143-1。第二计数器143-1可以接收写入控制信号wt。第二计数器143-1可以对写入控制信号wt进行计数以生成用作索引选择信号index_s的计数值,以及可以将索引选择信号index_s输出到地址存储部141。

47.具体地,当第一写入控制信号wt0被输入到索引检测器143时,索引检测器143的第二计数器143-1可以对第一写入控制信号wt0进行计数以生成并且输出第一计数值“001”作为索引选择信号index_s。地址流水线电路140可以输出对应于具有与索引选择信号index_s相同的值的第一索引index0的第一目标地址信号addr_t0。随后,当第二写入控制信号wt1被输入到索引检测器143时,索引检测器143的第二计数器143-1可以对第二写入控制信号wt1进行计数以生成并且输出第二计数值“010”作为索引选择信号index_s。地址流水线电路140可以输出对应于具有与索引选择信号index_s相同的值的第二索引index1的第二目标地址信号addr_t1。此后,当第三写入控制信号wt2被输入到索引检测器143时,索引检测器143的第二计数器143-1可以对第三写入控制信号wt2进行计数以生成并且输出第三计数

值“011”作为索引选择信号index_s。地址流水线电路140可以输出对应于具有与索引选择信号index_s相同的值的第三索引index2的第三目标地址信号addr_t2。

48.根据上述地址流水线电路140,可以通过由第一ewm命令生成的第一读取控制信号rd0将与第一地址信号addr_0和第一索引index0相对应的第一目标地址信号addr_t0存储到地址存储部141中。因此,如果第一地址信号addr0被激活直到第一输入数据da1和第二输入数据da2从第一存储体121和第二存储体122发送到乘法器电路130为止,则pim器件100可以正常操作。即,可以不需要保持第一地址信号addr0的激活状态直到结果数据da_rst被存储到第三存储体123中为止。第一地址信号addr0的该时序也可以同样地适用于第二地址信号addr1和第三地址信号addr2。

49.从地址流水线电路140输出的目标地址信号addr_t可以对应于具有与索引选择信号index_s相同的值的索引。索引可以具有读取控制信号rd的计数值,以及索引选择信号index_s可以具有写入控制信号wt的计数值。因此,索引的值等于索引选择信号index_s的值可以意味着读取控制信号rd和写入控制信号wt是由相同的ewm命令生成的信号。因此,发送到第三存储体123的结果数据da_rst和目标地址信号addr_t可以对应于与一个ewm计算有关的结果数据da_rst和地址信号addr。

50.图4是示出由图1所示的pim器件100执行的ewm处理的时序图,以及图5至图13是示出在图4所示的时序图的相应的时间点执行的ewm计算的框图。参照图4,pim器件100可以以cas到cas命令延迟时间“tccd”(t1-t2、t2-t4、t4-t7)的间隔顺次接收第一至第三ewm命令ewmul0~ewmul2。也就是说,在第一时间点“t1”,pim器件100可以接收第一ewm命令ewmul0。pim器件100可以基于第一ewm命令ewmul0执行第一ewm计算。在从第一时间点“t1”开始经过cas到cas命令延迟时间“tccd”时的第二时间点“t2”,pim器件100可以接收第二ewm命令ewmul1。pim器件100可以基于第二ewm命令ewmul1执行第二ewm计算。在从第二时间“t2”开始经过cas到cas命令延迟时间“tccd”时的第四时间点“t4”,pim器件100可以接收第三ewm命令ewmul2。pim器件100可以基于第三ewm命令ewmul2执行第三ewm计算。根据本实施方式,第一至第三ewm计算可以被执行成在时序图中彼此部分交叠。

51.参照图4和图5,当在第一时间点“t1”将第一ewm命令ewmul0发送到pim器件100时,pim器件100的命令/地址解码器110可以对第一ewm命令ewmul0进行解码以在从第一时间点“t1”开始经过特定时间时的第三时间点“t3”生成并且输出第一读取控制信号rd0和第一地址信号addr0。第一时间点“t1”和第三时间点“t3”之间的间隔时间可以对应于命令/地址解码器110对第一ewm命令ewmul0进行解码所花费的时间。由命令/地址解码器110生成的第一读取控制信号rd0和第一地址信号addr0可以被发送到地址流水线电路140以及存储器电路120的第一和第二存储体121和122。发送到存储器电路120的第一和第二存储体121和122的第一读取控制信号rd0可以激活第一和第二存储体121和122中的由第一地址信号addr0指定的列线。地址流水线电路140可以将用作第一目标地址信号addr_t0的第一地址信号addr0存储到地址存储部141中。地址流水线电路140的索引生成器142可以对第一读取控制信号rd0进行计数以生成索引“001”以及可以将索引“001”发送到地址存储部141。从索引生成器142输出的索引“001”可以被存储到地址存储部141中以用作与第一目标地址信号addr_t0相对应的第一索引index0。

52.参照图4和图6,在从第一ewm命令ewmul0被发送到pim器件100时的第一时间点“t1”开始经过cas到cas命令延迟时间“tccd”时的第二时间点“t2”,第二ewm命令ewmul1可以被发送到pim器件100。当第二ewm命令ewmul1在第二时间点“t2”被发送到pim器件100时,pim器件100的命令/地址解码器110可以对第二ewm命令ewmul1进行解码以在从第二时间点“t2”开始经过特定时间时的第五时间点“t5”生成并且输出第二读取控制信号rd1和第二地址信号addr1。第五时间点“t5”可以对应于从第一时间点“t1”开始经过命令/地址解码器110对第一ewm命令ewmul0进行解码和发送第一读取控制信号rd0和第一地址信号addr0所花费的总时间的时间点。即,命令/地址解码器110可以在从第一时间点“t1”直到第三时间点“t3”的时段期间执行第一ewm命令ewmul0的解码操作,以及在第三时间点“t3”从命令/地址解码器110输出的第一地址信号addr0可以被发送到第一和第二存储体121和122直到第五时间点“t5”为止。

53.在第五时间点“t5”从命令/地址解码器110输出的第二读取控制信号rd1和第二地址信号addr1可以被发送到地址流水线电路140以及存储器电路120的第一和第二存储体121和122。发送到第一和第二存储体121和122的第二读取控制信号rd1可以激活第一和第二存储体121和122中的由第二地址信号addr1指定的列线。地址流水线电路140可以将用作第二目标地址信号addr_t1的第二地址信号addr1存储到地址存储部141中。地址流水线电路140的索引生成器142可以对第二读取控制信号rd1进行计数以生成索引“010”以及可以将索引“010”发送到地址存储部141。从索引生成器142输出的索引“010”可以被存储到地址存储部141中以用作与第二目标地址信号addr_t1相对应的第二索引index1。

54.参照图4和图7,在从生成第一读取控制信号rd0时的第三时间点“t3”开始经过特定时间时的第六时间点“t6”,命令/地址解码器110可以生成并且输出第一算术控制信号mul0。第一算术控制信号mul0可以被发送到乘法器电路130。在从命令/地址解码器110输出第一算术控制信号mul0时的第六时间点“t6”,第一输入数据da1_0和第二输入数据da2_0可以开始从第一和第二存储体121和122发送到乘法器电路130。第一输入数据da1_0和第二输入数据da2_0可以从第一和第二存储体121和122发送到乘法器电路130直到生成下一个算术控制信号mul为止。第一输入数据da1_0和第二输入数据da2_0可以通过由第一地址信号addr0指定的列线从第一和第二存储体121和122发送到乘法器电路130。乘法器电路130可以响应于从命令/地址解码器110输出的第一算术控制信号mul0而对第一输入数据da1_0和第二输入数据da2_0执行第一ewm计算。

55.参照图4和图8,在从第二ewm命令ewmul1被发送到pim器件100时的第二时间点“t2”开始经过cas到cas命令延迟时间“tccd”时的第四时间点“t4”,第三ewm命令ewmul2可以被发送到pim器件100。pim器件100的命令/地址解码器110可以对第三ewm命令ewmul2进行解码以在从第四时间点“t4”开始经过特定时间时的第八时间点“t8”生成并且输出第三读取控制信号rd2和第三地址信号addr2。第八时间点“t8”可以对应于从第二时间点“t2”开始经过命令/地址解码器110对第二ewm命令ewmul1进行解码以及发送第二读取控制信号rd1和第二地址信号addr1所花费的总时间的时间点。即,命令/地址解码器110可以在从第二时间点“t2”直到第五时间点“t5”的时段期间执行第二ewm命令ewmul1的解码操作,以及在第五时间点“t5”从命令/地址解码器110输出的第二地址信号addr1可以被发送到第一和第二存储体121和122直到第八时间点“t8”为止。

56.在第八时间点“t8”从命令/地址解码器110输出的第三读取控制信号rd2和第三地

址信号addr2可以被发送到地址流水线电路140以及存储器电路120的第一和第二存储体121和122。发送到第一和第二存储体121和122的第三读取控制信号rd2可以激活第一和第二存储体121和122中的由第三地址信号addr2指定的列线。地址流水线电路140可以将用作第三目标地址信号addr_t2的第三地址信号addr2存储到地址存储部141中。地址流水线电路140的索引生成器142可以对第三读取控制信号rd2进行计数以生成索引“011”以及可以将索引“011”发送到地址存储部141。从索引生成器142输出的索引“011”可以被存储到地址存储部141中以用作与第三目标地址信号addr_t2相对应的第三索引index2。

57.参照图4和图9,在从生成第二读取控制信号rd1时的第五时间点“t5”开始经过特定时间时的第九时间点“t9”,命令/地址解码器110可以生成并且输出第二算术控制信号mul1。第二算术控制信号mul1可以被发送到乘法器电路130。在从命令/地址解码器110输出第二算术控制信号mul1时的第九时间点“t9”,第一输入数据da1_1和第二输入数据da2_1可以开始从第一和第二存储体121和122发送到乘法器电路130。第一输入数据da1_1和第二输入数据da2_1可以通过由第二地址信号addr1指定的列线从第一和第二存储体121和122发送到乘法器电路130。乘法器电路130可以响应于从命令/地址解码器110输出的第二算术控制信号mul1对第一输入数据da1_1和第二输入数据da2_1执行第二ewm计算。

58.参照图4和图10,在从生成第一算术控制信号mul0时的第六时间点“t6”开始经过特定时间时的第十时间点“t10”,命令/地址解码器110可以生成并且输出第一写入控制信号wt0。第一写入控制信号wt0可以被发送到第三存储体123和地址流水线电路140。乘法器电路130还可以将通过第一输入数据da1_0和第二输入数据da2_0的第一ewm计算生成的第一结果数据da_rst0(对应于图2的第一结果数据da_rst_0)发送到第三存储体123。地址流水线电路140的索引检测器143可以对第一写入控制信号wt0进行计数以生成索引选择信号index_s“001”,以及可以将索引选择信号index_s“001”发送到地址存储部141。地址存储部141可以将对应于具有与索引选择信号index_s“001”相同的值的第一索引index0“001”第一目标地址信号addr_t0(即,第一地址信号addr0)发送到第三存储体123。第三存储体123可以将从乘法器电路130输出的第一结果数据da_rst0存储到第三存储体123的由从地址流水线电路140输出的第一地址信号addr0指定的区域中。

59.参照图4和图11,在从生成第三读取控制信号rd2时的第八时间点“t8”开始经过特定时间时的第十一时间点“t11”,命令/地址解码器110可以生成并且输出第三算术控制信号mul2。第三算术控制信号mul2可以被发送到乘法器电路130。在从命令/地址解码器110输出第三算术控制信号mul2的第十一时间点“t11”,第一输入数据da1_2和第二输入数据da2_2可以开始从第一和第二存储体121和122发送到乘法器电路130。在第一输入数据da1_2和第二输入数据da2_2从第一和第二存储体121和122发送到乘法器电路130之前,第一输入数据da1_2和第二输入数据da2_2可以存储在第一和第二存储体121和122的由第三地址信号addr2指定的区域中。乘法器电路130可以响应于从命令/地址解码器110输出的第三算术控制信号mul2执行第一输入数据da1_2和第二输入数据da2_2的第三ewm计算。

60.参照图4和图12,在从生成第二算术控制信号mul1时的第九时间点“t9”开始经过特定时间时的第十二时间点“t12”,命令/地址解码器110可以生成并且输出第二写入控制信号wt1。第二写入控制信号wt1可以被发送到第三存储体123和地址流水线电路140。乘法器电路130还可以将通过第一输入数据da1_1和第二输入数据da2_1的第二ewm计算生成的

第二结果数据da_rst1(对应于图2的第二结果数据da_rst_1)发送到第三存储体123。地址流水线电路140的索引检测器143可以对第二写入控制信号wt1进行计数以生成索引选择信号index_s“010”以及可以将索引选择信号index_s“010”发送到地址存储部141。地址存储部141可以将对应于具有与索引选择信号index_s“010”相同的值的第二索引index1“010”的第二目标地址信号addr_t1(即,第二地址信号addr1)发送到第三存储体123。第三存储体123可以将从乘法器电路130输出的第二结果数据da_rst1存储到第三存储体123的由从地址流水线电路140输出的第二地址信号addr1指定的区域中。

61.参照图4和图13,在从生成第三算术控制信号mul2的第十一时间点“t11”开始经过特定时间时的第十三时间点“t13”,命令/地址解码器110可以生成并且输出第三写入控制信号wt2。第三写入控制信号wt2可以被发送到第三存储体123和地址流水线电路140。乘法器电路130还可以将通过第一输入数据da1_2和第二输入数据da2_2的第三ewm计算生成的第三结果数据da_rst2发送到第三存储体123。地址流水线电路140的索引检测器143可以对第三写入控制信号wt2进行计数以生成索引选择信号index_s“011”,以及可以将索引选择信号index_s“011”发送到地址存储部141。地址存储部141可以将对应于具有与索引选择信号index_s“011”相同的值的第三索引index2“011”的第三目标地址信号addr_t2(即,第三地址信号addr2)发送到第三存储体123。第三存储体123可以将从乘法器电路130输出的第三结果数据da_rst2存储到第三存储体123的由从地址流水线电路140输出的第三地址信号addr2指定的区域中。

62.图14是示出根据本教导的另一实施方式的pim器件200的框图。图15是示出图14所示的pim器件200中包括的乘法累加(mac)电路230的框图。在图14中,与图1中使用的相同的附图标记或相同的参考符号可以表示相同的部件。因此,在下文中将省略与参照图1描述的相同的部件的详细描述以避免重复说明。参照图1、图14和图15,pim器件100和pim器件200之间的区别在于,pim器件200包括mac电路230,而pim器件100包括乘法器电路130。

63.具体地,如图15所示,mac电路230可以包括乘法电路310、数据输出选择电路320、加法器树330和累加电路340。乘法电路310可以包括多个乘法器,例如,并行设置的第一至第八乘法器mul0~mul7。乘法器mul0~mul7中的每个可以执行第一输入数据da1和第二输入数据da2的乘法计算以生成并且输出乘法计算的结果数据。

64.数据输出选择电路320可以通过第一输出线或第二输出线输出由乘法电路310生成的乘法结果数据。在一个实施方式中,数据输出选择电路320可以包括多个解复用器,例如,并行设置的第一至第八解复用器demux0~demux7。构成数据输出选择电路320的解复用器的数量可以等于包括在乘法电路310中的乘法器的数量。解复用器demux0~demux7中的每个可以具有一个输入端子和两个输出端子。第一至第八解复用器demux0~demux7的输入端子可以分别耦接至第一至第八乘法器mul0~mul7的输出端子。例如,第一解复用器demux0的输入端子可以耦接至第一乘法器mul0的输出端子,以及第二解复用器demux1的输入端子可以耦接至第二乘法器mul1的输出端子。以相同的方式,第八解复用器demux7的输入端子可以耦接到第八乘法器mul7的输出端子。解复用器demux0~demux7中的每个可以通过两个输出线(即,第一和第二输出线)中的由发送到数据输出选择电路320的选择控制信号cs选择的一个输出线输出从乘法器mul0~mul7中的一个接收到的乘法结果数据。例如,当具有逻辑“低”电平的选择控制信号cs被输入到数据输出选择电路320时,解复用器

demux0~demux7可以通过解复用器demux0~demux7的第一输出线输出乘法电路310生成的乘法结果数据。相反,当具有逻辑“高”电平的选择控制信号cs被输入到数据输出选择电路320时,解复用器demux0~demux7可以通过解复用器demux0~demux7的第二输出线输出乘法电路310生成的乘法结果数据。

65.加法器树330可以包括被排列为具有级层结构的多个加法器,例如,树结构。在本实施方式中,构成加法器树330的多个加法器中的每个可以使用半加器来实现。然而,包括使用半加器实现的加法器树330的本实施方式可以仅是本公开的示例。即,在一些其他实施方式中,构成加法器树330的多个加法器中的每个可以使用全加器来实现。加法器树330的最高级(即,第一级st1)可以包括并行设置的四个第一加法器。位于第一级st1下方的第二级st2可以包括并行设置的两个第二加法器。对应于加法器树330的最低级的第三级st3可以位于第二级st2之下,以及可以仅包括单个加法器。

66.设置在第一级stl中的每个加法器的第一输入端子和第二输入端子可以耦接到构成数据输出选择电路320的第一至第八解复用器demux0~demux7中的两个解复用器的第一输出线中的相应的第一输出线。因此,设置在第一级st1中的每个加法器可以执行对数据输出选择电路320中包括的两个解复用器的输出数据(即,乘法结果数据)的加法计算以生成并且输出加法结果数据。此外,第二级st2中的每个加法器可以执行对第一级st1中的两个加法器的输出数据(即,加法结果数据)的加法计算以生成并且输出加法结果数据。此外,第三级st3中的加法器可以执行对第二级st2中的两个加法器的输出数据(即,加法结果数据)的加法计算以生成并且输出加法结果数据。

67.累加电路340可以包括累加器341和锁存电路342。累加器341可以执行用于将从加法器树330输出的加法结果数据与从锁存电路342输出的反馈数据相加的加法计算,从而生成并且输出累加加法结果数据。累加加法结果数据可以被发送到锁存电路342。在一个实施方式中,累加器341可以使用半加器来实现。锁存电路342可以锁存累加加法结果数据以将累加加法结果数据的锁存数据反馈到累加器341或将累加加法结果数据的锁存数据输出到耦接到mac电路230的外部设备。在一个实施方式中,锁存电路342可以包括触发器。

68.根据本实施方式,pim器件200的mac电路230可以执行mac算术运算或ewm算术运算。当mac电路230执行mac算术运算时,构成数据输出选择电路320的解复用器demux0~demux7的输出数据可以被发送到构成加法器树330的第一级st1的加法器。设置在加法器树330的第三级st3中的加法器的输出数据可以被累积地加到与包括在累加电路340中的锁存电路342的输出数据相对应的反馈数据上。

69.当mac电路230执行ewm算术运算时,构成数据输出选择电路320的解复用器demux0~demux7的输出数据不被发送到加法器树330,而是被发送到耦接到mac电路230的外部设备。为了使mac电路230执行ewm算术运算,可以将第一输入数据da1_0~da1_7输入到第一至第八乘法器mul0~mul7的第一输入端子中的相应的第一输入端子,而第二输入数据da2_0~da2_7可以输入到第一至第八乘法器mul0~mul7的第二输入端子中的相应的第二输入端子。如参照图1描述的,可以从第一存储体121输出第一输入数据da1_0~da1_7,以及可以从第二存储体122输出第二输入数据da2_0~da2_7。当对第一矩阵和第二矩阵执行ewm算术运算时,第一输入数据da1_0~da1_7可以是第一矩阵的元素,以及第二输入数据da2_0~da2_7可以是第二矩阵的元素。

70.当mac电路230执行ewm算术运算时,输入到第一至第八乘法器mul0~mul7中的每个的第一输入数据和第二输入数据可以是位于第一和第二矩阵中的相同位置的元素。例如,输入到第一乘法器mul0的第一输入端子的第一输入数据da1_0可以是位于第一矩阵的第一行和第一列的交点处的元素,以及输入到第一乘法器mul0的第二输入端子的第二输入数据da2_0可以是位于第二矩阵的第一行和第一列的交点处的元素。类似地,输入到第二乘法器mul1的第一输入端子的第一输入数据da1_1可以是位于第一矩阵的第一行和第二列的交点处的元素,以及输入到第二乘法器mul1的第二输入端子的第二输入数据da2_1可以是位于第二矩阵的第一行和第二列的交点处的元素。第一至第八乘法器mul0~mul7可以对第一输入数据da1和第二输入数据da2执行乘法计算以生成第一至第八乘法结果数据dm_0~dm_7以及将其输出到数据输出选择电路320。构成数据输出选择电路320的解复用器demux0~demux7可以基于选择控制信号cs通过解复用器demux0~demux7的第一输出线来输出由第一至第八乘法器mul0~mul7生成的第一至第八乘法结果数据dm_0~dm_7。

71.除了mac电路230的操作之外,pim器件200可以执行与参照图1至图13描述的pim器件100相同的操作。具体地,当第一至第八ewm命令ewmul0~ewmul7被顺次输入至pim器件200时,第一输入数据da1_0~da1_7和第二输入数据da2_0~da2_7可以通过读取控制信号rd和第一至第八地址信号addr0~addr7而从第一存储体121和第二存储体122顺次发送到mac电路230。在这种情况下,第一至第八地址信号addr0~addr7可以顺次存储到地址流水线电路140中以用作与第一至第八索引index0~index7匹配的第一至第八目标地址信号addr_t0~addr_t7。mac电路230可以响应于第一至第八算术控制信号mul0~mul7而执行对第一输入数据da1_0~da1_7和第二输入数据da2_0~da2_7的ewm计算,从而生成并且输出第一至第八结果数据da_rst0~da_rst7。第一至第八结果数据da_rst0~da_rst7可以被发送到第三存储体123。第三存储体123可以响应于写入控制信号wt而将第一至第八结果数据da_rst0~da_rst7存储到由从地址流水线电路140输出的第一至第八目标地址信号addr_t0~addr_t7指定的区域中。

72.出于说明性目的,以上已经给出了本教导的有限数量的可能实施方式。本领域普通技术人员将理解,各种修改、添加和替换是可能的。尽管本专利文件包含许多细节,但是这些细节不应被解释为对本教导的范围或要求保护的范围的限制,而应被解释为对特定实施方式而言特定的特征的描述。在本专利文件中以分立的实施方式的情形描述的某些特征也可以在单个实施方式中组合实现。相反,以单个实施方式的情形描述的各种特征也可以分立地在多个实施方式中实现或以任何合适的子组合来实现。而且,尽管以上可以将特征描述为以某些组合起作用并且甚至最初如此要求保护,但是在某些情况下,可以从该组合中分离出要求保护的组合中的一个或更多个特征,以及要求保护的组合可以指向子组合或子组合的变形。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。