1.本发明涉及一种用于产生适合于引起生物组织的电穿孔的波形的电外科产生器。确切来说,本发明涉及一种用于电外科产生器的脉冲产生电路,在电外科产生器中,所述脉冲产生电路被配置成产生持续时间小于10ns的高电压脉冲。

背景技术:

2.电外科产生器普遍存在于医院手术室中,用于开腹和腹腔镜手术,并且也越来越多地出现在内窥镜检查套件中。在内窥镜手术中,通常穿过在内窥镜内部的管腔插入电外科附件。考虑到腹腔镜手术的等效进入通道,此种管腔的内径相当窄且长度较大。

3.wo 2019/185331 a1公开一种能够以引起生物组织的电穿孔的波形供应能量的电外科产生器。该电外科产生器可包括电穿孔波形供应单元,该电穿孔波形供应单元与产生用于治疗的微波电磁信号和射频电磁信号的装置集成在一起。该电外科产生器可被配置成沿着共同的馈送电缆线递送不同类型的能量。该电穿孔波形供应单元包括dc电力供应器和dc脉冲产生器。该dc电力供应器可包括用于对可调整电压供应器输出的电压进行升频转换的dc-dc转换器。每一dc脉冲可具有在1ns到10ms范围内的持续时间和在10v到10kv范围内的最大振幅。

4.近年来,超短电场脉冲产生器具有许多发展[1]。在纳秒范围内的超短电场脉冲具有许多应用。这些应用包括:例如粒子测量、摄影、超宽带雷达检测和医学应用[2]-[3]。

[0005]

有许多方法能产生上升时间和下降时间为2ns的高振幅纳秒脉冲式电场。通常,与火花间隙、marx bank或二极管和激光断开开关技术相关的基于同轴传输线的实施方式(诸如,blumlein)已被用于产生高电压纳秒脉冲[1]。

技术实现要素:

[0006]

总体上来说,本发明提供一种用于电外科产生器的脉冲产生电路,所述脉冲产生电路被配置成产生适合于引起生物细胞的电穿孔的持续时间小于10ns的高电压脉冲。确切来说,本文中所公开的脉冲产生电路可适合于产生展现出

‘

平顶’轮廓(即具有急剧(例如小于2ns)的上升时间和下降时间、具有最小振铃(ringing))的双极脉冲。如下文更详细地阐释,这可通过与相对于传输线和快速开关元件而在适合的位置放置一对负载输出(针对正脉冲和负脉冲)相结合的开路传输线技术来达成。

[0007]

根据本发明,提供一种用于电外科产生器的双极脉冲产生电路,所述双极脉冲产生电路包括:电压源,所述电压源可经由开关元件连接到负载;同轴传输线,所述同轴传输线具有通过介电材料与外导体隔开的内导体,其中所述内导体具有连接在所述开关元件的输入端与所述电压源之间的第一端和处于开路状况的第二端,由此所述同轴传输线在所述开关元件处于关断状态时被所述电压源充电,并且在所述开关元件处于接通状态时放电;第一输出端(output),所述第一输出端能够连接到所述负载,其中所述第一输出端位于所述开关元件的输出端与接地端(ground)之间以在所述同轴传输线放电时支持正脉冲;以及

第二输出端,所述第二输出端能够连接到所述负载,其中所述第二输出端位于所述同轴传输线的所述外导体与接地端之间以在所述同轴传输线放电时支持负脉冲,其中所述同轴传输线的阻抗被配置成与(i)所述开关元件的阻抗、(ii)所述负载在所述第一输出端处的阻抗和(iii)所述负载在所述第二输出端处的阻抗的总和匹配。通过此结构,所述电路可产生超短(例如小于10ns)持续时间的双极脉冲,其中所述脉冲的正部分与负部分是对称的。使阻抗匹配能确保将反射最小化或消除。此种电路配置可产生具有短持续时间(由同轴传输线的长度控制)的平顶脉冲(由于匹配的阻抗状况)。

[0008]

在一个实例中,延迟线可连接到所述第一输出端或所述第二输出端,由此所述第一输出端和所述第二输出端处的正脉冲和负脉冲的供应循序地发生。例如,延迟线可连接在所述同轴传输线的所述外导体与所述第二输出端之间。所述延迟线的长度能够被选择成(或能够被调整成)控制相对于正脉冲的初始值(beginning)在第二输出端处出现的负脉冲的量。可包括连接在所述第一输出端和所述第二输出端中的每一者处的延迟线,以提供对所输出的双极波形的轮廓的完全控制。特别地,可能期望提供具有可调整长度的延迟线,以使得正脉冲和负脉冲的分离可被独立地控制。所述延迟线可具有任何适合的结构。例如,它可以是另一长度的同轴传输线。

[0009]

所述开关元件可包括:多个串联连接的雪崩晶体管;和触发脉冲产生器,所述触发脉冲产生器被配置成产生触发脉冲以激活所述多个串联连接的雪崩晶体管。这由于串联连接的雪崩晶体管的级联效应而使得正脉冲和负脉冲能够具有超短的上升时间和下降时间以及适合于电穿孔的振幅。特别地,输出的振幅可以是500v或更大,例如1kv或更大,但不超过所述多个串联连接的雪崩晶体管中的任一个串联连接的雪崩晶体管两端的集电极-基极击穿电压。

[0010]

所述同轴传输线可具有被选择成提供等于或小于5ns的线延迟的长度。脉冲持续时间是所述线延迟的两倍,因此输出脉冲可具有等于或小于10ns的持续时间。

[0011]

所述同轴传输线可由电压源通过具有高阻抗(例如1mω)的电阻器充电。因此,所述电路可被视为在开关元件处于关断状态时包括第一回路并且在开关元件处于接通状态时包括第二回路。在所述第一回路中,电流从电压源流过电阻器从而给所述同轴传输线充电。在所述第二回路中,电流从所述同轴传输线流过开关元件并流到负载。

[0012]

触发脉冲可包括ttl信号。触发脉冲产生器可以是适合于产生此种信号的任何源,例如微处理器等。触发脉冲可具有比所述多个雪崩晶体管中的每一个雪崩晶体管的发射极-基极击穿电压小的电压。触发脉冲的持续时间可长于来自同轴传输线的脉冲的持续时间,以确保所述开关元件处于接通状态长达足以使同轴传输线完全放电的时间。在一个实例中,触发脉冲具有5v的电压和600ns的持续时间。

[0013]

触发脉冲产生器可经由变压器连接到所述多个串联连接的雪崩晶体管。这意味着触发信号在基极与发射极之间浮动,并且因此独立于经过晶体管并进入负载中的电压。在一个实例中,可在所述多个串联连接的雪崩晶体管中的第一晶体管的集电极与发射极之间施加触发脉冲。第一晶体管可以是距所述同轴传输线最远的晶体管。

[0014]

二极管可与所述多个串联连接的雪崩晶体管中的每一个串联连接的雪崩晶体管并联连接以将横跨每一个晶体管的电压钳制成小于其集电极-基极击穿电压。这会保护晶体管。

[0015]

所述多个串联连接的雪崩晶体管中的每一个晶体管可以是同一的(identical),以使得电压源的电压均匀地划分在所述晶体管之间。

[0016]

如上文所述,本发明特别适合用于电外科。因此,负载可包括能够递送用于对生物组织进行电穿孔的单极脉冲的电外科器械。

[0017]

在另一实例中,本发明可提供一种具有如上文所阐述的脉冲产生电路的电外科产生器。所述脉冲产生电路可被配置成产生电穿孔波形,即适合于引起生物组织的电穿孔的一阵能量。电穿孔波形可包括一个或多个迅速高电压脉冲。每一脉冲可具有在1ns到10μs范围内、优选地在1ns到10ns范围内的脉冲宽度,但本发明未必仅限于此范围。较短持续时间的脉冲(例如,等于或小于10ns)可优选地用于可逆电穿孔。

[0018]

优选地,每一脉冲的上升时间等于或小于脉冲持续时间的90%,更优选地等于或小于脉冲持续时间的50%,且最优选地等于或小于脉冲持续时间的10%。

[0019]

每一脉冲可具有在10v到10kv范围内,优选地在1kv到10kv范围内的振幅。每一脉冲可以是来自接地电势的正脉冲。

[0020]

电穿孔波形可以是单个脉冲或多个脉冲,例如周期性的一连串脉冲。所述波形可具有等于或小于50%(例如,在0.5%到50%的范围内)的工作循环(duty cycle)。

附图说明

[0021]

下文参考附图论述本发明的实施方案,在附图中:

[0022]

图1是图解说明具有理想开关的放电线产生器的原理的示意图;

[0023]

图2a是示出在图1中的(i)传输线和(ii)负载处的电压波形的曲线图;

[0024]

图3a是表示图1的呈dc模型的开路传输线的示意图;

[0025]

图3b是表示图1的呈传输线模型的开路传输线的示意图;

[0026]

图4是示出图1的具有用于产生正超短电场脉冲的雪崩晶体管的开路传输线的示意图;

[0027]

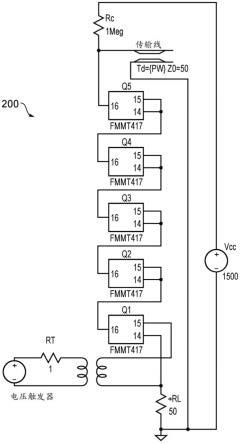

图5是单极超短电场脉冲产生器的模拟ltspice电路的图;

[0028]

图6是示出从图5的ltspice电路产生的具有各种持续时间的脉冲的曲线图;

[0029]

图7是在具有匹配的35ω负载的情况下从图5中的电路观测到的单极正脉冲;

[0030]

图8是示出图1的具有用于产生负超短电场脉冲的雪崩晶体管的开路传输线的示意图;

[0031]

图9是被配置成产生负脉冲的单极超短电场脉冲产生器的模拟ltspice电路的图;

[0032]

图10是在具有匹配的35ω负载的情况下从图9中的电路观测到的单极负脉冲;

[0033]

图11a是不具有延迟线的双极超短电场脉冲产生器的模拟ltspice电路的图;

[0034]

图11b是在负载之前具有延迟线的双极超短电场脉冲产生器的模拟ltspice电路的图;

[0035]

图12a是描绘在图11a的电路中的各个点处观测到的电压的曲线图;并且

[0036]

图12b是描绘在图11a的电路中的各个点处观测到的电压的曲线图。

具体实施方式

[0037]

可通过使用开路同轴传输线作为高q存储元件来产生超短脉冲,所述高q存储元件

由散布的串联的具有最小电阻和分路电导的电感器和分路电容器组成。经由快速开关元件使开端式延迟线放电提供了以简单且经济适用的方式产生具有小于2ns的急剧下降时间的

‘

平项’矩形脉冲的手段。通过高阻抗电阻器rc将特性阻抗为z0、长度为l且介电常数为εr的同轴传输线充电到电压电平v

cc

。所述线将具有相关联的延迟时间t,所述延迟时间由以下方程式得出:

[0038][0039]

其中c是光速(2.99

×

108m/s)。

[0040]

由此可知,与传输线相关联的脉冲持续时间是:

[0041][0042]

可通过闭合开关元件来通过r

l

使传输线放电来在负载r

l

上产生超短电场脉冲。开关元件确定超短电场脉冲的上升时间,而传输线确定脉冲持续时间(或宽度)和下降时间。

[0043]

如上文所阐释,负载处的脉冲的持续时间将是传输线的相关联延迟时间的两倍。

[0044]

图1图解说明以理想开关作为开关元件的开路传输线技术的原理。

[0045]

图2示出在(i)传输线z0和(ii)负载r

l

处从图1的系统获得的电压波形。

[0046]

传输线z0的特性阻抗与负载r

l

之间的关系在两方面对于开路同轴传输线技术的性能是不可或缺的,这可通过使用直通电路(dc)理论和传输线理论对配置进行建模来理解。

[0047]

在dc理论中,z0与r

l

之间的关系仿效电势分压器,如图3a中所示。它们的关系决定了负载处的脉冲振幅v

l

:

[0048][0049]

如果阻抗z0与r

l

相同,则负载处的脉冲的最大振幅v

lmax

将是传输线被充电到的电压的一半:

[0050][0051]

使用传输线模型,可如图3b中所示地表示系统。在此模型中,z0与r

l

之间的关系决定了反射系数,且因此决定了负载处的脉冲形状。如果r

l

与z0相同,则反射系数将是零且负载处将看不到次级脉冲或初级脉冲的反射:

[0052][0053]

因此,z0与r

l

的关系决定负载处的脉冲的两个关键方面:(i)脉冲振幅和(ii)脉冲形状(由任何反射所致)。从以上分析可知,最佳脉冲形状和参数、传输线z0的特性阻抗,以及负载r

l

应匹配。

[0054]

脉冲的其它特征由电路的其它参数控制。例如,脉冲上升时间由开关元件的行为决定,而脉冲宽度由传输线的长度决定,如上文所论述。

[0055]

本发明的实施方案中的这种开关元件优选地由雪崩晶体管的堆叠阵列提供。已知雪崩晶体管可以提供对上升时间低至300ps的高电压的可靠且可重复的高速开关,如果在实施电路时考虑微波组件布局技术,则这种高速开关可以在实践中实现。雪崩晶体管利用双极结型晶体管的负电阻特性区,所述负电阻特性区是由在共发射极击穿区中的运行而产生的。当基极电流ib=0a且发射极电流ie=0a时,雪崩区位于集电极发射极(v

ceo

)与集电极

基极(v

cbo

)电压之间。

[0056]

图4是利用与作为快速开关元件的雪崩晶体管组合的开路传输线技术的脉冲产生电路100的示意图。电路功能是基于开路传输线横跨雪崩晶体管向负载r

l

中的放电。

[0057]

单个雪崩晶体管电路可被配置成具有双稳态运行,其中若z0=r

l

,则输出端处的最大脉冲振幅限制于晶体管的集电极-发射极击穿电压bv

ces

的值的一半。高于晶体管的bv

ces

的供应电压v

cc

将永久地击穿且损坏作为开关元件的雪崩晶体管。

[0058]

首先,能量经由回路1中的小电流被存储在同轴传输线中。对晶体管的基极的正触发将突然

‘

接通’所述晶体管。存储在传输线中的能量将同时沿着回路2以高电流的形式释放,从而在r

l

上产生脉冲。对基极的触发的宽度长于2t,即负载处所需的脉冲宽度。

[0059]

图5示出作为本发明的实施方案的脉冲产生电路200。脉冲产生电路200类似于图4中所示的电路,但替代单个雪崩晶体管,存在多个(在此实例中五个)串联连接的雪崩晶体管。所述多个串联连接的雪崩晶体管有效地作为单个雪崩晶体管组合运行。这意味着开路传输线是横跨堆叠晶体管而向负载放电,从而产生导致负载处的脉冲振幅成比例地变高的级联效应。在此实例中,该雪崩晶体管中的每一个雪崩晶体管是同一的,以使得供应电压v

cc

相等地分布在串联链中的雪崩晶体管中的每一个雪崩晶体管上。

[0060]

在此布置中,可产生的最大脉冲振幅取决于堆叠雪崩晶体管n的数目。产生特定脉冲振幅v

l

所需的雪崩晶体管的数目可表示为

[0061][0062]

其中bv

cbo

是每一个雪崩晶体管的集电极-基极击穿电压。如果r

l

=z0,则最大脉冲振幅v

lmax

因此可表示为

[0063][0064]

在脉冲产生电路200中,堆叠了五个fmmt417雪崩晶体管。每一个晶体管具有100v的集电极-发射极击穿电压bv

ceo

和320v的集电极-基极击穿电压bv

cbo

。图5中所示的电路是使用ltspice模型模拟的。fmmt417的spice模型是直接从制造商的网站获取的。源电阻rc是1mω,传输线的特性阻抗z0是50ω,源电压v

cc

是1.5kv。

[0065]

所述电路可包括与每一个晶体管并联连接的二极管(未示出),以对电压进行钳制以确保横跨每一个晶体管的电压不超过其集电极-基极击穿电压。如此可延长晶体管的寿命且确保通过触发信号进行触发。

[0066]

所述触发信号可由任何适合的源提供。优选地,所述触发信号由ttl源或微控制器产生。在此实例中,触发信号包括具有600ns的持续时间和5v的振幅以及20ms的脉冲周期(重复周期)的脉冲。具有5v的触发信号是有利的,原因在于它小于晶体管的发射极-基极击穿电压。

[0067]

触发信号的脉冲宽度被布置成长于需要从传输线产生的脉冲。在此种情形中选择600ns的持续时间是为了提供允许整个传输线放电的安全余裕。

[0068]

触发信号重复率(脉冲周期)受开路充电传输线再次充电到全容量所花费的时间限制。

[0069]

变压器被安置在触发信号产生器与堆叠体(stack)中的第一晶体管(即距传输线最远的晶体管)的基极和发射极之间。此配置意味着触发脉冲是浮动的,且因此在第一晶体

管的基极与发射极之间均应相同,无论经过晶体管并进入负载中的电压如何。因此,负载处的脉冲的振幅应随堆叠体中的晶体管的数目而线性地增大。变压器可以是具有1∶1绕组比率和高电压隔离的1-emr-046栅极驱动变压器。

[0070]

在使用中,五个堆叠雪崩晶体管最初处于其关断状态,其中每一个晶体管具有横跨它们的300v(即v

cc

/n)。当正触发信号被施加到第一晶体管q1的基极时,q1被

‘

接通’且使得其集电极电压接近接地电势。这使得第二晶体管q2具有是集电极-发射极电压的两倍的电压,从而在过电压方面形成了所需的条件,并且因此导致q2的非破坏性雪崩并使得它的集电极接近接地电势。这对链中的下一晶体管形成循序的

‘

连锁’效果,从而使得第一雪崩晶体管q1到最后的雪崩晶体管q5在已充电的开路传输线附近形成过电压。当q5被

‘

接通’时,在负载处产生快速上升时间(<2ns),因此如果r

l

=z0,则允许已充电的开路传输线通过所述负载放电,从而产生宽度为2t且最大振幅为v

cc

/2的脉冲。

[0071]

因此,脉冲产生电路200可用于产生单极超短电场脉冲。

[0072]

图6是示出在一系列传输线长度下获得的电压脉冲的曲线图。在图6中,传输线长度由线延迟t来表征。该曲线图表明传输线长度决定2t的脉冲宽度,即线延迟为5ns、25ns、50ns和100ns的传输线分别产生10ns、50ns、100ns和200ns的脉冲宽度。另外,全部四个脉冲的上升时间是相同的且小于2ns,这强调了开关元件(即五个雪崩晶体管)决定了这个因素。

[0073]

图6中的曲线图表明50ω负载与传输线特性阻抗不匹配,因为在每一信号上都可以看到相对于初级脉冲来说具有较低振幅的次级脉冲。这表明反射(即γ≠0)致使负载不匹配。本发明人已意识到必须补偿晶体管的阻抗以优化脉冲产生电路。在图5中所示的实例中,每一单独晶体管均具有~3ω的阻抗。因此,总共~15ω的阻抗横跨晶体管堆叠体。因此反射系数可表示为

[0074][0075]

其中r

∑

是电路的总阻抗,并且ra是信号雪崩晶体管的阻抗。

[0076]

这解释了在图6中所示的脉冲中观测到的反射,如γ=0.13,并且反射脉冲的振幅是初级脉冲的~13%(r

l

=50ω,nra=(3ω

×

5)=15ω并且z0=50ω)。nra的额外阻抗也影响这种设计的dc分量,该dc分量可重写为:

[0077][0078]

考虑到此点,将负载r

l

的阻抗调整为35ω。此形成负载处出现具有零反射且不具有次级脉冲的单个单极脉冲,如图7中所示。

[0079]

上文在图4和图5中所示的电路被配置成产生正单极脉冲。然而,也可通过改变负载被连接的位置将电路调适成产生负单极脉冲。图8是利用与作为快速开关元件的雪崩晶体管组合的开路传输线技术的脉冲产生电路150的示意图,该脉冲产生电路150类似于图4中的电路100。图8的电路150与图4的电路的不同之处在于负载r

l

被连接成使得当同轴传输线放电时电流在与图4相反的方向上流动。图9示出作为本发明的实施方案的脉冲产生电路250。脉冲产生电路250类似于图5中所示的电路,但负载r

l

被连接成使得当同轴传输线放电时电流在与图5相反的方向上流动。图10示出使用图9中所示的电路250获得的在匹配的35ω负载的情况下观测到的负单极脉冲的曲线图。

[0080]

在上文所论述的概念的发展中,脉冲产生电路可被配置成双极脉冲产生电路。此

种电路的运行可与图4和图9中的单极设计是同一的。

[0081]

图11a是作为双极脉冲产生电路300的实施方案的脉冲产生电路300的示意图。它类似于图4和图9中所示的电路,但脉冲是在两个单独的负载上产生,所述两个单独的负载在图11a中标记为r

l

和r

l-。这些负载位置对应于上文所论述的正脉冲和负脉冲的位置。

[0082]

双极脉冲产生电路300产生双极脉冲,因为横跨r

l

的电压差产生正脉冲,其中横跨r

l-的电压差产生负脉冲。当使用电路300时,同时在r

l

和r

l-处观测到的这些脉冲是对称的,即具有相同的脉冲宽度、上升时间、振幅、重复率,但具有不同的极性。

[0083]

由于此电路中存在两个负载,因此必须修正用于减小反射的优化方程式。对于双极设计来说,总负载阻抗r

∑l

=r

l

r

l-是传输线的外导体与雪崩晶体管q1的发射极之间的阻抗并且是r

l

与r

l-的阻抗的总和。因此,可使用传输线理论将反射系数表示为:

[0084][0085]

∴if r

∑l

=r

l- r

l

=z

0-nra,γ=0

[0086]

类似地,可使用dc理论将负载上的峰间电压v

∑l

表示为:

[0087][0088][0089][0090]

其中v

l

和v

l-分别是正脉冲和负脉冲的振幅。

[0091]

从上文可知,17.5ω的r

l

和r

l-值将产生单个脉冲的双极脉冲,该双极脉冲具有零反射(γ=0)和2t的同时对称脉冲宽度以及<2ns的上升时间。换言之,双极脉冲产生电路300运行以横跨具有2t的脉冲宽度和零反射的r

∑l

在传输线的外导体与雪崩晶体管q1的发射极之间形成振幅为v

∑l

的单个正脉冲。

[0092]

图12a是示出在r

l

处观测到的脉冲310、在r

l-处观测到的脉冲312和在r

∑l

处观测到的脉冲314的曲线图。这些观测结果验证了上文所呈现的理论。在图12a中,5ns传输线在具有同一上升时间(<2ns)的全部三个负载处产生10ns脉冲。当r

l

=r

l-=17.5ω时,没有反射,即

[0093][0094]vl

和v

l-的量值是262.5v,因此峰间电压v

∑l

是520v,此峰间电压与等效单极设计相同。

[0095]

图11b是作为本发明的另一实施方案的双极脉冲产生电路350的示意图。图11b中的电路与图11a的不同之处在于在负载(r

l

和r

l-)中的每一个负载之前提供了延迟线。在一个或两个负载之前放置延迟线允许操控两个脉冲之间的延迟。延迟的脉冲将比非延迟的成对脉冲推后达延迟时间减去脉冲宽度。在图11b中,20ns延迟线被放置在r

l-之前。

[0096]

图12b是与图12a类似的曲线图,该图示出在r

l

处观测到的脉冲310、在r

l-处观测到的脉冲312和在r

∑l

处观测到的脉冲314。图12b证实了引入延迟线的效果,因为图12b中的全部三个脉冲和三个参数均与图12a是同一的。唯一的差异是横跨r

l-的负脉冲比正脉冲推

后10ns(即20ns-10ns)。

[0097]

因此,本文中所论述的双极脉冲产生电路配置能够产生:

[0098]-对称双极脉冲,其中正部分与负部分同时或循序地产生(即具有不同的延迟)

[0099]-零反射但可调整的v

l

和v

l-振幅,由于该振幅由r

l

与r

l-的比率控制,但如果满足r

∑l

=r

l- r

l

=z

0-nra条件,则反射将保持为零。

[0100]

在进一步的发展中,该延迟线中的一个或两个延迟线可具有使得引入的延迟能够被控制的可调整长度。这可允许动态(on the fly)调整正脉冲与负脉冲的分离,例如以使得器械能够产生各种电穿孔波形。

[0101]

参考文献

[0102]

[1]w.meiling and f.stary,nanosecond pulse techniques.new york:gordon and breach,1970,p.304.

[0103]

[2]q.yang,x.zhou,q.-g.wang and m.zhao,

″

comparative analysis on the fast rising edge pulse source with two kinds of avalanche transistor,

″

in cross strait quad-regional radio science and wireless technology conference,chengdu,2013.

[0104]

[3]g.yong-sheng et al.,

″

high-speed,high-voltage pulse generation using avalanche transistor,

″

review of scientific instruments,vol.87,no.5,p.054708,2016.

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。