1.本发明涉及数据处理系统中的噪声降低,尤其涉及用于产生和使用互补数据流来降低噪声的系统和方法。

背景技术:

2.高效和准确的数据通信和处理对于实现高速通信至关重要。许多系统利用数据通信,包括互联网、数据中心、电信和点对点通信系统。

3.数据通常是一系列逻辑0和1值,它们形成高速数据流。当数据流通过通道时,它会受到通道的影响。现有技术中的挑战之一是准确接收和处理数据流。在对数据进行处理以便在通道上传输或进行后续处理的情况下,重要的是保持数据和处理环境没有噪声,从而不会降级正在处理的数据或处理环境。

4.当处理数据信号或数据流时,数据信号的逻辑电平之间的每次转变都从电源节点汲取电流。因此,每次转变都会降低电源节点上的电压,这将噪声或抖动引入电源节点。电源节点上的这种噪声可能损坏正在处理的数据,并且在多通道系统中,还会耦合到其它通道,从而干扰其它通道的操作。

5.一种提议的解决方案是利用多个电容器来平滑电源节点的瞬变。然而,电容器增加了附加的成本,消耗了宝贵的空间,并且没有完全解决问题。所公开的系统克服了现有技术中的缺点,并提供了附加的好处。

技术实现要素:

6.一种用于降低信号中的噪声的方法,包括接收高数据速率的主数据流,该主数据流包括具有逻辑值的比特流。然后,分割主数据流以产生第一组一个或多个较低速率数据流和第二组一个或多个较低速率数据流。然后处理第二组较低速率数据流,以反转形成第二组较低速率数据流的比特的逻辑值,从而产生一个或多个经处理的较低速率数据流。该方法组合第一组一个或多个较低速率数据流与一个或多个经处理的较低速率数据流,以产生互补数据流。用数据处理系统并发处理主数据流和互补数据流,以降低向数据处理系统提供电流的电源上的噪声。

7.组合的步骤可以包括交织。在一个实施例中,分割包括将主数据流转换成第一组中的第一较低速率数据流和第二组中的第二较低速率数据流。互补数据流在主数据流没有逻辑电平转变的每个时钟周期具有逻辑电平转变。在一个实施例中,组合的步骤由串行器执行。用数据处理系统处理主数据流和互补数据流并发发生,以从电源建立随时间的恒定的平均电流汲取。预期这种方法可以发生在交叉点开关中。

8.还公开了一种用于降低由于信号处理的电源上的噪声的方法,包括接收主数据流,使得主数据流包括具有逻辑值的比特流。然后产生互补数据流。互补数据流具有与主数据流相反的转变模式,使得在主数据流具有逻辑电平转变的时钟周期,互补数据流不转变,并且在主数据流没有逻辑电平转变的时钟周期,互补数据流具有转变。然后用数据处理系

统并发处理主数据流和互补数据流,以降低电源上的噪声,使得电源向数据处理系统提供电流。

9.多个数据处理系统可以共享电源。在一种配置中,并发处理主数据流和互补数据流包括在同一时间并且在非常接近的相邻路径上进行处理。在一个实施例中,该方法还包括在处理之后传输或缓冲主数据流,并且将互补数据流端接于开路。由于并发处理主数据流和互补数据流产生来自电源的总体恒定的平均功率汲取,所以电源上噪声的降低发生。这种操作方法可以发生在多通道交叉点开关中,并且噪声的降低发生在多通道交叉点开关的其它通道中。

10.本文还公开了一种用于重定时和恢复数据流并降低噪声引入的系统。该实施例包括时钟和数据恢复模块,被配置为接收主数据流以恢复主数据流的时钟和定时。互补数据流生成单元被配置为生成互补数据流。互补数据流在主数据流没有逻辑电平转变的每个时钟周期具有逻辑电平转变。信号处理单元被配置为并发处理主数据流和互补数据流,以产生经处理的主数据流和经处理的互补数据流。提供发送器来传输经处理的主数据流。电源被配置为向信号处理单元提供电流。由于主数据流和互补数据流在一起考虑时在每个时钟周期具有逻辑电平转变,所以电源具有稳定的平均电流汲取。

11.在一个实施例中,信号处理单元包括一个或多个反相器和一个或多个多路复用器。互补数据流生成单元可以包括被配置为处理主数据流和时钟信号以生成互补数据流的逻辑元件。信号处理单元可以是多通道交叉点开关。在一种配置中,经处理的互补数据流被端接到开路。

12.本发明的其他系统、方法、特征和优点对于本领域技术人员来说,在研究了以下附图和详细描述后将会变得显而易见。所有这些附加的系统、方法、特征和优点都包含在本说明书中,包含在本发明的范围内,并且受到所附权利要求的保护。

附图说明

13.附图中的组件不一定是按比例绘制的,而是强调说明本发明的原理。在附图中,在不同的视图中,相同的附图标记表示相应的部分。

14.图1a示出了示例性第一使用环境的框图。

15.图1b示出了示例性第二使用环境的框图。

16.图1c示出了示例性第三使用环境的框图。

17.图2a示出了示例性现有技术数据流。

18.图2b示出了与图2a的数据流相关联的电流汲取和移动平均电流的现有技术时间对齐的图。

19.图3a示出了示例性数据流。

20.图3b示出了图3a的互补数据流。

21.图3c示出了与图3a和图3b的数据流相关联的电流汲取和移动平均电流的时间对齐的对应图。

22.图4a示出了数据流映射的传统方法。

23.图4b示出了产生互补数据流的方法。

24.图5示出了具有互补数据路径的示例性多通道系统的框图。

25.图6示出了被配置为产生互补数据流的逻辑元件的框图。

26.图7示出了用于产生互补数据流的系统的另一个示例实施例的框图。

27.图8示出了示例操作方法的操作流程图。

28.图9示出了替代示例操作方法的操作流程图。

具体实施方式

29.为了克服现有技术的缺点并提供附加的好处,公开了响应于主数据流产生互补数据流,该互补数据流具有在主数据流没有逻辑电平转变的每个时钟周期建立逻辑电平转变的转变模式。对于存在转变的主数据流中的时钟周期,互补数据流没有瞬变,但是对于主数据流没有转变的时钟周期,互补数据流具有瞬变。因此,互补数据流可以被认为是转变相反的数据流。

30.图1a示出了使用本发明的示例环境。在一个示例实施例中,本文公开的方法和装置用于在第一站104和第二站108之间传送数据。数据可以通过任何路径、导体或通道112传输。导体或通道112可以包括但不限于一个或多个金属导体、光学通道或自由空间通信,诸如无线电或其他频率通信,或任何其他类型的通道。如果第一站104和第二站108之间的距离很大,则可能需要一个或多个中继器116a、116b来处理数据,使得数据可以到达期望的站并被恢复。如所理解的,中继器116可以包括接收信号并在向前重发信号之前将信号恢复或放大到期望格式的设备。还可以设想,除了所示的那些之外,还可以存在中继器116或站,或者一些系统可以被配置为没有中继器。

31.图1b示出了根据本文公开的方法和装置配置的多站通信系统的示例实施例的框图。如图所示,第一站120被配置为通过一个或多个通道154与第二站128通信。第一站120和第二站128中的每一个都可以包括接收器172a、172b和发送器166a、166b。如图所示,接收器172a、427b和发送器166a、166b中的至少一个连接到处理设备150a、150b、150c、150d。处理设备150可以包括一个或多个处理器、asic、控制逻辑、交换结构、调制器、解调器、反相器、多路复用器、缓冲器或任何其他设备。对处理设备150的输入可以以本领域已知的任何方式发生。类似地,尽管某些路径或接口被示为串行或并行,但是完全可以设想这些路径中的任何一个可以被配置为串行或并行路径或者两者。

32.图1c示出了示例使用环境的示例实施例。在该实施例中,本文公开的创新可以被配置为具有多个输入184和多个输出188的交叉点开关180的一部分。交叉点开关180是以矩阵配置布置的开关的集合。可以提供任意数量的输入184和输出188。在一个实施例中,交叉点开关具有288个不同的输入和288个不同的输出(通道),并且任何输入可以被路由到任何输出。每个通道的处理元件可以从共享电源节点(未示出)接收功率。在交叉点开关180中,多个输入和输出线形成互连元件的交叉模式,其中在这些元件之间的连接可以通过闭合开关或建立多路复用器连接或位于每个交叉点的其他连接来建立。

33.尽管在这些示例使用环境中示出,但是可以预期任何系统都可以受益于本文公开的方法和装置。任何具有时钟和数据恢复模块或功能的系统都将受益于该创新。类似地,任何接收和重定时数据的系统都可以受益于本文公开的创新。

34.图2示出了示例性主数据流。如图所示,数据在逻辑0电平212和逻辑1电平208之间转变。数据可以在每个时钟周期216在逻辑电平之间转变,或者可以在连续的时钟周期220

内保持在相同的逻辑电平。主数据流216可以被称为数据流或接收的信号。在cmos技术中,仅在转变到不同逻辑电平时,例如,从逻辑电平0切换到逻辑电平1,或者从1切换到0电平时,才从电源汲取电流。结果,来自电源或电源节点的功率消耗作为主数据流216上的数据模式的函数而改变。在具有数百个通道的系统中,当大量通道基于共享时钟信号同时转变时,电流汲取和相关的电压摆幅会进一步增加。例如,如果75个通道在同一时钟周期内全部转变或不转变,电源纹波将被放大。

35.图2b示出了与图2a的主数据流相关联的电流汲取和移动平均电流的时间对齐的对应图。电流汲取图240在转变处具有波峰244,然后衰减到零水平248,直到下一个转变。如图所示,电流波峰在时间上与转变相对应。移动平均电流250也变化,尽管没有波峰电流曲线240变化剧烈。移动平均电流250在最大汲取254和最小汲取258之间变化。当图2a的数据信号在时钟周期期间没有转变时,移动平均电流250下降,因为只有在转变发生时才汲取电流。

36.导致图2a、图2b的图的传统或现有技术方法的缺点在于,数据转变的变化引入了移动平均电流250的变化,这导致了电源电压的变化,也称为电源噪声或纹波。随着时间的推移,这种与高速数据同步的变化会产生纹波,纹波反过来降级信号和其它系统组件需要从其汲取功率的电源。因此,纹波传播到电源节点,不仅影响当前通道,还影响从电源节点汲取电压和电流的其他通道。此外,基于数据的转变会将耦合引入相邻或附近的通道,并且总体效果是当前通道和其他通道上的数据损坏和噪声。一种提议的解决方案是利用许多电容器来平滑电源输出并降低纹波,但是这种解决方案成本高,占用宝贵的空间,并且增加了易出故障的附加元件。

37.图3a示出了示例性主数据流。图3a的主数据流通常与图2a的主数据流相同,因此不再详细讨论。它是为图3b和图3c的讨论而提供的。

38.图3b示出了图3a的互补数据流。互补数据流在其中主数据流中没有转变的每个时钟周期具有一个转变。例如,在时钟周期308,主数据流204没有转变。结果,互补数据流304包括转变312。然而,在时钟周期320、324、328期间,主数据流204在逻辑电平之间转变。结果,在时钟周期320、324、328,互补信号304没有转变,并且保持在所示的相同逻辑电平340。

39.接下来,在时钟周期330,主数据流204不转变,因此互补数据流304引入到0逻辑电平的转变344。互补数据流304以这种方式进行,当主数据流中没有转变时,在每个时钟周期引入转变。任何逻辑、控制系统或其他元件都可以用于形成互补数据流304。

40.图3c示出了与图3a和图3b的组合数据流相关联的电流汲取和移动平均电流的时间对齐的对应图。在该图中,对于波峰电流信号360,当考虑主数据流204和互补数据流304时,由于每个时钟周期的转变,在每个时钟周期具有电流波峰366。结果,移动平均电流370通常是稳定和一致的,并且不包括如图2b所示的下降、波峰或波谷。这降低了电源处的电流纹波和电压降,其中电流纹波和电压降不仅会干扰所示通道(主通道),还会给多通道系统中同样依赖共享电源的其它通道带来抖动和干扰。

41.图4a示出了产生互补数据流时数据流映射的传统方法。如图4a所示,接收传入(主)数据流408。传入数据流408包括多个比特,诸如比特1 412a和比特2 420a以及所示的其他比特。这个流是随时间变化的。该比特流408由于通道或其他因素而降级,并且在该实施例中,优选的是重定时或“清理”(clean up)数据,用于后续处理或重传。根据数据传输的

性质,可以使用不同的参数来确定信号质量。所公开的数据流通常出现在处理系统中,诸如在背板或总线上,或者在交叉点矩阵中,从而使得所公开的创新与任何信令或调制格式兼容。

42.在一个示例性操作方法中,传入数据流408被分割成两个较低速率比特流440、444,用于处理和重定时。因此,在较低速率数据流中,比特1 412a变成比特1 412b,并且比特2 420a变成比特2 420b。在处理和重定时之后,两个较低速率比特流440、444被串行化为单个高速比特流430,其具有与传入数据流408相同的比特率。在其他实施例中,传入数据流408可以被分割成任意数量的较低速率比特流用于处理,并且当重新组合时,较高速率比特流可以与传入数据流408具有相同或不同的比特率。

43.图4b示出了用于产生互补数据流的示例性方法。这只是产生互补数据流的一种可能的方法,本领域普通技术人员可以采用不同的操作方法或技术来产生互补数据流,该互补数据流具有与传入(主)数据流相反的数据转变模式。与图4a相比,相同的元件标有相同的附图标记。

44.如图所示,传入数据流408如现有技术中那样被处理,以产生两个较低速率的数据流440、444。此后,作为产生互补数据流的一部分,较低速率数据流440、444之一的逻辑电平被反转,从而产生经处理的低速率数据流460、464,其中之一具有反转的逻辑电平。在该实施例中,与低速率数据流444相比,低速率数据流444使其逻辑值反转,以产生反转的逻辑电平比特流464。因此,比特2 420b变成具有反转逻辑电平的反转比特2 450a。

45.此后,经处理的低速率数据流460、464以一对一的交织方式被串行化回高速数据流,从而将低速率比特流460与反转的逻辑电平比特流464组合以产生互补数据流468。

46.总的来说,互补数据流468和传入数据流408在每个时钟周期具有转变。这就产生了平均移动电流,如图3c所示,它不包括波峰或波谷。

47.图5示出了具有互补数据路径的示例性多通道系统的框图。这仅仅是一个可能的示例实施例,并且本领域普通技术人员可以得到用于产生互补数据流和互补数据路径的其他配置,互补数据路径被配置在在其上处理主数据流的主数据路径附近。在具有互补数据路径的多通道系统504中,有多个通道,包括通道0 508a、通道1 508b、直到通道n 508n,其中n是任何正整数值。由于空间限制,每个通道可能与其他通道非常接近。在其他实施例中,可以只有一个通道。

48.详细讨论了通道0 508a,并且系统504的其他通道可以是大致相同的或者可以具有不同的配置。通道0 508a包括被配置为接收主数据流的输入512,该主数据流可以从通道、总线、背板、另一处理元件或任何其他设备、路径或位置接收。主数据流馈入cdr(时钟数据恢复)模块516,该模块处理信号以提取时钟信号,并使用提取的时钟信号以最佳定时对传入数据流进行采样。cdr模块516提供两个输出。一个cdr输出是在输出520上提供的重定时和干净的主数据流,而提取的时钟信号在输出522上提供。主数据流馈入处理元件532的网络,在交叉矩阵开关的该示例实施例中,该网络可以包括反相器528、544、一个或多个多路复用器、控制逻辑和其他相关联的元件(统称为开关矩阵)。在其他实施例中,其他硬件、软件或两者可以形成处理元件532。

49.如图所示,一个或多个反相器528、544连接到电源节点530。其他通道508b、508n也从同一电源节点530获取功率。因此,电源节点530上的噪声影响与其连接的所有处理元件,

诸如其他通道508b、508n。一个或多个反相器528、544和其他相关联的处理元件(诸如多路复用器或交叉点开关的其他元件)被定义为处理系统532。处理系统消耗图5所示系统中的大部分功率,因此,具有互补的数据路径(包括元件540、548)将提供最大程度的噪声降低。不在互补数据路径中镜像的输出缓冲器552不是高功率消耗元件。

50.主数据流还馈入互补数据生成单元524。互补数据生成单元524还从cdr模块516接收输出522上的时钟信号。互补数据生成单元524是被配置为处理数据流并生成互补数据流的硬件、软件或两者的任意组合。互补数据生成单元524可以包括逻辑元件、状态机、一个或多个反相器、寄存器、执行以非暂时性格式存储在存储器中的机器可执行指令的处理器、或者这些元件的任何组合或者任何其他元件。

51.互补数据生成单元524的输出534是互补数据流,其馈入互补数据路径,该路径包括反相器的网络,该反相器的网络包括反相器540、548和多路复用器(未示出)。主数据路径和互补数据路径应尽可能相同或相似,以提供最有效的噪声消除。逆变器540、548的这个网络也从电源节点530汲取功率。

52.反相器544的输出是处理的主数据流,该处理的主数据流馈入输出缓冲器552。输出缓冲器552在输出556上呈现干净的和重定时的数据之前缓冲数据流。反相器548的输出是互补数据流,它呈现在输出560上。然而,不使用互补数据流,而是如图所示端接到开路。在其他实施例中,可以考虑其他终端选项。诸如示例性元件524、540、548的互补数据流路径的使用在电源节点530上提供了更稳定和均匀的负载,这降低了主数据流和相关联的路径中的噪声,以及降低了将耦合到相邻通道的噪声,并降低了其他通道508b、508n上的电源噪声。

53.图6示出了被配置为产生互补数据流的逻辑元件系统的框图。这只是被配置为产生互补数据流的逻辑元件的一种可能配置。不脱离所附权利要求范围的其他实施例也是可能的。在互补数据流产生模块604(以下称为模块)的这个示例实施例中,在数据输入608上接收主数据流,并且在时钟输入612上接收时钟信号。这些可以由cdr模块提供。

54.主数据流馈入xor逻辑元件和第一触发器616。第一触发器616也接收时钟信号。触发器响应触发器时钟输入上的时钟信号,选择性地时钟输入和时钟输出主数据流。第一触发器616的输出向xor逻辑元件620提供数据输入。xor逻辑元件620的操作在本领域中是公知的,因此在此不再详细描述。

55.下表定义了xor函数。

[0056][0057]

来自xor逻辑元件620的输出连接到多路复用器628,作为多路复用器的控制信号。多路复用器628接收来自第二触发器624的反馈的两个输入,其中一个如下所述被反转。多

路复用器628的输出具有作为第二多路复用器624的输入的输出。如图所示,第二触发器624也接收时钟信号。

[0058]

第二触发器624结合来自时钟信号的定时控制来处理多路复用器输出,以在输出632上产生互补数据流。第二触发器输出632作为输入被反馈到多路复用器628,并且两个触发器输入中的一个被反转。xor输出控制多路复用器628的哪个输入被呈现为多路复用器的输出。

[0059]

在操作中,主数据流和时钟信号被提供给起延迟作用的第一触发器616。主数据流也被呈现给xor逻辑元件620。由于第一触发器616的延迟功能,xor逻辑元件620正在比较主数据流中的两个连续比特。如果存在转变,则xor逻辑元件620输出逻辑1值,这意味着传入数据的逻辑电平从1变为0或者从0变为1。相反,如果没有转变,则xor逻辑元件620输出逻辑0值。换句话说,xor逻辑元件620指示主数据流中的连续比特之间是否发生了转变。

[0060]

xor逻辑元件620是多路复用器628的控制信号。当xor逻辑元件620的输出指示转变(1逻辑电平)时,则多路复用器628的下部输入从多路复用器输出。当xor逻辑元件620的输出指示没有转变(0逻辑电平)时,多路复用器628的上部输入从多路复用器输出。多路复用器628的两个输入是相同的信号,但是上部输入是反转的。第二触发器624用作存储器或寄存器来保存关于当前状态的信息,该信息然后被反馈到多路复用器628中。

[0061]

对于特定的时钟周期,如果主数据流有转变,则输出632(互补数据流)的当前逻辑状态被保持(没有转变)。发生这种情况是因为主数据流中的比特之间没有转变导致xor逻辑元件620输出逻辑1值,这又迫使多路复用器输出与由第二触发器624馈入多路复用器输入1的逻辑状态相同的逻辑状态。由于输入608上的数据具有转变,输出632上的逻辑电平不变,即没有转变。相反,如果数据输入信号(在输入608上)没有转变,则输出632的当前逻辑状态被改变(引入转变),导致xor逻辑元件620输出逻辑0值,这又迫使多路复用器输出由第二触发器624馈送到反相多路复用器输入0的反转的逻辑状态。由于输入608上的数据没有转变,输出632上的输出逻辑电平改变,即在互补数据流中引入了转变。

[0062]

图7示出了用于产生互补数据流的系统的示例实施例的框图。这只是被配置为产生互补数据流的逻辑元件的一种可能配置。不脱离所附权利要求范围的其他实施例也是可能的。图7所示的系统704包括输入708,其被配置为从通道或其他源接收失真数据。在该实施例中,接收比特1、2、3、4、5、6、7的数据流,很像图4的比特流408。传入数据流被呈现给半速率cdr模块712,该模块将传入数据流分割成两个较低速率数据流。半速率cdr模块是本领域普通技术人员已知的,因此在此详细描述。如图所示,输出720携带比特1、3、5、7,而输出722携带比特2、4、6、8。

[0063]

时钟线716从半速率cdr模块712延伸,并连接到一对2到1串行器732、736。输出720、722上的两个低速比特流也被提供给2-1串行器732、736中的每一个。然而,输出722上的比特2、4、6、8在被馈送到2-1串行器736之前被提供给反相器728。因此,提供给2-1串行器736的比特2、4、6、8是从半速率cdr模块712输出的比特电平的反逻辑电平。

[0064]

2-1串行器732、736是本领域普通技术人员已知和理解的,因此在此不再详细描述。2-1串行器732、736将每个输入组合成单个高速数据流。任何数据速率变化都是可能的,但是在该实施例中,半速率cdr模块712输出的数据速率是输入信号速率的一半,而2-1串行器732、736在形成输出信号时使输入信号的比特率加倍。

[0065]

串行器732的输出740携带主数据流,该主数据流已经被重定时,并且已经移除了任何抖动或通道的其他不想要的影响,或者已经被切换到期望的输出。串行器736的输出744携带互补数据流,该互补数据流已经被重定时并且移除了通道的任何抖动或其他影响,并且其中每隔一位处于主数据流的相反逻辑电平。因此,在该示例实施例中,与主数据流相比,位2、4、6等处于相反的逻辑电平。

[0066]

互补数据流与主数据流在每个时钟周期具有转变,从而建立了来自电源节点的一致的移动平均功率汲取。

[0067]

图8示出了示例操作方法的操作流程图。这只是本文公开的创新的一种可能的操作方法。在不脱离所附权利要求的情况下,其他方法也是可能的和可预期的。该方法开始于接收主数据流的步骤808。可以从通道、模拟前端、另一数据处理元件或任何其他位置或设备接收主数据流。接下来,在步骤812,该操作方法处理主数据流以产生互补数据流,该互补数据流具有与主数据流相反的转变模式,使得在主数据流具有逻辑电平转变(从一个逻辑电平到另一个逻辑电平)的每个时钟周期期间,互补数据流没有逻辑电平转变。以及,在主数据流没有逻辑电平转变(从一个逻辑电平到另一个逻辑电平)的每个时钟周期期间,互补数据流具有逻辑电平转变。

[0068]

在步骤816,在主数据流的处理期间,互补数据流在主数据流附近并与主数据流并发地被被处理和被路由。通过同时产生和处理主数据流和转变相反的互补数据流,由于在每个时钟周期发生逻辑电平转变,平均移动电流通常保持一致。这降低了多声道系统中主声道和其他声道中的噪声。在步骤820,该方法传输处理的(重定时的)主数据流,同时互补数据流在开路或其他终端处端接。

[0069]

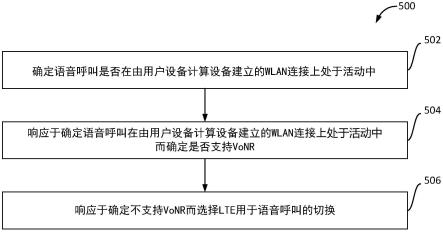

图9是示例操作替代方法的操作流程图。这只是本文公开的创新的一种可能的操作方法。在不脱离所附权利要求的情况下,其他方法也是可能的和可预期的。该方法开始于步骤904,其中系统接收主数据流。然后,在步骤908,系统处理主数据流以产生两个或更多个较低速率的数据流。这可以使用半速率cdr模块、逻辑元件或被配置为将数据流分割成两个或更多个较低速率数据流的任何其他设备来实现。

[0070]

在步骤912,系统处理两个或更多个较低速率数据流中的一个或多个,以反转每个比特的逻辑电平,从而产生一个或多个具有反转的逻辑电平的低速率数据流。这在图4b中的低速率反转比特流464中示出。

[0071]

在步骤916,2-1串行器或其他设备利用来自两个低速率数据流(非反转和反转的低速率数据流)的交织比特来串行化,以产生互补数据流。如本文所讨论的,应该理解,可以使用其他方法和系统来产生互补数据流。

[0072]

在步骤920,系统被配置为在时间上并发路由和处理主数据流和在主数据流附近的互补数据流。这在每个时钟周期在电源节点上建立了一致的电流汲取,进而降低了通过电源节点引入电源节点和其他通道的噪声。因此,不仅所讨论的通道(主通道)的性能得到改善,多通道系统中的其他通道也实现了好处。

[0073]

在步骤924,处理主数据流。互补数据流不被传输,而是可以被端接到开路或其他终端配置。

[0074]

虽然这种操作方法包括以原始速率重建数据流的步骤,但是也可以设想复制主数据流,然后在复制的数据流中,每隔一位的逻辑电平可以被反转。这种替代方法避免了产生

两个或更多个低速率数据流的步骤。

[0075]

虽然已经描述了本发明的各种实施例,但是对于本领域普通技术人员来说,很明显,在本发明的范围内,更多的实施例和实现是可能的。此外,本文描述的各种特征、元素和实施例可以以任何组合或布置来要求保护或组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。