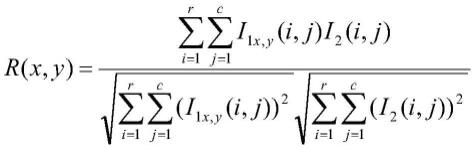

一种基于嵌入式gpu平台的单目标跟踪方法

技术领域

1.本发明涉及一种基于嵌入式gpu平台的单目标跟踪方法,属于计算机视觉领域。

背景技术:

2.视觉目标跟踪(visual objecttracking)是计算机视觉领域的一个重要课题,有着重要的研究意义,在军事制导、无人驾驶、视频监控等方面有着广泛的应用前景。视觉目标跟踪是指对图像序列中的目标进行检测、提取、识别和跟踪,从而获得目标参数,如目标位置、大小、速度等。根据跟踪目标的数量可以分为单目标跟踪和多目标跟踪,较单目标跟踪而言,多目标跟踪要更加复杂,需考虑多个目标间的关联匹配问题。

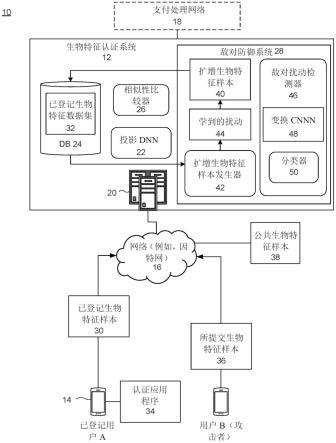

3.单目标跟踪方法的核心算法采用归一化积相关(normalizated product correlation),是一种基于图像灰度的匹配算法,采用空间二维滑动模板实现,基本原理如下:

[0004][0005]

当目标i

1x,y

(二维滑窗)在实时图i2中进行遍历匹配时,在实时图中的每个像素点都会计算出目标滑窗和实时图的灰度相关值,定义为r值,当目标与实时图越相似时,r值越接近于1,当r值为1时,目标与实时图完全匹配,r值最大的坐标点即为目标跟踪点。

[0006]

单目标跟踪方法主要包含两部分:1)算法核心部分:目标模板小图(二维滑窗)在整个实时图上针对每个像素位置进行图像灰度相关性计算(即所述归一化积相关计算),由于图像是二维矩阵,所以目标小图与实时大图的相关性计算是矩阵运算,即并行化计算,整个跟踪算法的处理时间大部分消耗在该部分;2)算法外围策略部分:对1)中的相关性计算结果(也是二维矩阵)进行搜索、排序、筛选、聚类等一系列处理,从中筛选出可信度最高的坐标点,即目标跟踪点,该部分的策略处理是决定整个跟踪算法准确度的关键。

[0007]

目前,整个跟踪算法是在一个“fpga dsp”的异构平台上实现。算法核心部分放在fpga上运行,fpga(field programmable gate array):现场可编程门阵列,是一种并行架构芯片,适合处理算法核心部分的相关性运算(矩阵并行计算);算法外围策略部分放在dsp上处理,dsp(digital signal process):数字信号处理芯片,并行化程度不高,但运算速度快,适合处理算法策略部分的大量矩阵遍历、搜索、排序等操作。虽然该架构上实现的跟踪算法性能已经可以达到实际应用需求,但是仍具有以下不足:1)整个跟踪算法被拆分开,不便于整套跟踪算法的优化、调试以及移植等工作;2)两个芯片fpga与dsp之间要进行频繁的数据交互,数据交互的耗时大大降低了跟踪算法的实时性;3)该异构平台体积大、功耗高,不适合空间、功耗特别紧俏的嵌入式场景。

技术实现要素:

[0008]

本发明需解决的技术问题是提供一种实时性高、便于算法改进、优化的单目标跟踪方法。

[0009]

为解决上述技术问题,本发明提供了一种基于嵌入式gpu平台的单目标跟踪方法,采取技术方案如下:

[0010]

基于获取的图像序列,选用嵌入式gpu平台进行目标相关性计算,利用目标模板小图在整个实时图上针对每个像素位置进行图像灰度相关性计算;对相关性计算结果进行极值搜索、排序、筛选、聚类,从中筛选出可信度最高的坐标点,获得目标跟踪点。

[0011]

进一步地,所述目标模板小图在所述实时图上的移动步进为2像素。

[0012]

进一步地,对所述实时图叠加补边,将位于边界区域内的目标包含进所述实时图中。

[0013]

进一步地,所述极值搜索区域为八邻域。

[0014]

进一步地,计算相关值主次极值比,设置阈值,进行目标点的滤波筛选。

[0015]

本发明提出的基于嵌入式gpu平台(jetson tx1)的跟踪算法改进、优化和加速方法,在目标跟踪精度有所提升的情况下,大幅降低了跟踪算法耗时,并且在一片体积更小、功耗更低的集成芯片上完成跟踪处理,对该跟踪算法在嵌入式场景的应用提供了更加广阔的应用前景。与现有技术对比,本明具有如下效果:

[0016]

1)对核心算法归一化积相关计算部分进行改进,将目标模板小图的移动步长由逐像素改为步进2像素,去除计算冗余,提高计算效率;2)对算法外围策略的相关性计算结果搜索部分进行优化,进一步增加了目标点的可信度,提高跟踪点准确性;3)将高运算量的归一化积相关运算由fpga芯片移植到gpu芯片实现,大大提高了跟踪算法的实时性。经过在新平台上所做的上述算法改进、优化和加速,与“fpga dsp”异构平台相比,在跟踪准确度有所提高的情况下,降低了跟踪算法延时,对该算法在嵌入式场景的应用非常具有参考价值。

附图说明

[0017]

图1为实时图未修改步进、不叠加补边的示意图;

[0018]

图2为本发明实施例提供的实时图修改步进、叠加补边的示意图;

[0019]

图3为相关值曲面图;

[0020]

图4为本发明实施例提供的八邻域示意图。

具体实施方式

[0021]

下面结合附图和实施例对本发明作进一步说明。

[0022]

作为本发明的实施例,提供的一种基于嵌入式gpu平台的单目标跟踪方法,具体如下:

[0023]

基于获取的图像序列,选用嵌入式gpu平台(jetson tx1,图形处理单元)进行目标相关性计算。利用目标模板小图(二维滑窗)在整个实时图上针对每个像素位置进行图像灰度相关性计算(即归一化积相关计算,由于图像是二维矩阵,所以目标小图与实时大图的相关性计算是矩阵运算,即并行化计算);对相关性计算结果(二维矩阵)进行极值搜索、排序、筛选、聚类,从中筛选出可信度最高的坐标点,获得目标跟踪点。

[0024]

本发明实施例将之前在fpga上实现的归一化积相关计算部分(高并行、高计算量)改由在jetson tx1平台的gpu(专属图形并行化计算平台)上实现,并且将之前分开的核心算法和外围策略两部分整合成一套跟踪算法,进一步精简了算法架构,消除之前在“fpga dsp”双平台下由于频繁的数据交互带来的算法延时。

[0025]

进一步地,在本发明实施例中,对归一化积相关核心算法部分进行遍历方法的修改。由于单个像素内目标特征变化很小,将归一化积相关计算部分目标模板小图的移动步长由逐像素(即步进1像素)改为步进2像素,在降低计算量的同时几乎不会降低目标相关性计算结果准确性,几近降低了一半的计算量。

[0026]

进一步地,在本发明实施例中,对实时图叠加补边,如采用镜像补边法,将位于边界区域内的目标包含进实时图中,克服之前实时图边界区域归一化积相关计算不到的局限,进一步提升实时图边界目标跟踪准确率。具体说明如图1、图2所示。

[0027]

进一步地,在本发明实施例中,对归一化积相关计算结果处理部分的极值搜索操作进行改进,将极值搜索区域由之前四邻域该为八邻域。具体说明如下图3、图4所示。

[0028]

在图3所示的相关值曲面图上进行最大值搜索时,每个点都与周围邻域点进行比较,比较的范围由之前四邻域(对应图4中的1、3、5、7)改为八邻域(图4中1~8),n为取八邻域点时的半径,改为八邻域后可进一步提升极大值点筛选的准确性。

[0029]

进一步地,在本发明实施例中,计算相关值主次极值比,设置阈值,进行目标点的滤波筛选(主次极值比:相关值最大值与次大值的比值),进一步提升筛选出的目标点的可信度和唯一性。

[0030]

相关值主次极值比msr定义如下:

[0031][0032]

其中,c

max

为相关值最大值,c

submax

为相关值最小值。

[0033]

由于采用单目标跟踪,在实时图内要跟踪目标是唯一的,增加主次极值比msr参数的意义在于,当实时图内出现多个疑似目标时,即图3中将出现多个高波峰,而正常情况下应该只有一个高波峰且远大于其他波峰,当该参数很大时说明实时图内包含唯一目标,所以可通过对该参数设置阈值滤波的方法来保证跟踪目标的唯一性,同时也提高了跟踪目标的可信程度。

[0034]

性能测试与验证:

[0035]

针对本发明实施例对基于归一化积相关的目标跟踪算法进行改进、优化、加速,并移植到嵌入式gpu平台(jetsontx1)上实现,对改进后的性能进行了测试与比对。分别测试了不同尺度下的目标模板图和实时图跟踪性能,并与传统“fpga dsp”架构下跟踪性能进行对比,结果如下表1、2所示:

[0036]

表1算法跟踪准确率对比

[0037][0038]

表2算法运算时间对比

[0039][0040]

由表1、2统计结果可以看出,算法经改进后,在目标模板和实时图同等大小的情况下,跟踪准确率提升了0.5%左右,同时跟踪处理时间jetson tx1平台基本上为“fpga dsp”平台的一半,由此可见,本发明对跟踪算法进行的改进、优化、加速方法,较传统“fpga dsp”平台上实现的跟踪算法准确率和处理时间均有提升。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。