1.本技术涉及计算机软件技术领域,具体而言,本技术涉及一种数据处理方法、装置、集成芯片、电子设备及计算机可读存储介质。

背景技术:

2.随着人工智能的兴起,深度学习已成为当前ai(artificial intelligence,人工智能)研究的重点,广泛应用于自动驾驶领域、环境感知、传感器融合等领域。

3.在通过数据处理模型,即神经网络模型进行海量数据的并行运算的同时,做到高效、可靠的推理,那就意味着承载ai算法的计算平台需要具备足够的加速处理性能。现有技术中,通常采用npu(neural-network processing unit,神经网络处理器)来进行数据处理模型的计算与推理,提升了模型的运行效率。但是在输入数据比较复杂的情况下,特别是图像数据的处理过程中,往往会出现npu的硬件功能无法达到相应的数据处理要求的情况,造成模型的推理任务无法高效完成。

技术实现要素:

4.本技术实施例提供了一种数据处理方法、装置、集成芯片、电子设备及计算机可读存储介质,可以解决现有技术中数据处理模型无法高效完成推理任务的问题。所述技术方案如下:

5.根据本技术实施例的一个方面,提供了一种数据处理方法,该方法包括:

6.获取待处理数据,从第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据;

7.从第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据;

8.从第三处理器调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

9.可选的,上述对预处理数据进行矢量运算,生成合并数据,包括:

10.基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据;

11.针对分块数据进行矢量运算,生成合并数据。

12.可选的,上述隐含层对应存在至少两条处理链路;

13.针对分块数据进行矢量运算,生成合并数据,包括:

14.基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据;

15.将至少两个中间数据进行合并处理,得到合并数据。

16.可选的,每一处理链路包括至少两个计算单元;

17.基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据之前,还包括:

18.基于内存层级为每一计算单元匹配目标存储空间;目标存储空间用于存放计算单

元的输出数据。

19.可选的,上述目标存储空间包括第一层级存储器;

20.针对分块数据进行矢量运算,生成合并数据之前,还包括:

21.将预处理数据和分块数据均存储于第一层级存储器。

22.可选的,上述目标存储空间还包括第二层级存储器和第三层级存储器;第一层级存储器、第二层级存储器和第三层级存储器的层级依次递增;

23.基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据,包括:

24.将分块数据从第一层级存储器传输到第二层级存储器,并传输到第三级存储器;

25.从第三层级存储器中读取分块数据,并基于至少两个计算单元进行计算,得到中间数据;

26.其中,每一计算单元的输出数据和中间数据均存储于第二层级存储器。

27.根据本技术实施例的另一个方面,提供了一种数据处理装置,该装置包括:

28.获取模块,用于获取待处理数据,从第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据;

29.计算模块,用于从第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据;

30.分类模块,用于从第三处理器调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

31.可选的,上述计算模块,用于:

32.基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据;

33.针对分块数据进行矢量运算,生成合并数据。

34.可选的,上述隐含层对应存在至少两条处理链路;

35.上述计算模块,还用于:

36.基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据;

37.将至少两个中间数据进行合并处理,得到合并数据。

38.可选的,上述每一处理链路包括至少两个计算单元;

39.上述计算模块,还用于:

40.基于内存层级为每一计算单元匹配目标存储空间;目标存储空间用于存放计算单元的输出数据。

41.可选的,上述目标存储空间包括第一层级存储器;

42.上述计算模块,还用于:

43.将预处理数据和分块数据均存储于第一层级存储器。

44.可选的,上述目标存储空间还包括第二层级存储器和第三层级存储器;第一层级存储器、第二层级存储器和第三层级存储器的层级依次递增;

45.上述计算模块,还用于:

46.将分块数据从第一层级存储器传输到第二层级存储器,并传输到第三级存储器;

47.从第三层级存储器中读取分块数据,并基于至少两个计算单元进行计算,得到中间数据;

48.其中,每一计算单元的输出数据和中间数据均存储于第二层级存储器。

49.根据本技术实施例的另一个方面,提供了一种集成芯片,包括第一处理器、第二处理器和第三处理器;其中,

50.第一处理器,其配置为获取待处理数据,调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据;

51.第二处理器,其配置为调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据;

52.第三处理器,其配置为调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

53.可选的,上述第二处理器,其配置为基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据;针对分块数据进行矢量运算,生成合并数据。

54.可选的,上述隐含层对应存在至少两条处理链路;

55.上述第二处理器,其配置为基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据;将至少两个中间数据进行合并处理,得到合并数据。

56.可选的,每一处理链路包括至少两个计算单元;

57.上述第二处理器,其配置为基于内存层级为每一计算单元匹配目标存储空间;目标存储空间用于存放计算单元的输出数据。

58.可选的,上述目标存储空间包括第一层级存储器;

59.上述第二处理器,其配置为将预处理数据和分块数据均存储于第一层级存储器。

60.可选的,上述目标存储空间还包括第二层级存储器和第三层级存储器;第一层级存储器、第二层级存储器和第三层级存储器的层级依次递增;

61.上述第二处理器,其配置为将分块数据从第一层级存储器传输到第二层级存储器,并传输到第三级存储器;从第三层级存储器中读取分块数据,并基于至少两个计算单元进行计算,得到中间数据;其中,每一计算单元的输出数据和中间数据均存储于第二层级存储器。

62.根据本技术实施例的另一个方面,提供了一种电子设备,该电子设备包括:存储器、处理器及存储在存储器上的计算机程序,上述处理器执行计算机程序以实现本技术实施例第一方面所示方法的步骤。

63.根据本技术实施例的再一个方面,提供了一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现本技术实施例第一方面所示方法的步骤。

64.根据本技术实施例的一个方面,提供了一种计算机程序产品,其包括计算机程序,该计算机程序被处理器执行时实现本技术实施例第一方面所示方法的步骤。

65.本技术实施例提供的技术方案带来的有益效果是:

66.本技术实施例通过第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据,接着采用第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,再通过第三处理器调用数据处理模型的输出层,对在隐含层生成的合并数据进行分类处理,进而得到数据处理模型对应的数据处理结果;本技术中数据处理模型的各数据处理层级分别与第一处理器、第二处理器和第三处理器进行了优化匹配,实现了基于多处理器的高性能的模型推理。相比现有技术中基于单独的npu来运行数据处理模型,本

申请实施例充分利用了第一处理器、第二处理器和第三处理的硬件优势,提升了数据处理模型的运行效率;同时,本技术实施例预先将各处理器与各数据处理层级进行匹配,减少了各数据处理层级运行时硬件相关的逻辑判断,本技术适用于比较复杂的待处理数据,例如复杂的图像数据,使得数据处理模型的计算与推理任务能够高效完成,提高数据处理结果的准确性。

附图说明

67.为了更清楚地说明本技术实施例中的技术方案,下面将对本技术实施例描述中所需要使用的附图作简单地介绍。

68.图1为本技术实施例提供的一种实现数据处理方法的系统架构示意图;

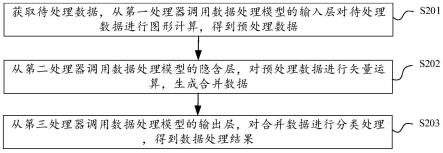

69.图2为本技术实施例提供的一种数据处理方法的流程示意图;

70.图3为本技术实施例提供的一种数据处理方法中一个示例的数据处理链路的结构示意图;

71.图4为本技术实施例提供的一种数据处理方法中一个示例的第二处理器的内存层级的结构示意图;

72.图5为本技术实施例提供的一个示例的数据处理方法的流程示意图;

73.图6为本技术实施例提供的一种数据处理装置的结构示意图;

74.图7为本技术实施例提供的一种数据处理电子设备的结构示意图。

具体实施方式

75.下面结合本技术中的附图描述本技术的实施例。应理解,下面结合附图所阐述的实施方式,是用于解释本技术实施例的技术方案的示例性描述,对本技术实施例的技术方案不构成限制。

76.本技术领域技术人员可以理解,除非特意声明,这里使用的单数形式“一”、“一个”、“所述”和“该”也可包括复数形式。应该进一步理解的是,本技术实施例所使用的术语“包括”以及“包含”是指相应特征可以实现为所呈现的特征、信息、数据、步骤、操作、元件和/或组件,但不排除实现为本技术领域所支持其他特征、信息、数据、步骤、操作、元件、组件和/或它们的组合等。应该理解,当我们称一个元件被“连接”或“耦接”到另一元件时,该一个元件可以直接连接或耦接到另一元件,也可以指该一个元件和另一元件通过中间元件建立连接关系。此外,这里使用的“连接”或“耦接”可以包括无线连接或无线耦接。这里使用的术语“和/或”指示该术语所限定的项目中的至少一个,例如“a和/或b”可以实现为“a”,或者实现为“b”,或者实现为“a和b”。

77.为使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术实施方式作进一步地详细描述。

78.人工神经网络(artificial neural networks,简写为anns)也简称为神经网络(nns)或称作连接模型(connection model),它是一种模仿动物神经网络行为特征,进行分布式并行信息处理的算法数学模型。这种网络依靠系统的复杂程度,通过调整内部大量节点之间相互连接的关系,从而达到处理信息的目的。

79.人工神经网络按其模型结构大体可以分为前馈型网络(也称为多层感知机网络)

和反馈型网络两大类,前者在数学上可以看作是一类大规模的非线性映射系统,后者则是一类大规模的非线性动力学系统。按照学习方式,人工神经网络又可分为有监督学习、非监督和半监督学习三类;按工作方式则可分为确定性和随机性两类;按时间特性还可分为连续型或离散型两类,等等。

80.不论何种类型的人工神经网络,它们共同的特点是,大规模并行处理,分布式存储,弹性拓扑,高度冗余和非线性运算。因而具有很髙的运算速度,很强的联想能力,很强的适应性,很强的容错能力和自组织能力。这些特点和能力构成了人工神经网络模拟智能活动的技术基础,并在广阔的领域获得了重要的应用。例如,在通信领域,人工神经网络可以用于数据压缩、图像处理、矢量编码、差错控制(纠错和检错编码)、自适应信号处理、自适应均衡、信号检测、模式识别、atm流量控制、路由选择、通信网优化和智能网管理等等。

81.以卷积神经网络(convolutional neural networks,cnn)为例,其是一类包含卷积计算且具有深度结构的前馈神经网络(feedforward neural networks),是深度学习(deep learning)的代表算法之一。卷积神经网络具有表征学习(representation learning)能力,能够按其阶层结构对输入信息进行平移不变分类(shift-invariant classification),因此也被称为“平移不变人工神经网络(shift-invariant artificial neural networks,siann)”。

82.卷积神经网络的结构通常包括输入层、隐含层和输出层。其中,隐含层只要包括包含卷积层、池化层和全连接层3类常见构筑,在一些更为现代的算法中可能有inception(谷歌公司提出的一种深度学习结构)模块、残差块(residual block)等复杂构筑。现有技术中,通常基于npu硬件来运行卷积神经网络。npu采用“数据驱动并行计算”的架构,特别擅长处理视频、图像类的海量多媒体数据,能够更快地执行机器学习模型,相比常规处理器将数据卸载到服务器然后等待它的响应,npu能够运行多个并行线程,且数据和处理中心之间的障碍更小,所以速度会更快。但是在输入数据比较复杂的情况下,npu无法单独的、高性能的完成模型的推理任务。

83.发明人发现,cpu(central processing unit,中央处理器)的架构中需要大量的空间去放置存储单元(cache)和控制单元(control),相比之下计算单元只占据了很小的一部分,所以它在大规模并行计算能力上极受限制,而更擅长于逻辑控制,其不适用于大规模的运算。而gpu(graphics processing unit,图形处理器)的构成相对简单,有数量众多的计算单元和超长的流水线,特别适合处理大量的类型统一的数据,但gpu无法支持神经网络中的所有层级。当dsp(digital signal process,数字信号处理)处理器架构用于处理神经网络,可以在其运算器方面作出相应修改,例如低位宽和超越函数,其能够适用于卷积神经网路,而对循环神经网络(rnn)和长短期记忆网络(lstm)等处理语音和自然语言的网络可能就无能为力了。

84.本技术提供的数据处理方法、装置、集成芯片、电子设备及计算机可读存储介质,旨在解决现有技术的如上技术问题。

85.如图1所示,本技术实施例提供了一种数据处理方法,该方法可以应用于集成芯片中,该集成芯片可以包括第一处理器、第二处理器和第三处理器。本技术实施例涉及的集成芯片,通过第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据,接着采用第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,再

通过第三处理器调用数据处理模型的输出层,对在隐含层生成的合并数据进行分类处理,进而得到数据处理模型对应的数据处理结果。本技术实施例中数据处理模型的各数据处理层级分别与集成芯片中的各处理器进行了优化匹配,实现了基于多处理器的高性能的模型推理。

86.下面通过对几个示例性实施方式的描述,对本技术实施例的技术方案以及本技术的技术方案产生的技术效果进行说明。需要指出的是,下述实施方式之间可以相互参考、借鉴或结合,对于不同实施方式中相同的术语、相似的特征以及相似的实施步骤等,不再重复描述。

87.本技术实施例中提供了一种数据处理方法,如图2所示,该方法包括:

88.s201,获取待处理数据,从第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据。

89.其中,数据处理模型可以是卷积神经网络、循环神经网络等神经网络模型,数据处理模型的计算单元包括输入层、隐含层和输出层。待处理数据可以是预设训练集中的训练数据,也可以是原始的待预测数据。

90.具体的,用于进行数据处理的集成芯片,可以基于第一处理器实时采集或从预设地址提取待处理数据,并调用数据处理模型的输入层对待处理数据进行图形计算,生成预处理数据。其中,图形计算可以包括数据标准化、去均值、pca(principal component analysis,主成分分析方法,一种数据降维算法)降维及白化、数据增强等数据预处理操作。

91.在本技术实施例中,第一处理器可以包括gpu,gpu调用数据处理模型的输入层对待处理数据依次进行标准化、去均值、pca降维及白化、数据增强处理,进而生成预处理数据。其中,

92.数据标准化可以是基于待处理数据的均值和标准差将待处理数据的各个维度的幅度标准化到同样范围;

93.去均值处理可以是基于均值将待处理数据的各个维度中心化到0;

94.pca降维及白化处理可以是基于pca方法对待处理数据进行降维,以去掉特征与特征之间的相关性,接着将降维后数据的每个特征轴上的幅度进行归一化处理;

95.数据增强是指当训练数据有限的情况下,通过一些数据变换来从已有的训练集中生成一些新的数据,来扩大训练集;该数据增强方法可以包括水平翻转、随机剪裁、平移变换、模糊处理等。

96.s202,从第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据。

97.其中,上述第二处理器可以包括npu;以数据处理模型为卷积神经网络模型为例,隐含层可以包括卷积层、激活层、池化层等计算单元;矢量运算可以包括向量或矩阵的乘法,当数据处理模型为卷积神经网络,矢量运算可以为卷积运算。

98.具体的,用于进行数据处理的集成芯片,可以基于第二处理器调用数据处理模型的隐含层,进而根据隐含层所包括的计算单元依次对预处理数据进行矢量运算,生成合并数据。

99.在本技术实施例中,以数据处理模型为卷积神经网络,以隐含层的数据处理链路包括卷积层、激活层和池化层为例进行具体说明。集成芯片可以基于npu调用卷积神经网络

的隐含层,其隐含层的数据处理过程包括:

100.(1)采用卷积层对预处理数据进行特征提取,得到第一特征向量;其中,卷积层参数包括卷积核大小、步长和填充,三者共同决定了卷积层输出特征向量的尺寸,卷积核大小可以指定为小于输入图像尺寸的任意值,卷积核越大,可提取的特征越复杂;

101.(2)根据激活层采用激励函数如relu(rectified linear unit,线性整流函数)为第一特征向量增加非线性因素,以得到特征表征更优的第二特征向量;

102.(3)采用池化层对第二特征向量进行特征选择和信息过滤,以得到目标特征向量。其中,池化层包含预设定的池化函数,其功能是将特征向量中单个点的结果替换为其相邻区域的特征向量统计量。

103.在一些实施方式中,该第二处理器还可以包括dsp处理器,dsp可以用于对数据进行nms(non-maximum suppression,非极大值抑制)、argmax计算(一种函数,用于获取目标函数取最大值时的变量值)或者argmin计算(一种函数,用于获取目标函数取最小值时的变量值)等处理。

104.s203,从第三处理器调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

105.其中,第三处理器包括cpu。在一些实施方式中,第三处理器还包括dsp。

106.具体的,用于进行数据处理的集成芯片可以基于第三处理器调用数据处理模型的输出层,输出层根据逻辑函数或归一化指数函数(softmax function)输出数据处理结果。

107.在本技术实施例中,当数据处理模型用于物体识别,数据处理结果可以为物体的中心坐标、大小或分类标签;当数据处理模型用于图像语义分割,数据处理结果可以是每一像素点的分类结果;当数据处理模型用于语音识别,数据处理结果可以是每一个单词的分类标签。

108.本技术实施例通过第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据,接着采用第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,再通过第三处理器调用数据处理模型的输出层,对在隐含层生成的合并数据进行分类处理,进而得到数据处理模型对应的数据处理结果;本技术中数据处理模型的各数据处理层级分别与第一处理器、第二处理器和第三处理器进行了优化匹配,实现了基于多处理器的高性能的模型推理。相比现有技术中基于单独的npu来运行数据处理模型,本技术实施例充分利用了第一处理器、第二处理器和第三处理的硬件优势,提升了数据处理模型的运行效率;同时,本技术实施例预先将各处理器与各数据处理层级进行匹配,减少了各数据处理层级运行时硬件相关的逻辑判断,本技术适用于比较复杂的待处理数据,例如复杂的图像数据,使得数据处理模型的计算与推理任务能够高效完成,提高数据处理结果的准确性。

109.本技术实施例中提供了一种可能的实现方式,上述步骤s202中的对预处理数据进行矢量运算,生成合并数据,包括:

110.在一些实施方式中,可以先基于预处理数据的数据量判断是否对预处理数据进行拆分;当数据量小于预设阈值,则直接对预处理数据进行矢量运算;当数据量不小于预设阈值,则将预处理数据进行拆分处理,具体的处理方式如下:

111.(1)基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据。

112.其中,第二处理器的内部存储可以包括多层级的存储空间,该存储空间可以与隐含层中的各计算单元相适配,以高效完成矢量运算。

113.具体的,用于进行数据处理的集成芯片,可以基于第二处理器将预处理数据进行拆分,得到至少两个分块数据。例如,当预处理数据为4*3*2*2的向量,生成的分块数据可以是四个1*3*2*2的向量。

114.(2)针对分块数据进行矢量运算,生成合并数据。

115.具体的,用于进行数据处理的集成芯片,可以通过第二处理器分别对至少两个分块数据进行卷积运算,并基于卷积计算结果生成合并数据。

116.本技术实施例中提供了一种可能的实现方式,上述隐含层对应存在至少两条处理链路;当预处理数据没有进行拆分处理,则基于任一条处理链路进行矢量运算;当预处理数据进行了拆分处理,则每一分块数据对应一处理链路进行矢量运算,具体的运算方式如下:

117.针对分块数据进行矢量运算,生成合并数据,包括:

118.a、基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据。

119.其中,至少两条处理链路是并行的,可以同时对各分块数据进行矢量运算。

120.在一些实施方式中,用于进行数据处理的集成芯片,可以采用第二处理器基于分块数据的数量,将分块数据与各处理链路进行匹配。

121.在另一些实施方式中,用于进行数据处理的集成芯片,可以采用第二处理器基于分块数据的大小,将分块数据与各处理链路进行匹配。

122.b、将至少两个中间数据进行合并处理,得到合并数据。

123.其中,每一分块数据对应一中间数据。

124.具体的,用于进行数据处理的集成芯片,可以采用第二处理器将所有中间数据进行合并处理,生成合并数据。

125.在本技术实施例中,通过将每一分块数据分配给多条处理链路,实现了各分块数据的并行处理;同时,分块数据是基于第二处理器的内存层级拆分得到的,本技术基于第二处理器的内存层级优化了数据的处理链路,进一步提升了数据处理模型的运算效率。

126.本技术实施例中提供了一种可能的实现方式,上述每一处理链路包括至少两个计算单元;基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据之前,还包括:

127.基于内存层级为每一计算单元匹配目标存储空间;目标存储空间用于存放计算单元的输出数据。

128.具体的,当数据处理模型是卷积神经网络,其计算单元可以为卷积层、激活层或池化层等;如图3所示,为数据处理模型为卷积神经网络时的数据处理链路。当数据处理模型是循环神经网络时,其计算单元可以为循环单元。

129.在本技术实施例中,以数据处理模型为卷积神经网络为例进行说明,当处理链路包括卷积层、激活层和池化层这三个计算单元,卷积层和激活层对应的目标存储空间可以为中间层级的存储空间,池化层对应的目标存储空间可以为低层级的存储空间;卷积层可以从低层级存储空间获取输入数据,进行卷积运算后将输出数据存储于目标存储空间即中间层级存储空间;激活层可以直接从中间层级存储空间获取输入数据,经激活函数处理后,将输出数据存储于激活层对应的目标存储空间即中间层级存储空间。

130.在本技术中,由于隐含层的数据处理存在多次大量的计算,将计算单元的输出数据存放入不同层级的目标存储空间可以节省数据传输和搬运的资源消耗,有效提高数据处理模型的运算效率。

131.本技术实施例中提供了一种可能的实现方式,上述目标存储空间包括第一层级存储器;

132.针对分块数据进行矢量运算,生成合并数据之前,还包括:

133.将预处理数据和分块数据均存储于第一层级存储器。

134.其中,第一层级存储器可以是低层级的存储空间,以便数据在各处理器间的快速传输。

135.在本技术实施例中,用于进行数据处理的集成芯片还可以包括dma(direct memory access,直接存储器访问)组件,该dma组件用于集成芯片中第一处理器、第二处理器和第三处理器等组件之间的数据搬移和传输。当第一处理器输出了预处理数据,集成芯片可以基于dma组件将预处理数据搬移到第二处理器的第一层级存储器中。第二处理器还包括第二层级存储器和第三层级存储器,第二处理器中数据的传输过程,将在下文中详细说明。

136.本技术实施例中提供了一种可能的实现方式,如图4所示,上述目标存储空间还包括第二层级存储器和第三层级存储器;第一层级存储器、第二层级存储器和第三层级存储器的层级依次递增;基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据,包括:

137.(1)将分块数据从第一层级存储器传输到第二层级存储器,并传输到第三级存储器。

138.具体的,用于进行数据处理的集成芯片,可以基于第二处理器将分块数据从第一层级存储空间传输到第二层级存储器。

139.其中,第一层级存储器可以是ddr sdram(double data rate sdram,双倍速率同步动态随机存储器),用于实现第二处理器与集成芯片中其他组件的数据传输。第二层级存储器可以是sram(static random-access memory,静态随机存取存储器)用于第二处理器内部的数据传递;第三层级存储器可以是glb(global buffer,全局缓存器)和spd(scratchpad,暂存器),用于第二处理器内部的数据处理。

140.(2)从第三层级存储器中读取分块数据,并基于至少两个计算单元进行计算,得到中间数据;其中,每一计算单元的输出数据和中间数据均存储于第二层级存储器。

141.在本技术实施例中,以数据处理模型为卷积神经网络为例进行说明,当处理链路包括卷积层、激活层和池化层这三个计算单元;第二处理器可以从第一层级存储器获取分块数据,并将分块数据从第一层级存储器逐级搬运到第三层级存储器中;接着调用卷积层对分块数据进行卷积运算后,将卷积层输出数据存储于第二层级存储器;第二处理器再将卷积层输出数据搬运到第三层级存储器,并调用激活层采用激活函数对卷积层输出数据进行运算,并将激活层输出数据存储于第二层级存储器中;池化层的数据处理也同上述数据传输方式,在此不再赘述。

142.本技术实施例中,将第二处理器的内存分为三个层级,第一层级存储器用于集成芯片的其他组件访问,第二层级存储器和第三层级存储器用于第二处理器的内部运算,该

内存分级方式既能方便外部的数据传输,还能适用于处理器内部的并行运算,使得第二处理器着重处理隐含层的运算算法,采用优化的内存计算能力提升数据处理模型的运行效率。

143.为了更好的理解上述数据处理方法,下面结合图5详细阐述一个本技术的数据处理方法的示例,该方法可以应用于集成芯片中,该集成芯片包括第一处理器、第二处理器和第三处理器。该方法包括如下步骤:

144.s501,基于第一处理器获取待处理数据,并调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据。

145.其中,数据处理模型可以是卷积神经网络、循环神经网络等神经网络模型,数据处理模型的计算单元包括输入层、隐含层和输出层。待处理数据可以是预设训练集中的训练数据,也可以是原始的待预测数据。

146.具体的,集成芯片可以基于第一处理器实时采集或从预设地址提取待处理数据,并调用数据处理模型的输入层对待处理数据进行图形计算,生成预处理数据。其中,图形计算可以包括数据标准化、去均值、pca(principal component analysis,主成分分析方法,一种数据降维算法)降维及白化、数据增强等数据预处理操作。

147.在本技术实施例中,第一处理器可以包括gpu,gpu调用数据处理模型的输入层对待处理数据依次进行标准化、去均值、pca降维及白化、数据增强处理,进而生成预处理数据。

148.s502,基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据;其中,该第二处理器用于调用数据处理模型的隐含层;上述隐含层对应存在至少两条处理链路;每一处理链路包括至少两个计算单元。

149.其中,上述第二处理器可以包括npu;以数据处理模型为卷积神经网络模型为例,隐含层可以包括卷积层、激活层、池化层等计算单元。

150.其中,第二处理器的内部存储可以包括多层级的存储空间,该存储空间可以与隐含层中的各计算单元相适配,以高效完成矢量运算。

151.具体的,集成芯片可以基于第二处理器将预处理数据进行拆分,得到至少两个分块数据。例如,当预处理数据为4*3*2*2的向量,生成的分块数据可以是四个1*3*2*2的向量。

152.s503,基于第二处理器的内存层级为每一计算单元匹配目标存储空间;其中,目标存储空间用于存放计算单元的输出数据;目标存储空间包括第一层级存储器、第二层级存储器和第三层级存储器;上述第一层级存储器、第二层级存储器和第三层级存储器的层级依次递增。

153.在本技术实施例中,以数据处理模型为卷积神经网络为例进行说明,当处理链路包括卷积层、激活层和池化层这三个计算单元,卷积层和激活层对应的目标存储空间可以为第二层级存储器,池化层对应的目标存储空间可以为第三层级存储器;卷积层可以从第一层级存储器获取输入数据,进行卷积运算后将输出数据存储于第二存储器;激活层可以直接从第二层级存储期获取输入数据,经激活函数处理后,将输出数据存储于激活层对应的目标存储空间即第二层级存储器。

154.s504,将预处理数据和分块数据均存储于第一层级存储器。

155.其中,第一层级存储器是低层级的存储空间,以便数据在各处理器间的快速传输。

156.在本技术实施例中,集成芯片还可以包括dma组件,该dma组件用于集成芯片中第一处理器、第二处理器和第三处理器等组件之间的数据搬移和传输。当第一处理器输出了预处理数据,集成芯片可以基于dma组件将预处理数据搬移到第二处理器的第一层级存储器中。

157.s505,将分块数据从第一层级存储器传输到第二层级存储器,并传输到第三级存储器。

158.具体的,集成芯片可以基于第二处理器将分块数据从第一层级存储空间传输到第二层级存储器。

159.其中,第一层级存储器可以是ddr sdram,用于实现第二处理器与集成芯片中其他组件的数据传输。第二层级存储器可以是sram用于第二处理器内部的数据传递;第三层级存储器可以是glb和spd,用于第二处理器内部的数据处理。

160.s506,从第三层级存储器中读取分块数据,并基于至少两个计算单元进行计算,得到中间数据;其中,每一计算单元的输出数据和中间数据均存储于第二层级存储器。

161.在本技术实施例中,以数据处理模型为卷积神经网络为例进行说明,当处理链路包括卷积层、激活层和池化层这三个计算单元;第二处理器可以从第一层级存储器获取分块数据,并将分块数据从第一层级存储器逐级搬运到第三层级存储器中;接着调用卷积层对分块数据进行卷积运算后,将卷积层输出数据存储于第二层级存储器;第二处理器再将卷积层输出数据搬运到第三层级存储器,并调用激活层采用激活函数对卷积层输出数据进行运算,并将激活层输出数据存储于第二层级存储器中;池化层的数据处理也同上述数据传输方式,在此不再赘述。

162.本技术实施例中,将第二处理器的内存分为三个层级,第一层级存储器用于集成芯片的其他组件访问,第二层级存储器和第三层级存储器用于第二处理器的内部运算,该内存分级方式既能方便外部的数据传输,还能适用于处理器内部的并行运算,使得第二处理器着重处理隐含层的运算算法,采用优化的内存计算能力提升数据处理模型的运行效率。

163.s507,将至少两个中间数据进行合并处理,得到合并数据。

164.具体的,集成芯片可以采用第二处理器将所有中间数据进行合并处理,生成合并数据。

165.在本技术实施例中,通过将每一分块数据分配给多条处理链路,实现了各分块数据的并行处理;同时,分块数据是基于第二处理器的内存层级拆分得到的,本技术基于第二处理器的内存层级优化了数据的处理链路,进一步提升了数据处理模型的运算效率。

166.s508,从第三处理器调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

167.其中,第三处理器可以包括cpu。

168.具体的,集成芯片可以基于第三处理器调用数据处理模型的输出层,输出层根据逻辑函数或归一化指数函数(softmax function)输出数据处理结果。

169.在本技术实施例中,当数据处理模型用于物体识别,数据处理结果可以为物体的中心坐标、大小或分类标签;当数据处理模型用于图像语义分割,数据处理结果可以是每一

像素点的分类结果;当数据处理模型用于语音识别,数据处理结果可以是每一个单词的分类标签。

170.本技术实施例通过第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据,接着采用第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,再通过第三处理器调用数据处理模型的输出层,对在隐含层生成的合并数据进行分类处理,进而得到数据处理模型对应的数据处理结果;本技术中数据处理模型的各数据处理层级分别与第一处理器、第二处理器和第三处理器进行了优化匹配,实现了基于多处理器的高性能的模型推理。相比现有技术中基于单独的npu来运行数据处理模型,本技术实施例充分利用了第一处理器、第二处理器和第三处理的硬件优势,提升了数据处理模型的运行效率;同时,本技术实施例预先将各处理器与各数据处理层级进行匹配,减少了各数据处理层级运行时硬件相关的逻辑判断,本技术适用于比较复杂的待处理数据,例如复杂的图像数据,使得数据处理模型的计算与推理任务能够高效完成,提高数据处理结果的准确性。

171.本技术实施例提供了一种数据处理装置,如图6所示,该数据处理装置60可以包括:获取模块601、计算模块602和分类模块603;

172.其中,获取模块601,用于获取待处理数据,从第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据;

173.计算模块602,用于从第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据;

174.分类模块603,用于从第三处理器调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

175.本技术实施例中提供了一种可能的实现方式,上述计算模块602,用于:

176.基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据;

177.针对分块数据进行矢量运算,生成合并数据。

178.本技术实施例中提供了一种可能的实现方式,上述隐含层对应存在至少两条处理链路;

179.上述计算模块602,还用于:

180.基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据;

181.将至少两个中间数据进行合并处理,得到合并数据。

182.本技术实施例中提供了一种可能的实现方式,上述每一处理链路包括至少两个计算单元;

183.上述计算模块602,还用于:

184.基于内存层级为每一计算单元匹配目标存储空间;目标存储空间用于存放计算单元的输出数据。

185.本技术实施例中提供了一种可能的实现方式,上述目标存储空间包括第一层级存储器;

186.上述计算模块602,还用于:

187.将预处理数据和分块数据均存储于第一层级存储器。

188.本技术实施例中提供了一种可能的实现方式,上述目标存储空间还包括第二层级

存储器和第三层级存储器;第一层级存储器、第二层级存储器和第三层级存储器的层级依次递增;

189.上述计算模块602,还用于:

190.将分块数据从第一层级存储器传输到第二层级存储器,并传输到第三级存储器;

191.从第三层级存储器中读取分块数据,并基于至少两个计算单元进行计算,得到中间数据;

192.其中,每一计算单元的输出数据和中间数据均存储于第二层级存储器。

193.本技术实施例的装置可执行本技术实施例所提供的方法,其实现原理相类似,本技术各实施例的装置中的各模块所执行的动作是与本技术各实施例的方法中的步骤相对应的,对于装置的各模块的详细功能描述具体可以参见前文中所示的对应方法中的描述,此处不再赘述。

194.本技术实施例通过第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据,接着采用第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,再通过第三处理器调用数据处理模型的输出层,对在隐含层生成的合并数据进行分类处理,进而得到数据处理模型对应的数据处理结果;本技术中数据处理模型的各数据处理层级分别与第一处理器、第二处理器和第三处理器进行了优化匹配,实现了基于多处理器的高性能的模型推理。相比现有技术中基于单独的npu来运行数据处理模型,本技术实施例充分利用了第一处理器、第二处理器和第三处理的硬件优势,提升了数据处理模型的运行效率;同时,本技术实施例预先将各处理器与各数据处理层级进行匹配,减少了各数据处理层级运行时硬件相关的逻辑判断,本技术适用于比较复杂的待处理数据,例如复杂的图像数据,使得数据处理模型的计算与推理任务能够高效完成,提高数据处理结果的准确性。

195.本技术实施例提供了一种集成芯片,包括第一处理器、第二处理器和第三处理器;其中,

196.第一处理器,其配置为获取待处理数据,调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据;

197.第二处理器,其配置为调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据;

198.第三处理器,其配置为调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

199.本技术实施例中提供了一种可能的实现方式,上述第二处理器,其配置为基于第二处理器的内存层级将预处理数据拆分为至少两个分块数据;针对分块数据进行矢量运算,生成合并数据。

200.本技术实施例中提供了一种可能的实现方式,上述隐含层对应存在至少两条处理链路;

201.上述第二处理器,其配置为基于至少两条处理链路分别对分块数据进行矢量运算,生成至少两个中间数据;将至少两个中间数据进行合并处理,得到合并数据。

202.本技术实施例中提供了一种可能的实现方式,每一处理链路包括至少两个计算单元;

industry standard architecture,扩展工业标准结构)总线等。总线702可以分为地址总线、数据总线、控制总线等。为便于表示,图7中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

212.存储器703可以是rom(read only memory,只读存储器)或可存储静态信息和指令的其他类型的静态存储设备,ram(random access memory,随机存取存储器)或者可存储信息和指令的其他类型的动态存储设备,也可以是eeprom(electrically erasable programmable read only memory,电可擦可编程只读存储器)、cd-rom(compact disc read only memory,只读光盘)或其他光盘存储、光碟存储(包括压缩光碟、激光碟、光碟、数字通用光碟、蓝光光碟等)、磁盘存储介质、其他磁存储设备、或者能够用于携带或存储计算机程序并能够由计算机读取的任何其他介质,在此不做限定。

213.存储器703用于存储执行本技术实施例的计算机程序,并由处理器701来控制执行。处理器701用于执行存储器703中存储的计算机程序,以实现前述方法实施例所示的步骤。

214.其中,电子设备包括但不限于:诸如移动电话、笔记本电脑、pad等等移动终端以及诸如数字tv、台式计算机等等固定终端。

215.本技术实施例提供了一种计算机可读存储介质,该计算机可读存储介质上存储有计算机程序,计算机程序被处理器执行时可实现前述方法实施例的步骤及相应内容。

216.本技术实施例提供了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机指令,该计算机指令存储在计算机可读存储介质中。计算机设备的处理器从计算机可读存储介质读取该计算机指令,处理器执行该计算机指令,使得该计算机设备执行时实现如下情况:

217.获取待处理数据,从第一处理器调用数据处理模型的输入层对待处理数据进行图形计算,得到预处理数据;

218.从第二处理器调用数据处理模型的隐含层,对预处理数据进行矢量运算,生成合并数据;

219.从第三处理器调用数据处理模型的输出层,对合并数据进行分类处理,得到数据处理结果。

220.本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”、“1”、“2”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本技术的实施例能够以除图示或文字描述以外的顺序实施。

221.应该理解的是,虽然本技术实施例的流程图中通过箭头指示各个操作步骤,但是这些步骤的实施顺序并不受限于箭头所指示的顺序。除非本文中有明确的说明,否则在本技术实施例的一些实施场景中,各流程图中的实施步骤可以按照需求以其他的顺序执行。此外,各流程图中的部分或全部步骤基于实际的实施场景,可以包括多个子步骤或者多个阶段。这些子步骤或者阶段中的部分或全部可以在同一时刻被执行,这些子步骤或者阶段中的每个子步骤或者阶段也可以分别在不同的时刻被执行。在执行时刻不同的场景下,这些子步骤或者阶段的执行顺序可以根据需求灵活配置,本技术实施例对此不限制。

222.以上所述仅是本技术部分实施场景的可选实施方式,应当指出,对于本技术领域

的普通技术人员来说,在不脱离本技术的方案技术构思的前提下,采用基于本技术技术思想的其他类似实施手段,同样属于本技术实施例的保护范畴。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。