1.本发明实施例涉及芯片制造技术领域,具体涉及一种仿真模型确定方法、芯片分类方法和相关设备。

背景技术:

2.在芯片设计中,通常采用spice(simulation program with integrated circuits emphasis,集成电路性能分析电路模拟程序)模型进行仿真,来验证芯片设计的连接和功能的完整性,并预测芯片的行为。虽然spice模型可以表征生产过程中正常的工艺波动对芯片的影响,但是,在半导体制造工艺不均匀性的影响下,晶圆不同区域的芯片的器件特性存在差异,导致采用统一的spice模型对同一晶圆上不同区域的芯片进行仿真时,并不能准确仿真芯片的性能。

技术实现要素:

3.有鉴于此,本发明实施例提供一种仿真模型确定方法、芯片分类方法和相关设备,以提高仿真模型仿真的准确度。

4.为实现上述目的,本发明实施例提供如下技术方案。

5.第一方面,本发明提供了一种仿真模型确定方法,包括:

6.获取在各工艺角条件下制作的半导体器件的测试数据,所述半导体器件包括制作有多个芯片的晶圆,所述测试数据包括所述芯片的测试数据;

7.根据所述测试数据与初始仿真模型的仿真数据的相似度,将所述半导体器件划分为至少两个区域,不同区域的芯片的测试数据与所述仿真数据的相似度不同;

8.根据所述不同区域的芯片的测试数据,确定的所述初始仿真模型的仿真参数调整值,获得与所述不同区域的芯片分别对应的最佳仿真模型,以基于所述最佳仿真模型对不同区域的芯片进行仿真。

9.第二方面,本发明提供了一种芯片分类方法,包括:

10.获取芯片内测量结构的测量数据,所述测量数据包括所述测量结构的性能参数;

11.根据所述芯片对应的最佳仿真模型,确定所述芯片的性能参数与所述测量结构的性能参数的函数关系;所述芯片的性能参数包括第一性能参数和第二性能参数;同一半导体器件上不同区域的芯片对应的最佳仿真模型不同;

12.根据所述芯片的性能参数与所述测量结构的性能参数的函数关系,确定所述第一性能参数和第二性能参数的函数关系;

13.根据所述第一性能参数的目标值以及所述第一性能参数和第二性能参数的函数关系,确定所述第二性能参数的目标值,并根据所述第二性能参数的目标值,调整所述芯片的第二性能参数;

14.根据调整后的所述芯片的性能参数的实际值,对所述芯片进行分类。

15.第三方面,本发明提供了一种仿真参数确定装置,包括:

16.第一获取单元,用于获取在各工艺角条件下制作的半导体器件的测试数据,所述半导体器件包括制作有多个芯片的晶圆,所述测试数据包括所述芯片的测试数据;

17.第一处理单元,用于根据所述测试数据与初始仿真模型的仿真数据的相似度,将所述半导体器件划分为至少两个区域,不同区域的芯片的测试数据与所述仿真数据的相似度不同;

18.第二处理单元,用于根据所述不同区域的芯片的测试数据,确定的所述初始仿真模型的仿真参数调整值,获得与所述不同区域的芯片分别对应的最佳仿真模型,以基于所述最佳仿真模型对不同区域的芯片进行仿真。

19.第四方面,本发明提供了一种芯片分类装置,包括:

20.第二获取单元,用于获取芯片内测量结构的测量数据,所述测量数据包括所述测量结构的性能参数;

21.第三处理单元,用于根据所述芯片对应的最佳仿真模型,确定所述芯片的性能参数与所述测量结构的性能参数的函数关系;所述芯片的性能参数包括第一性能参数和第二性能参数;同一半导体器件上不同区域的芯片对应的最佳仿真模型不同;

22.第四处理单元,用于根据所述芯片的性能参数与所述测量结构的性能参数的函数关系,确定所述第一性能参数和第二性能参数的函数关系;

23.第五处理单元,用于根据所述第一性能参数的目标值以及所述第一性能参数和第二性能参数的函数关系,确定所述第二性能参数的目标值,并根据所述第二性能参数的目标值,调整所述芯片的第二性能参数;

24.分类单元,用于根据调整后的所述芯片的性能参数的实际值,对所述芯片进行分类。

25.第五方面,本发明提供了一种电子设备,包括:

26.存储器,存储至少一组指令;

27.处理器,执行所述至少一组指令执行如上任一项所述的仿真参数确定方法,或者如上任一项所述的芯片分类方法。

28.第六方面,本发明提供了一种可读存储介质,所述可读存储介质存储至少一组指令,所述至少一组指令用于使执行如上任一项所述的仿真参数确定方法,或者如上任一项所述的芯片分类方法。

29.本发明实施例提供的仿真模型确定方法、芯片分类方法和相关设备,获取各工艺角条件下制作的半导体器件的测试数据之后,根据测试数据与初始仿真模型的仿真数据的相似度,将半导体器件划分为至少两个区域,不同区域的芯片的测试数据与仿真数据的相似度不同,根据不同区域的芯片的测试数据,对初始仿真模型的仿真参数进行调整,获得与不同区域的芯片分别对应的最佳仿真模型,以基于最佳仿真模型对不同区域的芯片进行仿真,从而可以提高仿真模型仿真的准确度。

附图说明

30.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据

提供的附图获得其他的附图。

31.图1为晶圆中心区域的pmos晶体管和边缘区域的pmos晶体管的电压电流特性曲线示意图;

32.图2为本发明一个实施例提供的仿真模型确定方法的流程图;

33.图3为本发明一个实施例提供的晶圆的芯片排布结构示意图;

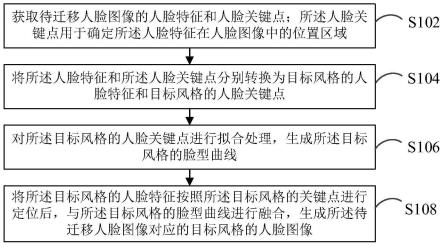

34.图4为本发明一个实施例提供的芯片分类方法的流程图;

35.图5为本发明一个实施例提供的仿真模型确定装置的结构示意图;

36.图6为本发明一个实施例提供的芯片分类装置的结构示意图。

具体实施方式

37.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

38.在芯片设计中,晶圆代工采用spice模型来表征晶圆生产过程中正常工艺波动对芯片内器件的影响。芯片设计者根据spice模型进行合理的设计,可以涵盖晶圆生产正常波动对芯片的影响。

39.但是,spice模型并不能涵盖半导体制造工艺不均匀性对芯片的影响。例如,半导体制造工艺(如fab工艺)的不均匀性,会导致晶圆中心区域和边缘区域的芯片内器件特性存在差异,进而导致晶圆中心区域和边缘区域的芯片性能存在差异。如图1所示,图1为晶圆中心区域的pmos晶体管和边缘区域的pmos晶体管的电压电流特性曲线示意图,从图中可以看出二者的电压电流特性曲线并未重合,而是存在明显差异。

40.因此,虽然采用统一的spice模型对同一晶圆上的芯片进行仿真,可以表征同一晶圆生产过程中的正常工艺波动对芯片的影响,但是,并不能准确表征半导体制造工艺不均匀性对芯片的影响,进而不能准确仿真芯片的性能。

41.基于此,本发明提供了一种仿真模型确定方案,将晶圆划分为至少两个区域,不同区域的芯片的测试数据与仿真数据的相似度不同,然后确定不同区域的芯片分别对应的最佳仿真模型,以提高不同区域的芯片的仿真模型仿真的准确度。

42.作为本发明实施例公开内容的一种可选实现,本发明实施例提供了一种仿真模型确定方法,用于确定晶圆不同区域的芯片的仿真模型,以提高各个区域的芯片的仿真准确度。如图2所示,图2为本发明一个实施例提供的仿真模型确定方法的流程图,该仿真模型确定方法包括:

43.s201:获取在各工艺角条件下制作的半导体器件的测试数据,半导体器件包括制作有多个芯片的晶圆,测试数据包括芯片的测试数据;

44.为了提高生产效率,通常都是在同一个晶圆以及相同工艺条件下制造多个芯片,形成具有多个芯片的半导体器件。其中,可以在硅晶圆上制作多个芯片,也可以在其他材料的半导体基板上制作多个芯片。可选地,本发明实施例中的半导体器件包括具有多个芯片的晶圆。如图3所示,图3为本发明一个实施例提供的晶圆上芯片排布结构示意图,晶圆上具有阵列排布的多个芯片31。

45.在晶圆上制造芯片31之前,都会设计晶圆工艺角(corner)分片条件,然后交由晶圆代工厂流片生产。需要说明的是,为减轻设计难度,工艺工程师们需要保证生产出芯片内的半导体器件的性能维持在某一性能范围内,以通过报废超出该性能范围的芯片来控制参数变化。该性能范围以通常工艺角的形式给出,通常工艺角包括ff、ss、fs、sf和tt,其中,速度快的nmos晶体管和速度快的pmos晶体管为ff;速度快的nmos晶体管和速度慢的pmos晶体管为fs;速度慢的nmos晶体管和速度快的pmos晶体管为sf;速度慢的nmos晶体管和速度慢的pmos晶体管为ss,tt为位于上述四个工艺角(即四个工艺临界点)几何中心的工艺角,通常根据前述5个工艺角所共同确定的四边形区域表示可接受的晶片。

46.晶圆出厂后,可以利用ate(automatic test equipment,集成电路自动测试)测试程序,获取晶圆各工艺角上的芯片的测试数据,该测试数据包括芯片内预设器件的特征数据,该特征数据包括特性曲线或特征参数。其中,预设器件包括晶体管,如pmos晶体管和/或nmos晶体管,特征曲线包括源漏电流ids-栅源电压vgs曲线、源漏电流ids-源漏电压vds曲线等,特征参数包括饱和区阈值电压vtsat、线性区阈值电压vtlin、等效电流ieff和漏电流ioff等。

47.s202:根据测试数据与初始仿真模型的仿真数据的相似度,将半导体器件划分为至少两个区域,不同区域的芯片的测试数据与仿真数据的相似度不同;

48.其中,初始仿真模型为spice模型,其是基于spice模拟算法的集成电路性能分析的仿真模拟程序,包含foundry工艺紧密相关的无源元件电阻,电容,电感及有源器件二极管,三极管,场效应管等多种器件模型。

49.在半导体制造工艺不均匀性的影响下,半导体器件各个区域的芯片的性能存在差异。尤其是晶圆边缘通常为不完整芯片结构,因此,无法测试得到fab工艺数据,可能会出现spice模型并不能准确表征这部分区域的器件特性,即,按照spice模型仿真,不能涵盖这部分区域的工艺特性。

50.因此,初始仿真模型是与大部分芯片匹配的仿真模型,也就是说,该初始仿真模型并不是与同一半导体器件上所有芯片都最匹配的仿真模型,并不是同一半导体器件上所有芯片的测试数据都与初始仿真模型的仿真数据相似。

51.例如,可能存在晶圆的中心区域的芯片的测试数据与初始仿真模型的仿真数据的相似度较大,晶圆边缘区域的芯片的测试数据与初始仿真模型的仿真数据的相似度较小的情况。

52.基于此,本发明实施例中,会根据测试数据与初始仿真模型的仿真数据的相似度大小,将半导体器件划分为至少两个区域,不同区域的芯片的测试数据与仿真数据的相似度不同。

53.在一个可选示例中,测试数据与仿真数据的相似度较小的芯片都位于晶圆的边缘区域,如图3所示,灰色的芯片为相似度较小的芯片。则可以根据这些芯片的坐标确定中心区域s1的半径,以确定中心区域s1以及边缘区域s2的大小。基于此,将基板划分为至少两个区域包括:将基板划分为中心区域s1和边缘区域s2,中心区域s1的芯片的测试数据与仿真数据的相似度大于边缘区域s2的芯片的测试数据与仿真数据的相似度。

54.需要说明的是,由于制作半导体器件的过程中,制作工艺会在各工艺角条件之间正常波动,因此,为了涵盖晶圆生产正常波动的影响,本发明实施例中,会将对各工艺角条

件下制作的半导体器件进行测试,获得各工艺角条件下制作的半导体器件的测试数据,并根据各工艺角条件下制作的半导体器件的测试数据与初始仿真模型的各工艺角条件下仿真数据的相似度,将半导体器件划分为至少两个区域。

55.在一个可选示例中,将半导体器件划分为至少两个区域包括:将半导体器件划分为中心区域和边缘区域,中心区域的芯片的测试数据与仿真数据的相似度大于边缘区域的芯片的测试数据与仿真数据的相似度。当然,本发明并不仅限于此,在另一些示例中,也可以将半导体器件划分为从内向外依次分布的三个圆环状区域,在此不再赘述。

56.在一个可选示例中,特征数据至少包括晶体管的阈值电压测量值、等效电流测量值和漏电流测量值;仿真数据至少包括晶体管的阈值电压仿真值、等效电流仿真值和漏电流仿真值。

57.基于此,确定任一工艺角条件下制作的半导体器件的测试数据与初始仿真模型的对应工艺角条件下仿真数据的相似度包括:

58.至少根据任一工艺角条件下确定的阈值电压测量值与阈值电压仿真值的相似度、等效电流测量值与等效电流仿真值的相似度以及漏电流测量值与漏电流仿真值的相似度,确定工艺角条件下制作的半导体器件的测试数据与初始仿真模型的对应工艺角条件下仿真数据的相似度。

59.其中,可以根据阈值电压测量值与阈值电压仿真值的相似度、等效电流测量值与等效电流仿真值的相似度以及漏电流测量值与漏电流仿真值的相似度之和或平均值,确定工艺角条件下制作的半导体器件的测试数据与初始仿真模型的对应工艺角条件下仿真数据的相似度。

60.203:根据不同区域的芯片的测试数据,确定的初始仿真模型的仿真参数调整值,获得与不同区域的芯片分别对应的最佳仿真模型,以基于最佳仿真模型对不同区域的芯片进行仿真。

61.将半导体器件划分为至少两个区域之后,对各个区域的芯片的测试数据进行分析,确定初始仿真模型的仿真参数调整值,然后根据各个区域的仿真参数调整值,对初始仿真模型的仿真参数进行调整,获得与各个区域的芯片分别对应的最佳仿真模型。其中,调整的仿真参数可以是迁移率修正、源漏沟道电流修正、阈值电压漂移等spice模型器件特性参数。需要说明的是,最佳仿真模型的仿真数据和对应区域的芯片的测试数据的相似度较大,如大于初始仿真模型的仿真数据与该区域的芯片的测试数据的相似度。

62.在一个可选示例中,将半导体器件划分为中心区域和边缘区域之后,可以根据中心区域的芯片的测试数据确定对应的中心最佳仿真模型,根据边缘区域的芯片的测试数据确定对应的边缘最佳仿真模型,以根据中心最佳仿真模型对中心区域的芯片进行仿真,根据边缘最佳仿真模型对边缘区域的芯片进行仿真,提高仿真模型仿真的准确度。

63.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种芯片分类方法,用于根据不同芯片对应的最佳仿真模型对芯片进行分类。如图4所示,图4为本发明一个实施例提供的芯片分类方法的流程图,该芯片分类方法包括:

64.s401:获取芯片内测量结构的测量数据,测量数据包括测量结构的性能参数;

65.在一些可选示例中,测量结构设置在芯片内部,如测量结构为芯片内部的部分关键结构,该关键结构包括处理器、i/o接口、存储器或电容等器件,或者,处理器内部各功能

模块。其中,可以通过测量关键结构之间的路径的信号获得关键结构的性能参数。并且,具体的关键结构之间的路径可以通过抽样的方式获得。此外,可以通过ate测量机台获得芯片内测量结构的测量数据,该测量数据包括测量结构的工作频率或工作温度等。

66.s402:根据芯片对应的最佳仿真模型,确定芯片的性能参数与测量结构的性能参数的函数关系;芯片的性能参数包括第一性能参数和第二性能参数;同一半导体器件上不同区域的芯片对应的最佳仿真模型不同;

67.其中,半导体器件包括制作有多个芯片的晶圆。根据芯片对应的最佳仿真模型,确定芯片的性能参数与测量结构的性能参数的函数关系包括:根据芯片对应的最佳仿真模型进行仿真,获得实际仿真数据;根据实际仿真数据以及测量数据,确定芯片的性能参数与测量结构的性能参数的函数关系。其中,芯片的性能参数包括第一性能参数和第二性能参数。

68.在一些可选示例中,第一性能参数为工作频率,第二性能参数为工作电压。当然,本发明并不仅限于,在另一些可选示例中,第一性能参数还可以为工作电压,第二性能参数还可以为工作频率。

69.在一些可选示例中,获得芯片内测量结构的性能参数如工作频率之后,可以基于芯片对应的最佳仿真模型进行仿真,获得测量结构为上述工作频率时,芯片的第一性能参数如工作频率和第二性能参数如工作电压,然后即可获得芯片的第一性能参数如工作频率与测量结构的工作频率的函数关系,以及芯片的第二性能参数如工作电压与测量结构的工作频率的函数关系。

70.由于同一半导体器件如晶圆上不同区域的芯片对应的最佳仿真模型不同,因此,在仿真之前,需先确定芯片来自于晶圆的哪个区域,然后根据晶圆的不同区域与不同最佳仿真模型之间的对应关系,确定芯片对应的最佳仿真模型。其中,晶圆区域的划分以及晶圆区域与最佳仿真模型之间的对应关系的建立参照上述仿真模型确定方法的实施例,在此不再赘述。

71.在一些可选示例中,芯片来自于晶圆的中心区域,则芯片对应的仿真模型为中心区域对应的最佳仿真模型,在另一些可选示例中,芯片来自于晶圆的边缘区域,则芯片对应的仿真模型为边缘区域对应的最佳仿真模型。

72.s403:根据芯片的性能参数与测量结构的性能参数的函数关系,确定第一性能参数和第二性能参数的函数关系;

73.在一些可选示例中,芯片的第一性能参数如工作频率与测量结构的工作频率的函数关系,以及芯片的第二性能参数如工作电压与测量结构的工作频率的函数关系,即可获得芯片的第一性能参数如工作频率与芯片的第二性能参数如工作电压的函数关系。

74.s404:根据第一性能参数的目标值以及第一性能参数和第二性能参数的函数关系,确定第二性能参数的目标值,并根据第二性能参数的目标值,调整芯片的第二性能参数;

75.为了减少芯片制造过程中工艺误差的影响,使得芯片的性能与功耗达到最佳平衡,通常调整芯片的性能参数如工作频率或者工作电压,以将工作电压调整到维持预设工作频率的最小电压,或者将工作频率调整到维持预设工作电压的最大频率。

76.在一些可选示例中,可以根据第一性能参数如工作频率的目标值以及第一性能参数如工作频率和第二性能参数如工作电压的函数关系,确定第二性能参数如工作电压的目

标值,并根据第二性能参数如工作电压的目标值,调整芯片的第二性能参数如工作电压,以将芯片的工作电压调整到维持预设工作频率的最小电压。

77.s405:根据调整后的芯片的性能参数的实际值,对芯片进行分类。

78.调整芯片的第二性能参数之后,以opn规格定义需要达到的频率要求,进行功能验证和电参数测试(如ft测试),测试得到调整后的芯片的性能参数的实际值,如工作频率的实际值,并计算出达到这些实际值时,处理器核所需的电压以及芯片的功耗。然后判断频率、电压以及功耗是否满足opn规格要求,如果满足,熔断fuse,烧录opn、芯片id等信息,如果不满足,降档opn规格进行下一轮测试。基于此,可以将芯片分成不同的opn档,从而实现芯片的分类。

79.由于本发明实施例中,采用了仿真准确度更高的最佳仿真模型,因此,芯片的分类精度更高,更有利于提高芯片的达标率。

80.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种仿真模型确定装置,如图5所示,图5为本发明一个实施例提供的仿真模型确定装置的结构示意图,该仿真模型确定装置包括:

81.第一获取单元50,用于获取在各工艺角条件下制作的半导体器件的测试数据,半导体器件包括制作有多个芯片的晶圆,测试数据包括芯片的测试数据;

82.第一处理单元51,用于根据测试数据与初始仿真模型的仿真数据的相似度,将半导体器件划分为至少两个区域,不同区域的芯片的测试数据与仿真数据的相似度不同;

83.第二处理单元52,用于根据不同区域的芯片的测试数据,确定的初始仿真模型的仿真参数调整值,获得与不同区域的芯片分别对应的最佳仿真模型,以基于最佳仿真模型对不同区域的芯片进行仿真。

84.在一些可选示例中,芯片的测试数据包括芯片内预设器件的特征数据,预设器件包括晶体管;

85.特征数据至少包括晶体管的阈值电压测量值、等效电流测量值和漏电流测量值;仿真数据至少包括晶体管的阈值电压仿真值、等效电流仿真值和漏电流仿真值。

86.在一些可选示例中,第一处理单元51根据测试数据与初始仿真模型的仿真数据的相似度,将半导体器件划分为至少两个区域包括:

87.根据各工艺角条件下制作的半导体器件的测试数据与初始仿真模型的各工艺角条件下仿真数据的相似度,将半导体器件划分为至少两个区域。

88.在一些可选示例中,第一处理单元51确定任一工艺角条件下制作的半导体器件的测试数据与初始仿真模型的对应工艺角条件下仿真数据的相似度包括:

89.至少根据任一工艺角条件下确定的阈值电压测量值与阈值电压仿真值的相似度、等效电流测量值与等效电流仿真值的相似度以及漏电流测量值与漏电流仿真值的相似度,确定工艺角条件下制作的半导体器件的测试数据与初始仿真模型的对应工艺角条件下仿真数据的相似度。

90.在一些可选示例中,第一处理单元51将半导体器件划分为至少两个区域包括:

91.将半导体器件划分为中心区域和边缘区域,中心区域的芯片的测试数据与仿真数据的相似度大于边缘区域的芯片的测试数据与仿真数据的相似度。

92.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种芯片分

类装置,如图6所示,图6为本发明一个实施例提供的芯片分类装置的结构示意图,该芯片分类装置包括:

93.第获取单元60,用于获取芯片内测量结构的测量数据,测量数据包括测量结构的性能参数;

94.第三处理单元61,用于根据芯片对应的最佳仿真模型,确定芯片的性能参数与测量结构的性能参数的函数关系;芯片的性能参数包括第一性能参数和第二性能参数;同一半导体器件上不同区域的芯片对应的最佳仿真模型不同;

95.第四处理单元62,用于根据芯片的性能参数与测量结构的性能参数的函数关系,确定第一性能参数和第二性能参数的函数关系;

96.第五处理单元63,用于根据第一性能参数的目标值以及第一性能参数和第二性能参数的函数关系,确定第二性能参数的目标值,并根据第二性能参数的目标值,调整芯片的第二性能参数;

97.分类单元64,用于根据调整后的芯片的性能参数的实际值,对芯片进行分类。

98.在一些可选示例中,第三处理单元61根据芯片对应的最佳仿真模型,确定芯片的性能参数与测量结构的性能参数的函数关系包括:根据芯片对应的最佳仿真模型进行仿真,获得实际仿真数据;根据实际仿真数据以及测量数据,确定芯片的性能参数与测量结构的性能参数的函数关系。

99.在一些可选示例中,第一性能参数为工作频率,第二性能参数为工作电压。

100.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种电子设备,该电子设备包括:

101.存储器,存储至少一组指令;

102.处理器,执行至少一组指令执行如上任一实施例提供的仿真参数确定方法,或者如上任一实施例提供的芯片分类方法。

103.作为本发明实施例公开内容的另一种可选实现,本发明实施例提供了一种可读存储介质,可读存储介质存储至少一组指令,至少一组指令用于使执行如上任一实施例提供的仿真参数确定方法,或者如上任一实施例提供的芯片分类方法。

104.上文描述了本发明实施例提供的多个实施例方案,各实施例方案介绍的各可选方式可在不冲突的情况下相互结合、交叉引用,从而延伸出多种可能的实施例方案,这些均可认为是本发明实施例披露、公开的实施例方案。

105.虽然本发明实施例披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。