外设高速互连接口pcie板卡、线缆、验证系统及计算机

技术领域

1.本实用新型涉及pcie通讯技术领域,尤其涉及一种外设高速互连接口pcie板卡、线缆、验证系统及计算机。

背景技术:

2.目前,一个pcie端口最大支持的数据通路管脚数量是pcie x16,另外,还有pcie x8,pcie x4,pcie x2以及pcie x1等数据通路管脚的pcie端口。在中央处理器cpu芯片设计过程中,一般将一个pcie x16端口设计为支持x8,x4,x2以及x1的多种数据通路管脚数量的多个端口,即一个x16可以配置为一个x16端口,也可以配置为2个x8端口,或8个x2端口,或16个x1端口,或几个不同通路管脚数量宽度的多端口的组合,例如1个x8端口、1个x4端口和2个x2端口的组合。基于这种设计思路,无论是在功能验证还是在使用过程中,都需要将一个pcie x16的插槽扩展为多种pcie插槽进行使用或者验证,在现有技术中,不具备对多种端口进行灵活验证和使用的条件。

技术实现要素:

3.本实用新型提供的外设高速互连接口pcie板卡、线缆、验证系统及计算机,能够将待扩展的pcie插槽的每个数据通路管脚独立的进行传输,在验证和使用过程中,可以将待扩展的pcie插槽中的任意数量的数据通路管脚引入到对应的数据通路连接器,能够实现自由且灵活的对pcie端口进行使用或者验证。

4.第一方面,本实用新型提供一种外设高速互连接口pcie板卡,包括:

5.基板;

6.一个以上的pcie插槽,设置在基板上,每个pcie插槽具有辅助信号管脚和多个数据通路管脚;

7.一个以上的数据通路连接器组,设置在基板上,一个以上的数据通路连接器组与所述一个以上的pcie插槽一一对应设置,每个数据通路连接器组具有一个以上的数据通路连接器,所述数据通路连接器与对应的pcie插槽中至少部分数据通路管脚一一对应的通讯连接;

8.辅助信号连接器,设置在基板上,辅助信号连接器与所述pcie插槽的一个以上的pcie插槽的辅助信号管脚通讯连接。

9.可选地,还包括电源模块,设置在所述基板上;所述电源模块与所述一个以上的pcie插槽电连接,以用于向所述一个以上的pcie插槽供电。

10.可选地,所述一个以上的pcie插槽包括pcie x8、pcie x4或pcie x2中的一种或两种以上的pcie插槽。

11.可选地,与所述数据通路连接器通讯连接的数据通路管脚为靠近所述辅助信号管脚连续排列的数据通路管脚。

12.第二方面,本实用新型提供一种外设高速互连接口pcie线缆,包括:

13.pcie连接器,与待扩展的pcie插槽相适配;

14.数据通路线束,具有多根信号传输线,所述多根信号传输线与所述pcie连接器的数据通路管脚一一对应的通讯连接;

15.辅助信号线束,与所述pcie连接器的辅助信号管脚通讯连接;

16.多个数据通路连接头,与所述数据通路线束中的多根信号传输线一一对应的通讯连接;

17.辅助信号连接头,与所述辅助信号线束通讯连接。

18.可选地,所述辅助信号包括时钟信号、复位信号或系统管理总线信号中的一种或两种以上的信号。

19.第三方面,本实用新型提供一种外设高速互连接口pcie验证系统,包括:

20.如上述任意一项所述的外设高速互连接口pcie板卡;

21.如上述任意一项所述的外设高速互连接口pcie线缆;

22.所述辅助信号连接头与所述辅助信号连接器通讯连接,至少部分数据通路连接头与至少部分数据通路连接器组通讯连接,以验证与所述数据通路连接器组对应的pcie插槽。

23.可选地,还包括:

24.主板,包括待扩展的pcie插槽和中央处理器cpu基座,所述cpu基座与所述待扩展的pcie插槽通讯连接,所述pcie连接器与待扩展的pcie插槽通讯连接。

25.第四方面,本实用新型提供一种计算机,包括:

26.机箱;

27.主板,设置在所述机箱内并与所述机箱固定连接;所述主板具有待扩展的pcie插槽;

28.如上述任意一项所述的外设高速互连接口pcie板卡;

29.如上述任意一项所述的外设高速互连接口pcie线缆;

30.pcie连接器与所述待扩展的pcie插槽通讯连接,所述辅助信号连接头与所述辅助信号连接器通讯连接,至少部分所述数据通路连接头与至少部分数据通路连接器组通讯连接,以将所述待扩展的pcie插槽扩展为多个pcie插槽。

31.可选地,所述外设高速互连接口pcie板卡与所述主板间隔设置,所述外设高速互连接口pcie板卡设置在所述机箱内并与所述机箱固定连接。

32.在本实用新型提供的技术方案中,在pcie板卡上设置数据通路连接器,将数据通路连接器与pcie插槽中的数据通路管脚一一对应的通信连接,pcie线缆中的pcie连接头则用于将pcie连接器的管脚信号分为单个管脚信号引出,从而,通过任意组合的数据通路连接头组合,可以将待扩展的pcie插槽扩展为任意规格的pcie插槽,无论是在对cpu的功能验证过程中,还是在pcie插槽的使用过程中,都可以自由且灵活的对pcie插槽进行扩展和使用。

附图说明

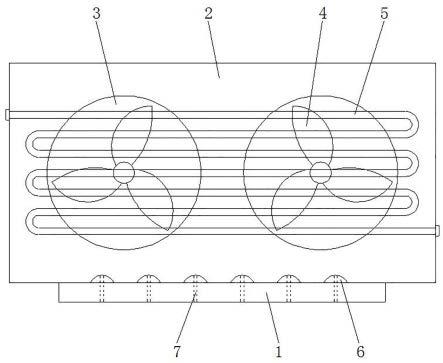

33.图1为本实用新型一实施例外设高速互连接口pcie板卡的示意图;

34.图2为本实用新型另一实施例外设高速互连接口pcie线缆的示意图。

具体实施方式

35.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

36.本实用新型实施例提供一种外设高速互连接口pcie板卡,如图1所示,包括:

37.基板;在一些实施例中,基板可以为印刷电路板制备,基板的主要作用是用于支撑插槽、数据通路连接器以及辅助信号连接器,还用于插槽与数据通路连接器之间的连线以及插槽与辅助信号连接器之间的连线。

38.一个以上的pcie插槽,设置在基板上,每个pcie插槽具有辅助信号管脚和多个数据通路管脚;在一些实施例中,pcie插槽可以选取具有任何数量的数据通路连接管脚的pcie插槽,但是,为了节省面积以及零件的资源,当待扩展的pcie插槽为x16时,可以在基板上设置x8的pcie插槽,这是由于x8的pcie插槽可以兼容x16以下的任何一种规格,便于灵活的进行扩展。

39.一个以上的数据通路连接器组,设置在基板上,一个以上的数据通路连接器组与所述一个以上的pcie插槽一一对应设置,每个数据通路连接器组具有一个以上的数据通路连接器,所述数据通路连接器与对应的pcie插槽中至少部分数据通路管脚一一对应的通讯连接;在一些实施例中,数据通路连接器是将pcie插槽中的部分数据通路管脚向外引出后再和连接器器件进行通讯连接形成的。当外部信号连接至数据通路连接器时,即能够与对应的pcie插槽中的数据通路管脚建立通讯连接。

40.辅助信号连接器,设置在基板上,辅助信号连接器与所述pcie插槽的一个以上的pcie插槽的辅助信号管脚通讯连接。辅助信号连接器是将pcie插槽中的辅助信号的管脚引出后与连接器进行连接形成的,由于多种规格的pcie插槽的辅助信号的传输都是一致的,因此,采用一个辅助信号连接器与多个pcie插槽进行连接即可。

41.在本实施例提供的技术方案中,在pcie板卡上设置数据通路连接器,将数据通路连接器与pcie插槽中的数据通路管脚一一对应的通信连接,pcie线缆中的pcie连接头则用于将pcie连接器的管脚信号分为单个管脚信号引出,从而,通过任意组合的数据通路连接头组合,可以将待扩展的pcie插槽扩展为任意规格的pcie插槽,无论是在对cpu的功能验证过程中,还是在pcie插槽的使用过程中,都可以自由且灵活的对pcie插槽进行扩展和使用。

42.作为一种可选的实施方式,还包括电源模块,设置在所述基板上;所述电源模块与所述一个以上的pcie插槽电连接,以用于向所述一个以上的pcie插槽供电。在一些实施例中,电源模块可以向多个pcie插槽供电,电源模块与外部电源进行连接,对外部电源进行变压等处理后,再向多个pcie插槽供电。

43.作为一种可选的实施方式,所述一个以上的pcie插槽包括pcie x8、pcie x4或pcie x2中的一种或两种以上的pcie插槽。在一些实施例中,可以在基板上设置8个pcie插槽,为了pcie卡安装方便,这些pcie插槽选用x8连接器,当然也可以选择其他宽度的插槽连接器。8个pcie插槽对应8个数据通路连接器组,其中4个pcie插槽对应x2的数据通路连接器组,例如每个pcie插槽连接2个高密度高速度卡缘连接器mcio母头连接器,每个mcio母头连

接器连接到对应的pcie插槽的一个数据通路管脚。其中2个pcie插槽对应x4的数据通路连接器组,每个pcie插槽连接4个mcio母头连接器,每个mcio母头连接器连接到对应的pcie插槽的一个数据通路管脚。其中2个pcie插槽对应x8的数据通路连接器组,每个pcie插槽连接8个mcio母头连接器,每个mcio母头连接器连接到对应的pcie插槽的一个数据通路管脚。上述的连接方式中,无论是x8的数据通路连接器组、x4的数据通路连接器组,还是x2的数据通路连接器组都对应的是x8的插槽。当然,也可以将x4的数据通路连接器组对应x4的插槽,将x2的数据通路连接器组对应x2的插槽。还可以将也可以将x4的数据通路连接器组对应x4的插槽,将x2的数据通路连接器组也对应x4的插槽。

44.作为一种可选的实施方式,与所述数据通路连接器通讯连接的数据通路管脚为靠近所述辅助信号管脚连续排列的数据通路管脚。在一些实施例中,由靠近辅助信号管脚的一端开始,连续选取多个数据通路管脚连接至数据通路连接器,从而,当pcie外设的pcie连接器规格小于插槽时,插入到插槽中也能够正确的使用。例如,当基板上安装的pcie插槽为x8插槽时,接入的信号为x4信号,此时,pcie外设的连接器也为x4连接器,按照本实施方式中选取管脚,才能够正确的支持pcie外设。

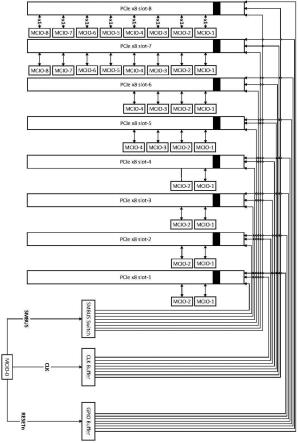

45.本实用新型实施例提供一种外设高速互连接口pcie线缆,如图2所示,包括:

46.pcie连接器,与待扩展的pcie插槽相适配;在一些实施例中,pcie连接器例如可以为pcie金手指,当pcie连接器为x16的连接器时,具有16个数据通路管脚。

47.数据通路线束,具有多根信号传输线,所述多根信号传输线与所述pcie连接器的数据通路管脚一一对应的通讯连接;在一些实施例中,信号传输线的数量通常应当与pcie连接器的数量相对应,以便于对pcie的多种规格的组合方式进行使用或者验证。但是,当使用或者验证需求较少,仅需要用到x16连接器中的部分信号时,则可以选取较少数量的信号传输线。

48.辅助信号线束,与所述pcie连接器的辅助信号管脚通讯连接;在一些实施例中,辅助信号线束是在pcie数据传输过程中,起到辅助作用的信号,例如,时钟信号、系统管理总线信号或者复位信号等。

49.多个数据通路连接头,与所述数据通路线束中的多根信号传输线一一对应的通讯连接;在一些实施例中,多个数据通路连接头分别连接在多个信号传输线上,多个数据通路连接头在物理上不会形成相互的限制,每个数据通路连接头都可以单独的连接到对应的位置。

50.辅助信号连接头,与所述辅助信号线束通讯连接。在一些实施例中,由于多种规格的pcie插槽的辅助信号的传输都是一致的,因此,采用一个辅助信号连接头即可。在使用过程中,可以将pcie板卡上的辅助信号连接器通过芯片,例如系统管理转换芯片smbus switch、时钟缓冲芯片clk buffer和通用输入输出缓冲芯片gpio buffer,将辅助信号扩展,然后再连接到多个插槽上即可。

51.在本实施例提供的技术方案中,在pcie板卡上设置数据通路连接器,将数据通路连接器与pcie插槽中的数据通路管脚一一对应的通信连接,pcie线缆中的pcie连接头则用于将pcie连接器的管脚信号分为单个管脚信号引出,从而,通过任意组合的数据通路连接头组合,可以将待扩展的pcie插槽扩展为任意规格的pcie插槽,无论是在对cpu的功能验证过程中,还是在pcie插槽的使用过程中,都可以自由且灵活的对pcie插槽进行扩展和使用。

52.作为一种可选的实施方式,所述辅助信号包括时钟信号、复位信号或系统管理总线信号中的一种或两种以上的信号。

53.在上述的各实施方式中,多个数据通路连接器和数据通路连接头可以根据支持的pcie速率选用不同类型,例如,为了支持pcie gen5,选用mcio金手指公头连接器和mcio金手指母头连接器进行连接的方式。而对于辅助信号来说,因为辅助信号对速率要求不高,可以选用其他速率较低的连接器以便降低成本,也可以选用mcio金手指连接器以提高其信号质量。

54.本实用新型实施例还提供一种外设高速互连接口pcie验证系统,包括:

55.如上述任意一项所述的外设高速互连接口pcie板卡;

56.如上述任意一项所述的外设高速互连接口pcie线缆;

57.所述辅助信号连接头与所述辅助信号连接器通讯连接,至少部分数据通路连接头与至少部分数据通路连接器组通讯连接,以验证与所述数据通路连接器组对应的pcie插槽。

58.作为一种优选的实施方式,pcie板卡上各插槽对应的数据通路连接器以及辅助信号连接其编号如图1所示,将辅助信号连接器编号为mcio-0,每个插槽对应的数据通路连接器分别以mcio-1作为起始进行编号,例如x2的数据通路连接器组中的两个数据通路连接器分别编号为mcio-1和mcio-2;x4的数据通路连接器组中的两个数据通路连接器分别编号为mcio-1、mcio-2、mcio-3和mcio-4;pcie线缆上的各数据通路连接头以及辅助信号连接头编号如图2所示,将辅助信号连接头的编号为m-mcio-0;16个数据通路连接头编号以m-mcio-1至m-mcio-16尽心该编号。

59.在测试过程中,数据通路连接头和数据通路连接器对应的连接方式如下表1所示:

[0060][0061]

按照上述表格中的连接方式,能够将x16的pcie插槽扩展为4个x2的pcie插槽和2

个x4的pcie插槽,从而测试对应插槽的功能。

[0062]

此外,还可以将16个数据通路连接器分别按顺序插入两个x8的数据通路连接器组中,以将x16的pcie插槽扩展为2个x8的pcie插槽,从而测试对应的功能。

[0063]

在本实施例提供的技术方案中,在pcie板卡上设置数据通路连接器,将数据通路连接器与pcie插槽中的数据通路管脚一一对应的通信连接,pcie线缆中的pcie连接头则用于将pcie连接器的管脚信号分为单个管脚信号引出,从而,通过任意组合的数据通路连接头组合,可以将待扩展的pcie插槽扩展为任意规格的pcie插槽,无论是在对cpu的功能验证过程中,还是在pcie插槽的使用过程中,都可以自由且灵活的对pcie插槽进行扩展和使用。

[0064]

作为一种可选的实施方式,还包括:主板,包括待扩展的pcie插槽和中央处理器cpu基座,所述cpu基座与所述待扩展的pcie插槽通讯连接,所述pcie连接器与待扩展的pcie插槽通讯连接。在一些实施例中,通过在主板上设置cpu基座和待扩展的pcie插槽,将cpu安装在cpu基座上,再通过pcie线缆将待扩展的pcie插槽扩展至pcie板卡,能够实现对cpu中的pcie信号的测试。主板为cpu和待扩展的pcie插槽提供了支撑,同时还提供了外围电源以及信号的管理功能,以保证测试过程的正常进行。

[0065]

本实用新型实施例还提供一种计算机,包括:

[0066]

机箱;

[0067]

主板,设置在所述机箱内并与所述机箱固定连接;所述主板具有待扩展的pcie插槽;

[0068]

如上述任意一项所述的外设高速互连接口pcie板卡;

[0069]

如上述任意一项所述的外设高速互连接口pcie线缆;

[0070]

pcie连接器与所述待扩展的pcie插槽通讯连接,所述辅助信号连接头与所述辅助信号连接器通讯连接,至少部分所述数据通路连接头与至少部分数据通路连接器组通讯连接,以将所述待扩展的pcie插槽扩展为多个pcie插槽。

[0071]

本实施方式中提供的计算机中,可以按照前一实施例中的连接方式,在使用过程中,也可以依据具体的需求,对数据通路连接头进行插拔和组合。从而,大大的提高了pcie插槽扩展方式的灵活性。在本实施例提供的技术方案中,在pcie板卡上设置数据通路连接器,将数据通路连接器与pcie插槽中的数据通路管脚一一对应的通信连接,pcie线缆中的pcie连接头则用于将pcie连接器的管脚信号分为单个管脚信号引出,从而,通过任意组合的数据通路连接头组合,可以将待扩展的pcie插槽扩展为任意规格的pcie插槽,无论是在对cpu的功能验证过程中,还是在pcie插槽的使用过程中,都可以自由且灵活的对pcie插槽进行扩展和使用。

[0072]

作为一种可选的实施方式,所述外设高速互连接口pcie板卡与所述主板间隔设置,所述外设高速互连接口pcie板卡设置在所述机箱内并与所述机箱固定连接。在一些实施例中,采用pcie线缆进行pcie板卡与主板之间的连接,可以将pcie板卡放置于机箱中的空闲位置,对于机箱内的空间规划灵活性大大的提高。

[0073]

以上所述,仅为本实用新型的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。